傾佳電子深度解析SiC MOSFET負壓關斷的串擾抑制機理與-5V工作電壓的技術意義——暨主流廠商關斷策略橫向對比

傾佳電子(Changer Tech)是一家專注于功率半導體和新能源汽車連接器的分銷商。主要服務于中國工業電源、電力電子設備和新能源汽車產業鏈。傾佳電子聚焦于新能源、交通電動化和數字化轉型三大方向,并提供包括IGBT、SiC MOSFET、GaN等功率半導體器件以及新能源汽車連接器。?

傾佳電子楊茜致力于推動國產SiC碳化硅模塊在電力電子應用中全面取代進口IGBT模塊,助力電力電子行業自主可控和產業升級!

傾佳電子楊茜咬住SiC碳化硅MOSFET功率器件三個必然,勇立功率半導體器件變革潮頭:

傾佳電子楊茜咬住SiC碳化硅MOSFET模塊全面取代IGBT模塊和IPM模塊的必然趨勢!

傾佳電子楊茜咬住SiC碳化硅MOSFET單管全面取代IGBT單管和大于650V的高壓硅MOSFET的必然趨勢!

傾佳電子楊茜咬住650V SiC碳化硅MOSFET單管全面取代SJ超結MOSFET和高壓GaN 器件的必然趨勢!

報告摘要

傾佳電子系統性地闡明,碳化硅(SiC)MOSFET的負壓關斷(Negative Gate Turn-off, NGT)是抑制高開關瞬態(高 $dV/dt$)下寄生導通串擾(Parasitic Turn-on Crosstalk)的決定性技術手段。然而,這一策略并非沒有代價,它在系統設計中引入了關于柵極氧化物可靠性(特別是負偏壓溫度不穩定性,NBTI)、驅動電路復雜性和體二極管損耗的深刻權衡。

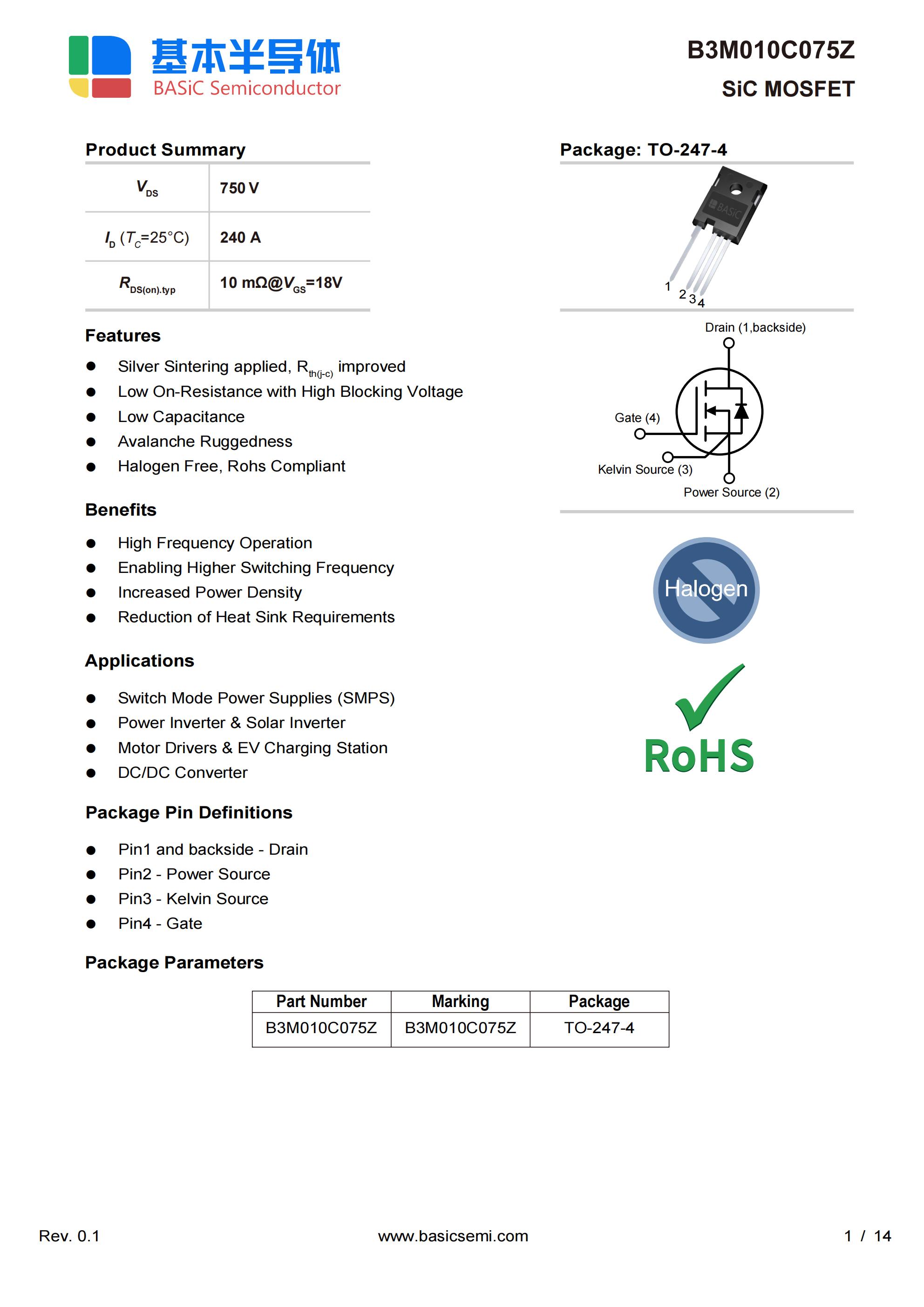

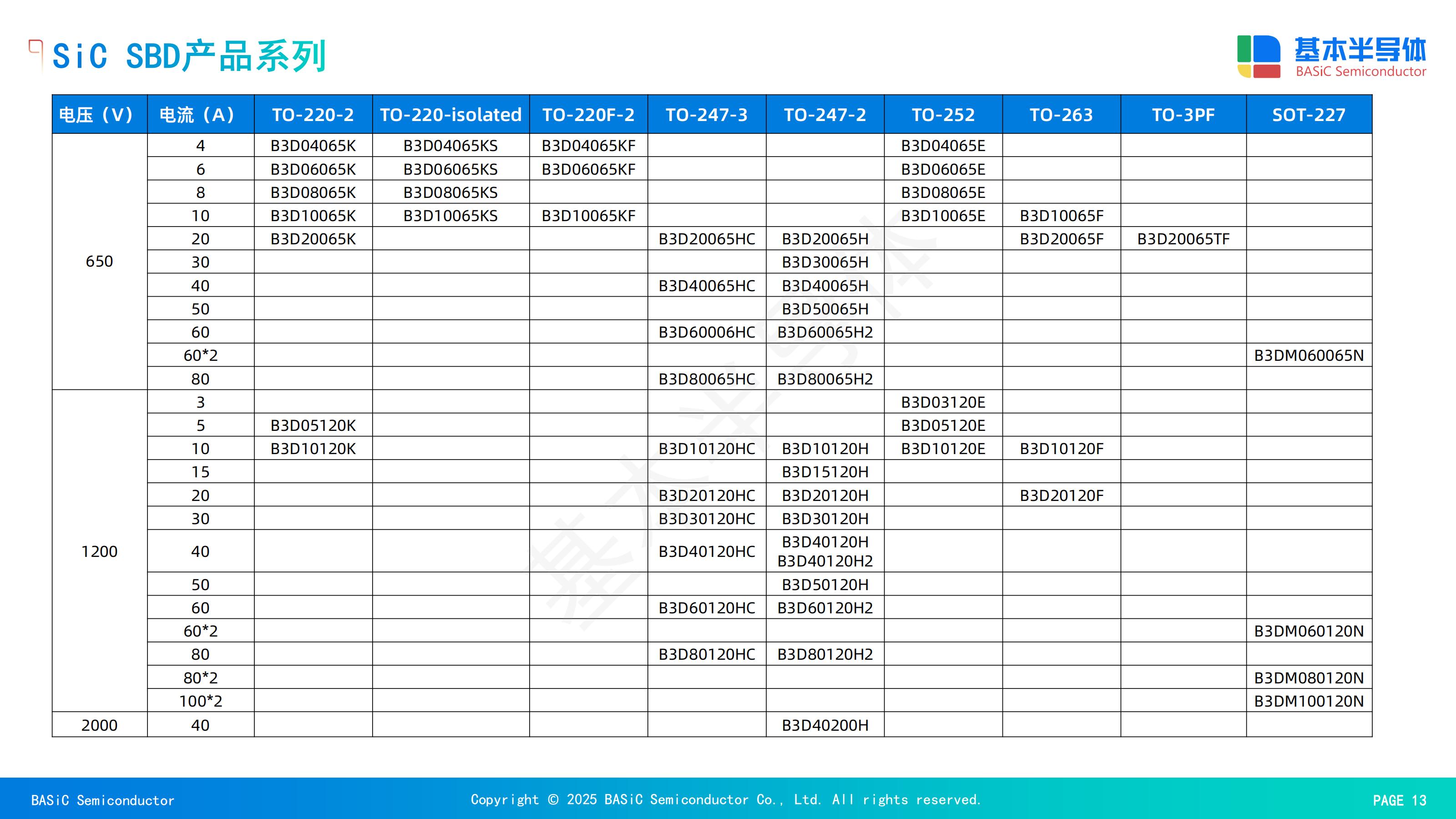

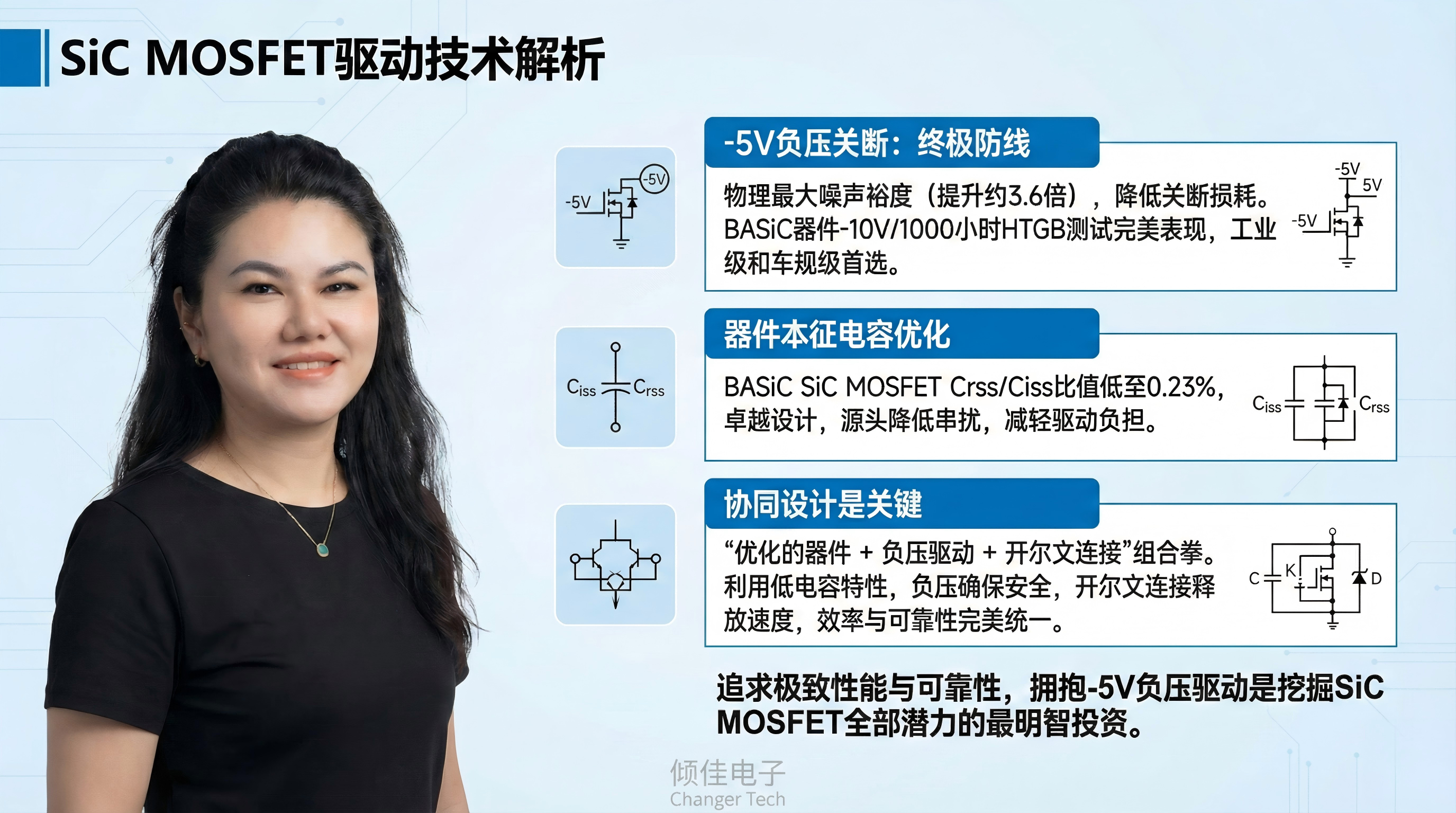

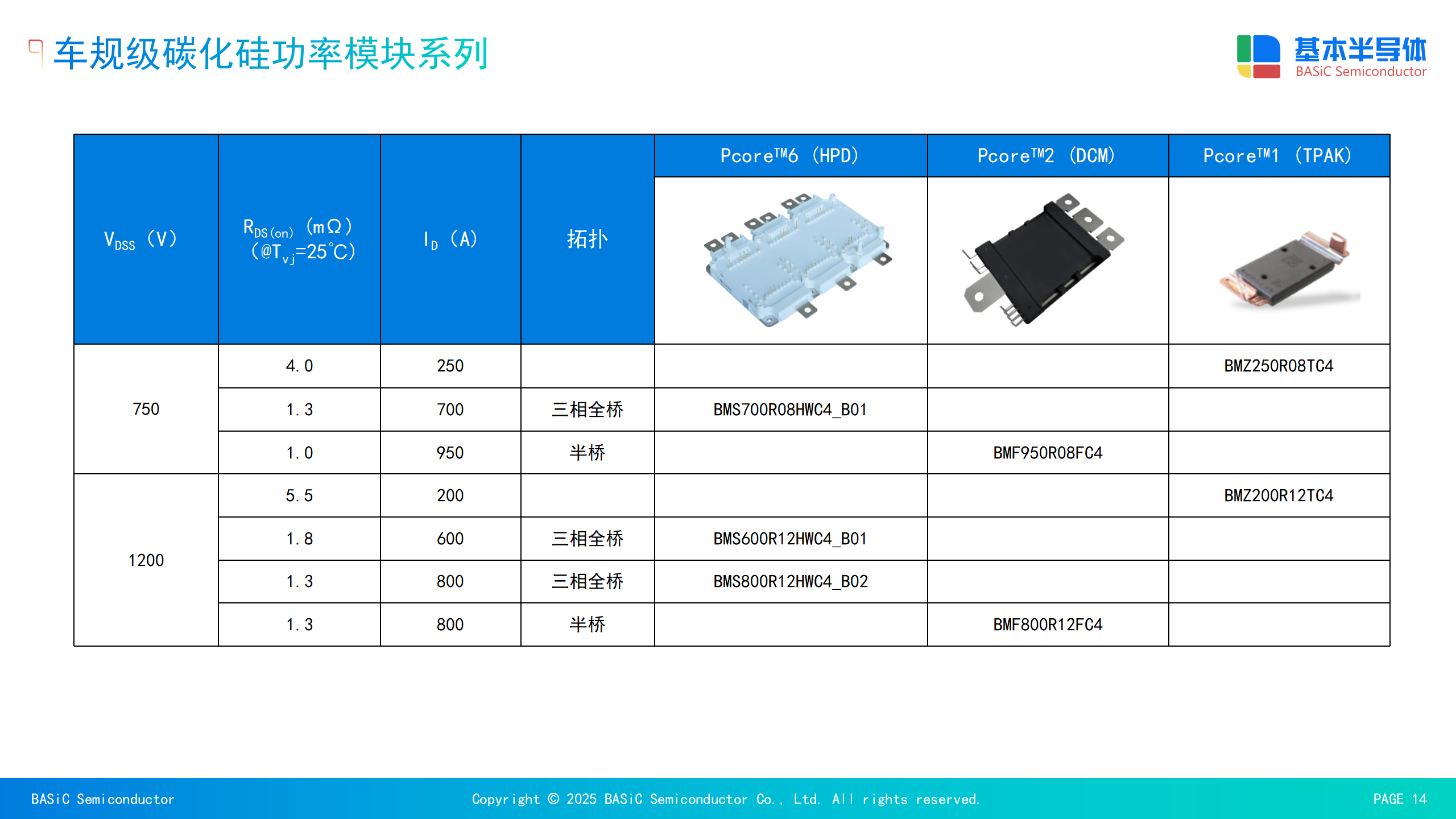

基本半導體(BASIC Semiconductor)在其第三代SiC MOSFET平臺 上,明確推薦-5V的推薦工作電壓($V_{GSop}$)。鑒于其器件約2.7V的典型柵極閾值電壓($V_{GS(th)}$),此舉是一種“穩健性優先”的戰略選擇。它旨在為系統提供絕對的串擾免疫裕量。其更深層的“技術意義”在于:這是一種對其柵氧工藝在長期-5V偏壓下,抵抗NBTI效應挑戰的可靠性自信的宣告。

傾佳電子的橫向對比將揭示,當前市場主流廠商的關斷策略以$V_{GS(th)}$為分界線,呈現出兩大陣營:

高 $V_{GS(th)}$ 陣營 (Infineon): 憑借約4.5V以上的高閾值電壓 ,正積極推動“0V關斷”的簡潔設計方案 。

中低 $V_{GS(th)}$ 陣營 (BASiC Semi, ONSEMI, STMicroelectronics): 憑借約2.3V至3.0V的閾值電壓 ,依賴-4V至-5V的負壓關斷來確保嚴苛工況下的動態可靠性。

傾佳電子將為系統架構師在器件選型、驅動設計和可靠性評估之間進行知情決策,提供關鍵的物理依據和市場數據。

第一章:SiC MOSFET高dV/dt串擾的物理根源

1.1 寄生導通的“風暴三角”:$dV/dt$、米勒電容與柵極閾值

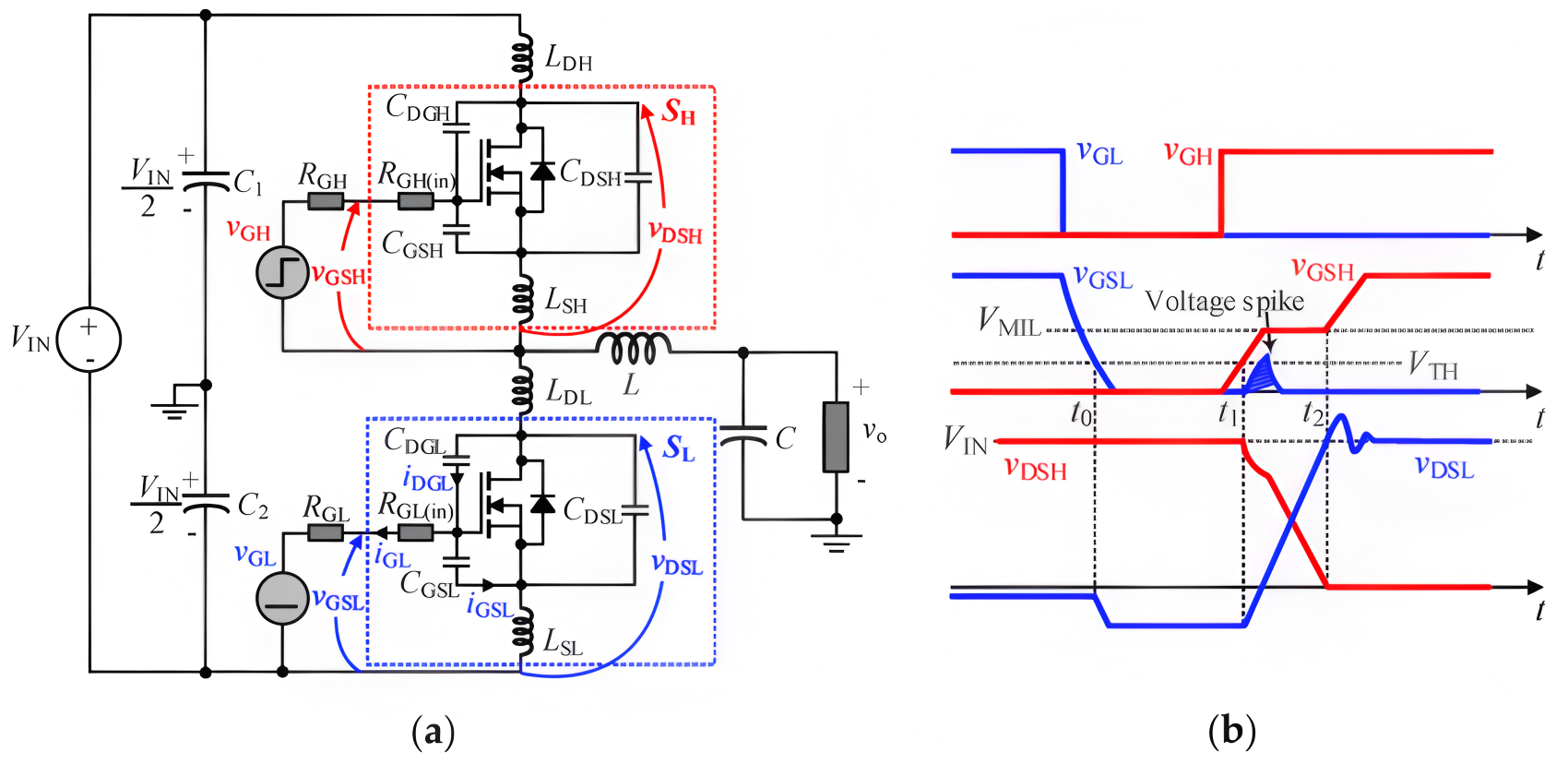

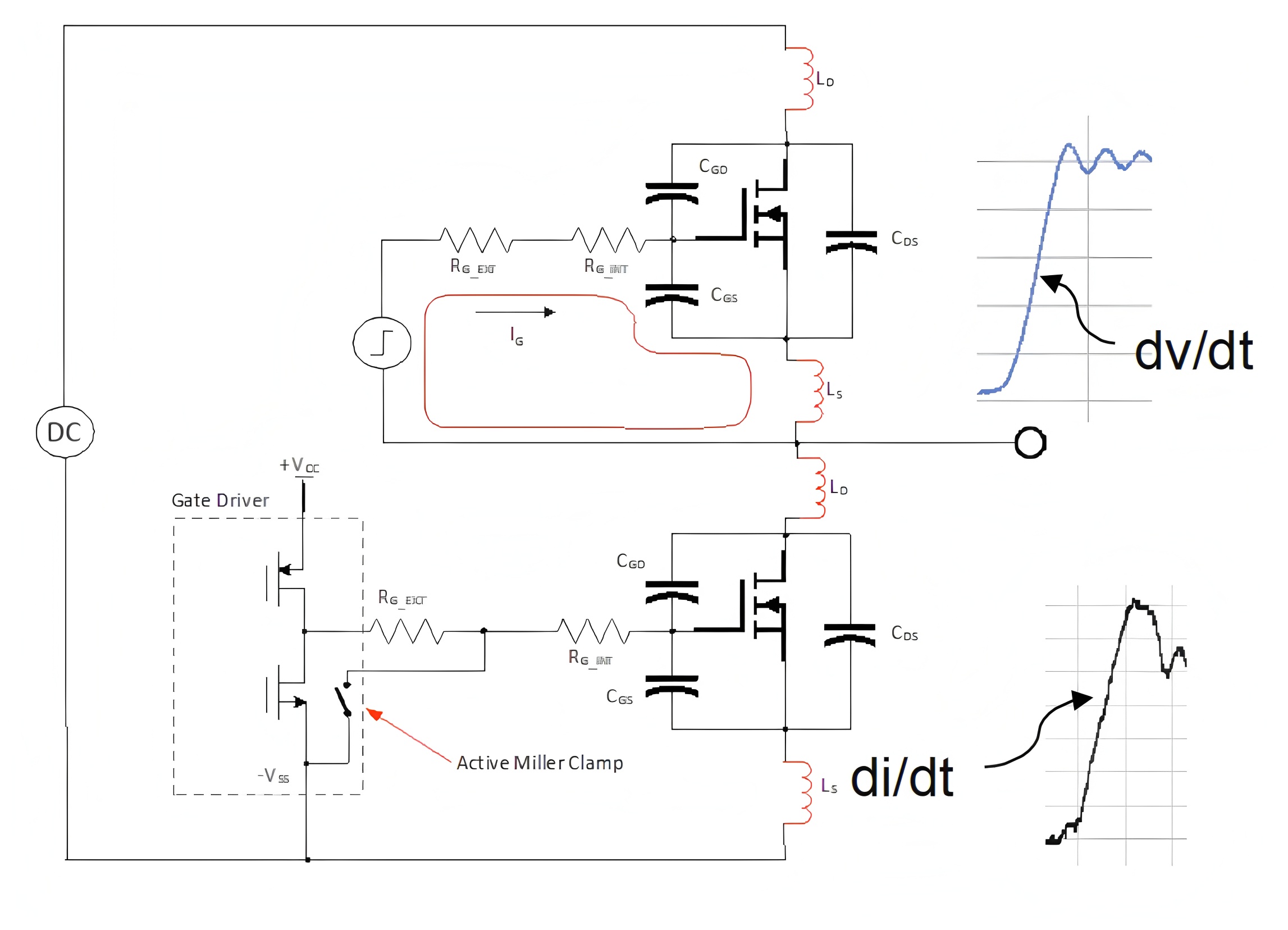

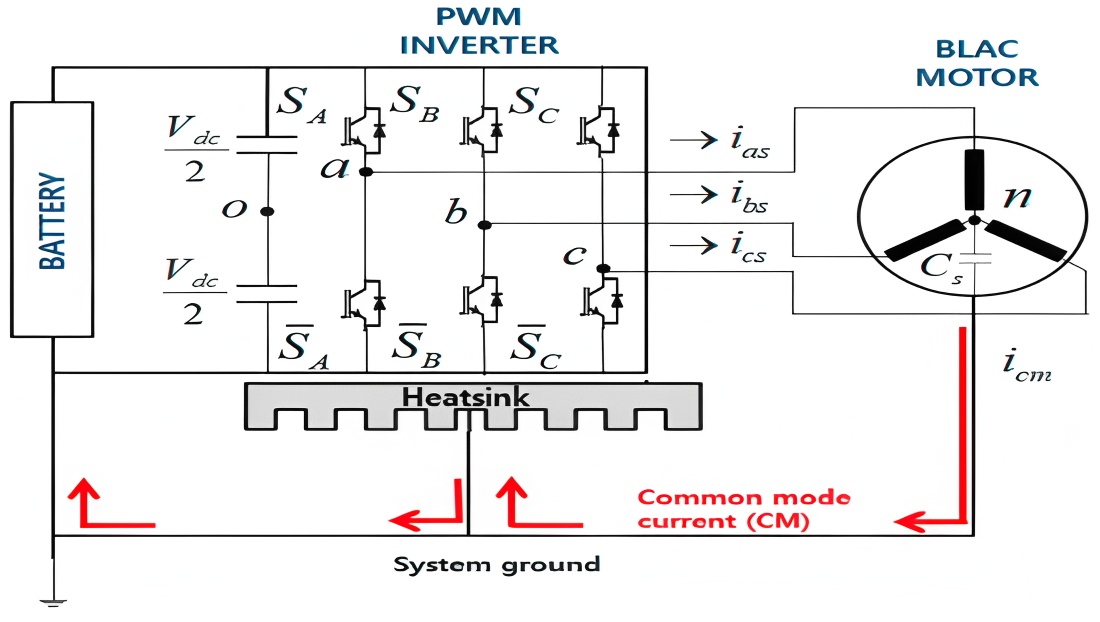

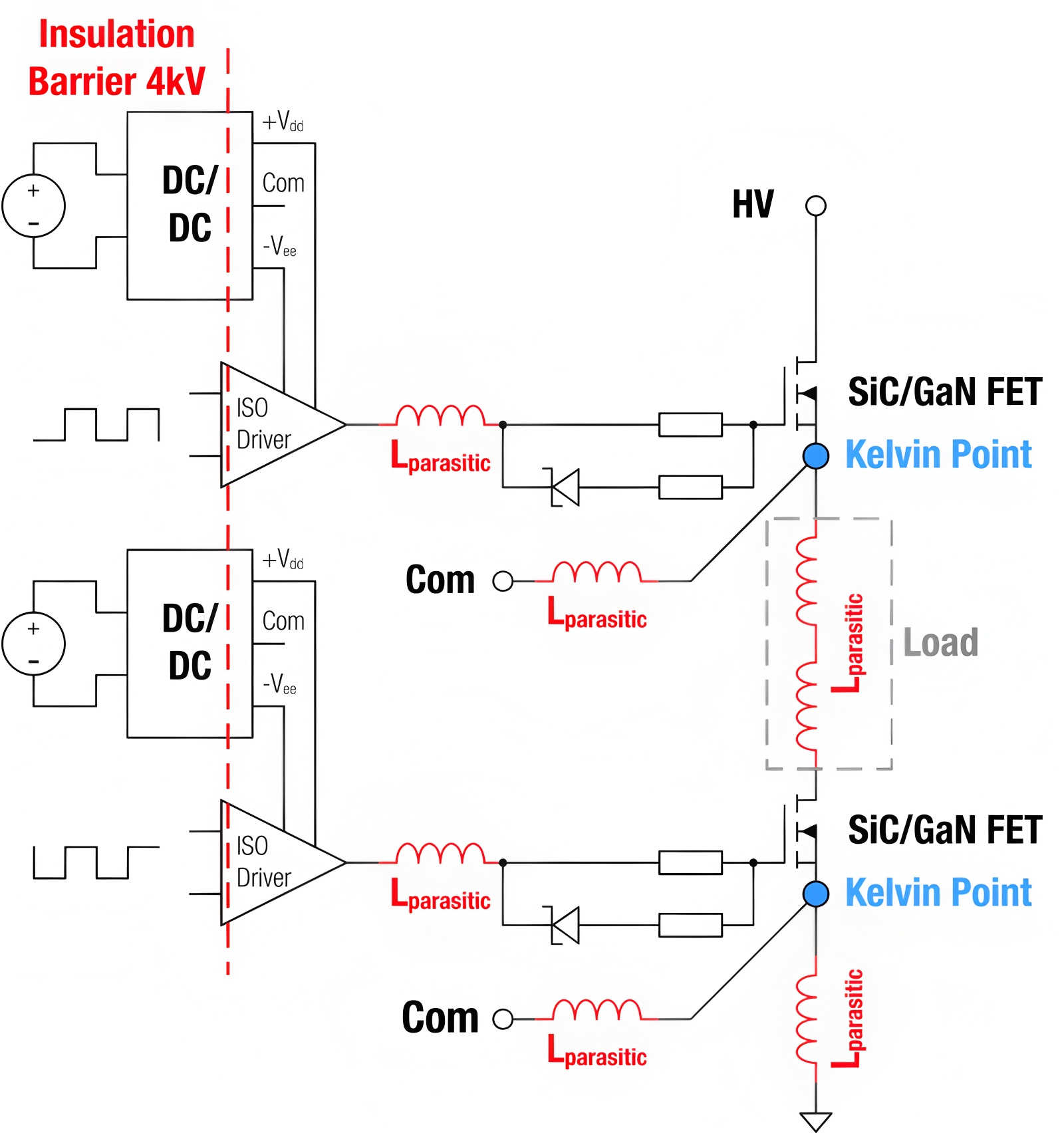

在電力電子系統中,特別是在如圖騰柱(Totem-pole)或半橋(Half-bridge)的拓撲結構中,串擾是導致系統失效的關鍵隱患 。串擾的發生,源于器件高速開關時三個物理要素的瞬態耦合。

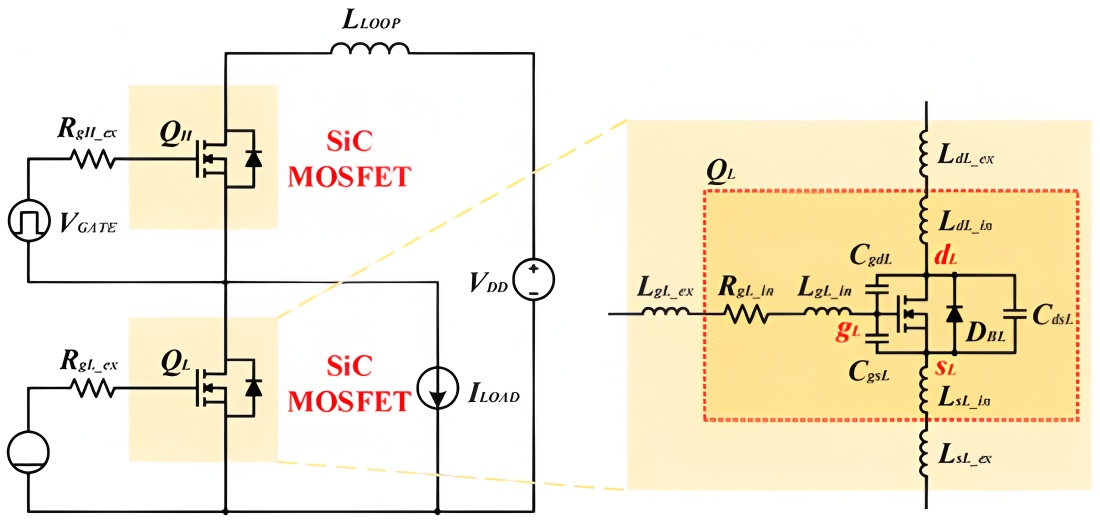

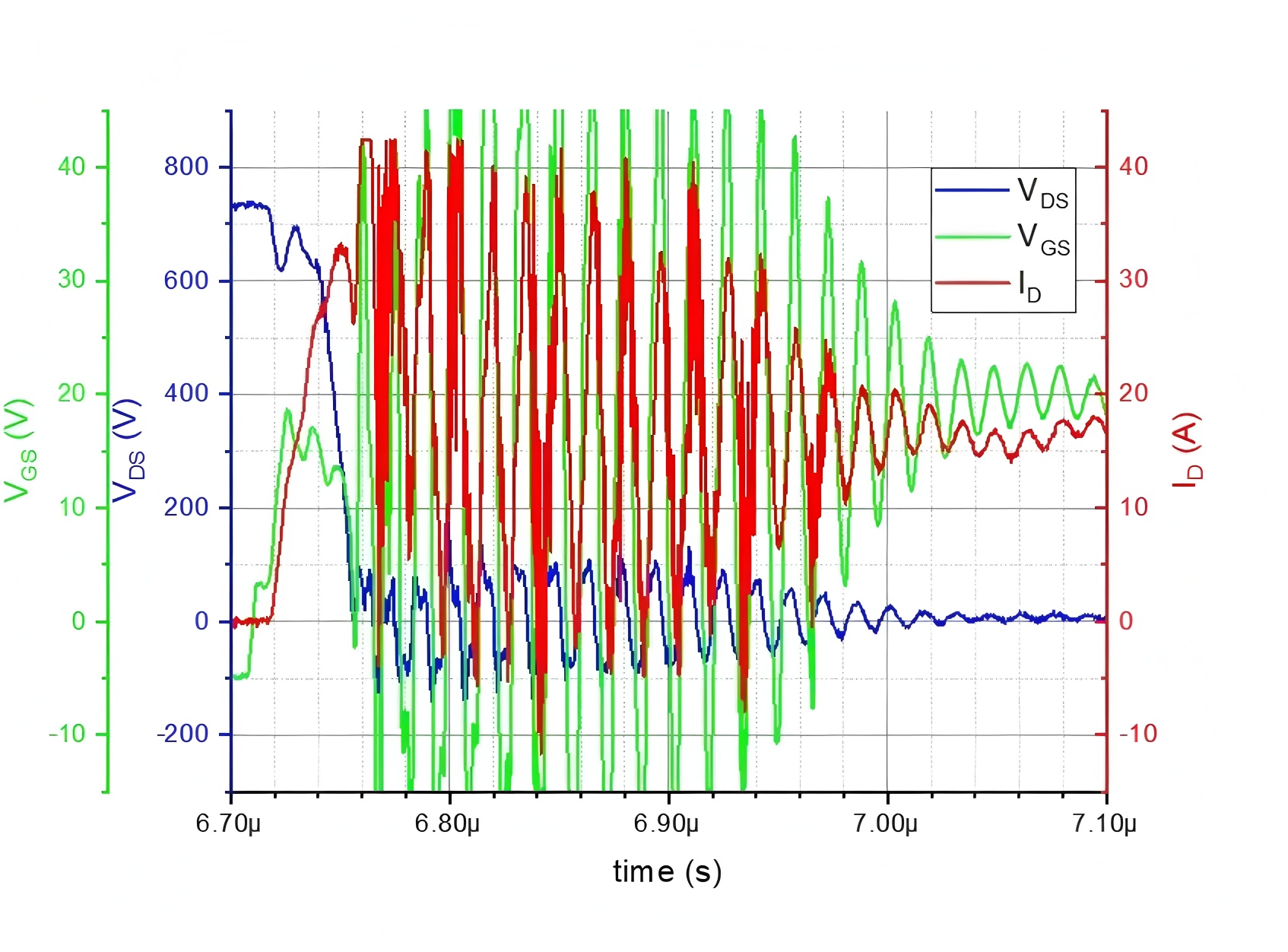

以一個典型的半橋下管(Low-Side, LS)S2為例,其寄生導通發生在對管(High-Side, HS)S1開通的瞬間 。此時,S2處于關斷狀態,但S1的開通會導致S2的漏源極電壓($V_{DS}$)經歷一次極高($dV/dt$)的電壓爬升 12。對于SiC MOSFET,由于其極快的開關速度,這個$dV/dt$值可輕易超過 50 V/ns 甚至 100 V/ns。

這個高$dV/dt$通過S2器件內部的寄生電容,特別是柵極-漏極電容($C_{gd}$),即米勒電容($C_{rss}$),耦合到柵極 。在基本半導體的B3M010C075Z(750V)和B3M013C120Z(1200V)器件手冊中,其$C_{rss}$的典型值分別為19 pF 和 14 pF 。這個瞬態電壓變化率會產生一個位移電流,即米勒電流:

$$I_{Miller} = C_{gd} times frac{dV}{dt}$$

這個電流的方向是從S2的漏極(高電位)灌入柵極(低電位)。

1.2 柵極電荷的動態競爭:米勒電流($I_{Miller}$)與柵極電阻($R_G$)的放電路徑

當$I_{Miller}$電流被注入S2的柵極節點時,它面臨兩條競爭路徑 :

充電路徑: 對柵源電容 $C_{gs}$(即輸入電容$C_{iss}$的主要組成部分)進行充電。

放電路徑: 通過柵極關斷回路(包括外部柵極電阻$R_{G,ext}$、內部柵極電阻$R_{G,int}$,以及柵極驅動器IC的下拉通道)流向源極(地)。

基本半導體的器件內部柵極電阻$R_{G(int)}$典型值分別為 1.7 $Omega$ 2 和 1.4 $Omega$ 。$I_{Miller}$在關斷回路的總電阻($R_{G,total}$)上產生一個瞬時的正向電壓尖峰($V_{GS,spike}$):

$$V_{GS,spike} approx I_{Miller} times R_{G,total}$$

如果這個$V_{GS,spike}$的峰值超過了MOSFET的柵極閾值電壓 $V_{GS(th)}$,S2將瞬間被錯誤地(寄生)導通 。這會導致上下橋臂在短時間內同時導通,形成“直通”(Shoot-through),急劇增加開關損耗,并可能導致器件永久性損壞 。

1.3 為什么SiC MOSFET比Si MOSFET更易串擾?——器件特性與開關速度的必然代價

串擾問題在SiC MOSFET應用中遠比傳統的硅(Si)IGBT或Si MOSFET中更為突出。這并非因為SiC器件“脆弱”,而是其核心性能優勢所伴隨的必然物理結果 。

SiC MOSFET的核心價值在于其極低的開關損耗和高功率密度,這使其能夠工作在比Si器件高得多的開關頻率下 。SiC實現這一優勢的關鍵在于其極低的柵極電荷($Q_G$)。低$Q_G$意味著可以用更小的驅動功率實現更快的開關瞬態 。

這種“快”直接導致了極高($dV/dt$)和($di/dt$)的產生 。根據1.1節的公式,高$dV/dt$直接導致了高$I_{Miller}$。與此同時,許多SiC MOSFET(特別是早期幾代產品)的$V_{GS(th)}$設計得相對較低,以確保在+18V驅動下能獲得足夠低的導通電阻$R_{DS(on)}$ 。

因此,SiC的“低$Q_G$”(優勢)導致了“高$dV/dt$”(目標),“高$dV/dt$”導致了“高$I_{Miller}$”(物理現實),而“低$V_{GS(th)}$”(特性)使得“高$I_{Miller}$”更容易觸發“寄生導通” 。串擾,正是SiC追求高速性能所必須應對的“B面”挑戰。

第二章:負壓關斷(NGT)對串擾的決定性抑制機理

為了應對第一章所描述的串擾風險,采用負柵極關斷電壓(NGT)成為SiC MOSFET驅動設計中的關鍵技術手段。NGT的抑制作用是決定性的,其機理體現在三個層面:

2.1 裕量倍增:負偏壓如何構建“安全護城河”

NGT最直接、最核心的作用,是極大地增加了柵極的“噪聲裕量”(Noise Margin)。噪聲裕量定義為柵極閾值電壓與柵極關斷電壓之間的差值:

$$Margin = V_{GS(th)} - V_{GS(off)}$$

以基本半導體的B3M013C120Z為例,其典型$V_{GS(th)}$為2.7V 。

在0V關斷(ZVT)方案下:

$Margin_{0V} = 2.7V - 0V = 2.7V$

在-5V關斷(NGT)方案下:

$Margin_{-5V} = 2.7V - (-5V) = 7.7V$

通過施加-5V負壓,柵極的噪聲裕量被倍增至7.7V,相較于0V關斷方案提升了285%。這意味著$I_{Miller}$所引起的$V_{GS,spike}$必須爬升一個高達7.7V的電壓門檻,才能觸發寄生導通 。在合理的電路布局(低寄生電感)和柵極電阻設計下,這幾乎是不可能的,從而從根本上“決定性地抑制”了串擾的發生。

2.2 動力學分析:-5V關斷電壓下米勒電流的瞬態響應

NGT的意義不僅在于靜態的“電壓裕量”,更在于動態的“能量吸收”機制。

在0V關斷時,$I_{Miller}$(正電流)注入柵極后,立即開始對$C_{gs}$進行正向充電,使$V_{GS}$從0V向$V_{GS(th)}$(2.7V)爬升。

在-5V關斷時,$I_{Miller}$注入柵極后,必須首先**中和**掉$C_{gs}$上存儲的負電荷(即將其柵壓從-5V“拉”回0V),然后才能**繼續**進行正向充電,使其向$V_{GS(th)}$(2.7V)爬升 。

這個-5V的“電荷空穴”或“能量緩沖區”,為柵極提供了一個吸收瞬態米勒電流能量的緩沖墊。$I_{Miller}$是一個時間極短的脈沖,其所攜帶的總電荷($Q_{Miller}$)是有限的。在-5V方案下,這股能量脈沖在還未將柵壓提升到0V之前,可能就已經結束了,$V_{GS,spike}$的峰值因此被極大削弱。

2.3 超越串擾:負壓關斷對開關損耗($E_{off}$)的潛在優化作用

除了提升可靠性,NGT還對開關性能(特別是關斷損耗$E_{off}$)有積極的優化作用 。柵極關斷速度取決于驅動器將柵極電荷($Q_G$)從柵極“抽取”出來的能力。

0V關斷: 驅動電壓擺幅(Driving Swing)為 $V_{GS(on)}$ 到 0V (例如 +18V 到 0V,擺幅18V)。

-5V關斷: 驅動電壓擺幅為 $V_{GS(on)}$ 到 -5V (例如 +18V 到 -5V,擺幅23V)。

-5V的關斷電壓提供了更大的電壓擺幅,這意味著在關斷瞬間,柵極驅動器提供了比0V關斷時更強的“負向拉力”(Pull-down Strength)。這種更強的拉力導致$Q_G$以更快的速度被抽走 ,從而縮短關斷延遲時間($t_{d(off)}$)和下降時間($t_f$)。

更快的關斷瞬態意味著漏極電壓($V_{DS}$)上升和漏極電流($I_D$)下降的交疊時間更短,這直接轉化為更低的關斷損耗($E_{off}$)。實驗數據也證實了這一點,與雙極性(-3V/18V)驅動相比,單極性(0V/18V)驅動的$E_{off}$通常更高 。因此,NGT不僅是**可靠性**(抗串擾)的需求,也是**性能**(降低$E_{off}$)的優化手段。

第三章:深度解碼:基本半導體-5V推薦工作電壓($V_{GSop}$)的戰略意義

基本半導體在其器件數據手冊中的規格定義,清晰地傳達了其設計哲學和技術定位。分析其-5V $V_{GSop}$ 的意義,必須結合其器件特性與可靠性權衡。

3.1 規格解讀:-5V作為“推薦工作電壓”而非“絕對最大額定值”的信號

在基本半導體B3M010C075Z和B3M013C120Z的數據手冊“最大額定值”(Maximum Ratings)表中,有兩個關鍵的柵壓參數 :

$V_{GSmax}$ (Gate-Source Voltage): -10V / +22V。這是器件的“絕對最大額定值”,是柵極氧化物的物理“紅線”,任何瞬態或靜態操作都不能逾越。

$V_{GSop}$ (Recommend Gate-Source Voltage): -5V / +18V。這是“推薦工作電壓”,是廠家推薦的、用于實現數據手冊中標稱性能的持續工作范圍。

將-5V寫入$V_{GSop}$,是一個極其重要的工程指令。它意味著基本半導體期望系統設計師在-5V下操作該器件。事實上,其數據手冊中所有關鍵的動態特性,如柵極電荷$Q_G$ 、開關特性($t_d(on), t_r, t_d(off), t_f$)2 和開關損耗($E_{on}, E_{off}$)2,均是在 $V_{GS}=-5V/+18V$ 的擺幅下測試和表征的。

結合其2.7V的典型$V_{GS(th)}$ ,此舉表明基本半導體認為2.7V的噪聲裕量(在0V關斷時)在高速應用中風險過高。因此,-5V的$V_{GSop}$是其實現數據手冊所承諾的低開關損耗和高動態可靠性(無串擾)的必要條件。

3.2 核心權衡(The Core Trade-off):NBTI與柵氧可靠性挑戰

然而,推薦-5V $V_{GSop}$ 是一個必須面對嚴苛可靠性挑戰的“雙刃劍”。柵極氧化物(Gate Oxide)的長期可靠性,特別是SiC/SiO2界面,是SiC MOSFET技術的核心難點 。

其中一個關鍵挑戰是負偏壓溫度不穩定性(Negative Bias Temperature Instability, NBTI)。當MOSFET柵極在高溫下(如150°C至175°C)長期承受負偏壓(如-5V)時,會導致界面陷阱的產生 4 和氧化物陷阱中的空穴俘獲 。

這些被俘獲的正電荷(空穴)會永久性地改變柵極氧化物的電場分布,其宏觀表現為MOSFET的$V_{GS(th)}$發生**負向漂移**(即$V_{GS(th)}$降低)。$V_{GS(th)}$的降低會使器件更接近導通,從而削弱抗串擾能力。

3.3 可靠性悖論:-5V負壓的“惡性循環”

這就導出了一個嚴峻的“可靠性悖論”:

問題: 器件的 $V_{GS(th)}$ 較低(例如基本半導體的2.7V ),導致串擾風險高。

解決方案: 施加-5V $V_{GS(off)}$以獲得7.7V的巨大噪聲裕量 。

長期副作用: -5V $V_{GS(off)}$在高溫下(SiC的常規工作溫度)引起NBTI效應 。

NBTI的后果: $V_{GS(th)}$發生負向漂移,例如從2.7V降低至2.0V 。

新的問題: $V_{GS(th)}$的降低,導致用于抗串擾的噪聲裕量($Margin = V_{GS(th)} - V_{GS(off)}$)也隨之降低(從7.7V降至7.0V)。

這是一個潛在的“惡性循環”:用于解決低$V_{GS(th)}$問題的-5V負壓,反過來又會隨著時間的推移而進一步降低$V_{GS(th)}$,削弱器件的長期可靠性。相關研究明確指出,-5V負壓比-3V負壓會顯著加速NBTI效應 。

3.4 技術宣言:-5V背后的工藝自信

基本半導體(作為專業的器件制造商)深刻理解3.3節中描述的NBTI風險。那么,他們為何敢于將-5V寫入“推薦工作電壓”?

答案在于其技術平臺的進步。基本半導體在其第三代SiC MOSFET技術平臺(B3M系列)的介紹中,明確提升提升可靠性” 。

因此,數據手冊上 的“-5V” $V_{GSop}$ 不僅僅是一個驅動建議,它更是一個技術宣言。它在向市場宣告:基本半導體的“第三代技術平臺”及其“優化的工藝” ,已經具備了足以承受-5V長期NBTI應力的工藝水平和可靠性。

基本半導體自信其器件在推薦的-5V關斷電壓下,通過嚴苛的高溫柵極偏壓(HTGB)可靠性測試(例如,在-10V $V_{GSmax}$ 和175°C下,或在-5V $V_{GSop}$ 和175°C下,持續1000小時),$V_{GS(th)}$的漂移被控制在極其微小和可接受的范圍內,不會導致器件的長期失效。

第四章:主流SiC MOSFET廠商柵極關斷電壓策略橫向對比

對主流SiC MOSFET制造商的關斷策略進行橫向對比,可以發現一個清晰的“分水嶺”:器件的 $V_{GS(th)}$ 設計,直接決定了其推薦的 $V_{GS(off)}$ 策略。

4.1 零電壓關斷(0V-ZVT)陣營:技術演進的趨勢(高 $V_{GS(th)}$)

這一陣營的廠商通過器件結構和工藝的革新,大幅提高了$V_{GS(th)}$,使其具備了使用0V關斷的底氣,旨在簡化系統設計。

4.1.1 Infineon (英飛凌) (CoolSiC G2)

$V_{GS(th)}$: 典型值 4.5V (例如IMDQ75R016M2H, @25°C)。這是一個非常高的值,提供了天然的抗串擾能力。

$V_{GS(off)}$ 策略: 明確推薦0V關斷 。英飛凌在其應用筆記中強調,其高$V_{GS(th)}$設計使其“完全免疫寄生導通”,使用0V關斷可簡化驅動電路、降低成本 。

策略分析: 盡管英飛凌推薦0V,但其G2器件的數據手冊卻將靜態$V_{GS}$范圍擴大到 -7V / +23V 。這是一個高明的市場兼容策略。它在傳達:“我們的器件足夠好,0V就行 ;但如果您的系統(為了兼容其他需要負壓的廠商)已經設計了-5V驅動,我們的器件也能完美承受(-7V靜態耐受),您可以無縫替換。”

4.2 傳統負壓(NGT)陣營:基于閾值電壓的現實選擇(中低 $V_{GS(th)}$)

這一陣營的廠商$V_{GS(th)}$處于中低水平,因此依賴NGT作為確保動態可靠性的標準實踐。

4.2.1 onsemi (安森美) (EliteSiC M3S)

$V_{GS(th)}$: 典型值 4.0V (例如NTHL032N065M3S) 。這是一個中高水平。

$V_{GS(off)}$ 策略: 推薦 $V_{GSop}$ (Recommended Operating Conditions) 為 -5V...-3V 。其開關損耗數據也均在-3V 或-3V/-5V 38 條件下測得。

策略分析: onsemi的4.0V $V_{GS(th)}$ 37 理論上比ST和Wolfspeed更有條件實現0V關斷。但onsemi 仍推薦-3V至-5V ,這表明其設計哲學極為保守和穩健。他們不愿在噪聲裕量上妥協,寧愿犧牲驅動的簡潔性,也要確保在最惡劣的工況下器件依然絕對可靠。

4.2.3 STMicroelectronics (意法半導體) (Gen 3)

$V_{GS(th)}$: 典型值 3.0V (例如SCT070W120G3-4) 。

$V_{GS(off)}$ 策略: $V_{GS}$ 推薦工作值為 -5V to +18V 。其應用筆記 明確指出,負壓(-2V至-5V)是“最佳權衡”(best trade-off),用于在VGS(th)和負向AMR(絕對最大額定值)尖峰之間提供安全裕量 。

策略分析: ST的策略與基本半導體類似,其3.0V的$V_{GS(th)}$不足以(像Infineon那樣)自信地推薦0V關斷,因此負壓是確保裕量的標準實踐。

4.3 關鍵數據對比矩陣

下表總結了上述分析,直觀地展示了$V_{GS(th)}$與$V_{GS(off)}$策略之間的強關聯性。

表1:主流SiC MOSFET廠商關斷電壓 ($V_{GS(off)}$) 與柵極閾值電壓 ($V_{GS(th)}$) 對比

| 廠商 (Manufacturer) | 產品世代 (Generation) | 典型 VGS(th)? (@25°C) | 推薦 VGS(off)? | 關鍵技術策略與數據來源 |

|---|---|---|---|---|

| 基本半導體 (BASIC Semi) | Gen 3 | 2.7 V (B3M013C120Z) | -5 V (VGSop) | 穩健性優先: 中低$V_{GS(th)}$,依賴-5V確保裕量。隱含對工藝抗NBTI的自信。 |

| Infineon (英飛凌) | CoolSiC G2 | 4.5 V (IMDQ75R016M2H) | 0 V (推薦) / -7V (兼容) | 性能與兼容并重: 高$V_{GS(th)}$ 支持0V ;-7V靜態能力 確保對負壓系統的“多源兼容性”。 |

| onsemi (安森美) | EliteSiC M3S | 4.0 V (NTHL032N065M3S) | -3 V to -5 V (VGSop) | 保守穩健派: 盡管$V_{GS(th)}$較高 ,仍推薦負壓以保留最大設計裕量 。 |

| STMicroelectronics | Gen 3 | 3.0 V (SCT070W120G3-4) | -2 V to -5 V | 平衡權衡: 中低$V_{GS(th)}$ ,推薦-5V工作 9,視-2V至-5V為可靠性的“最佳權衡點” 。 |

| Wolfspeed | C3M (Gen 3) | 2.3 V (C3M0015065D) | -4 V (VGSop) | 剛$V_{GS(th)}$ 使負壓關斷成為保證可靠性的“必須”手段 。 |

第五章:系統應用設計的戰略考量與結論

5.1 驅動設計的二元論:0V的簡潔性 vs. -5V的強健性

基于第四章的分析,SiC MOSFET的驅動策略已明顯分為兩大流派,系統設計師必須根據應用需求做出戰略選擇。

5.1.1 0V ZVT (零電壓關斷) 方案 (Infineon)

優勢: 極大簡化了柵極驅動器的電源設計 。系統設計師不再需要昂貴、復雜、占空間的雙極性(Bipolar)隔離電源(如 +/- Vcc),只需一個單極性(Unipolar)電源(如 0V/+18V)即可 。這對于成本和空間敏感的應用(如中低功率SMPS、光伏逆變器)是巨大的福音。

前提: 必須選用$V_{GS(th)}$足夠高(>4.0V)的器件,如Infineon G2 。

5.1.2 -5V NGT (負壓關斷) 方案 (BASIC Semi, Wolfspeed, ST, onsemi)

優勢:

強健性 (Robustness): 提供了無與倫比的抗串擾噪聲裕量 ,是高$dV/dt$、高雜散電感、高可靠性要求的嚴苛應用(如儲能變流器PCS,光伏逆變器、大功率工業電機)的首選。

性能 (Performance): 提供了更強的關斷拉力,可實現更低的$E_{off}$ 。

代價 (Cons):

驅動復雜性: 必須設計和實現雙極性隔離電源 ,增加了BOM成本和PCB面積。

可靠性風險: 必須信任器件制造商的柵氧工藝能終生(全壽命周期)承受-5V的NBTI應力 。

5.2 最終報告:基本半導體的市場定位與系統設計師的抉擇

5.2.1 基本半導體(-5V)的定位:面向高可靠、高應力環境的“穩健型”解決方案

基本半導體通過-5V $V_{GSop}$ 和“優化工藝” 1的組合,向市場傳遞了一個清晰的信號:我們提供的是一個以動態性能和可靠性為最高優先級的解決方案。我們不追求0V驅動的噱頭,而是通過-5V負壓確保器件在最惡劣的瞬態下(2/2的開關特性均在-5V下表征)絕對穩定,同時我們用優化的工藝向您保證,這種負壓不會損害器件的長期壽命(NBTI)。

5.2.2 Infineon(0V)的定位:面向高集成度、低成本的“革新型”解決方案

Infineon則代表了另一條技術路徑:通過器件物理的革新(高$V_{GS(th)}$)來消除系統設計的痛點(負壓驅動) 。它們的目標是降低SiC的使用門檻,使其像硅MOSFET一樣易于驅動 ,從而加速其在成本敏感型應用中的普及。

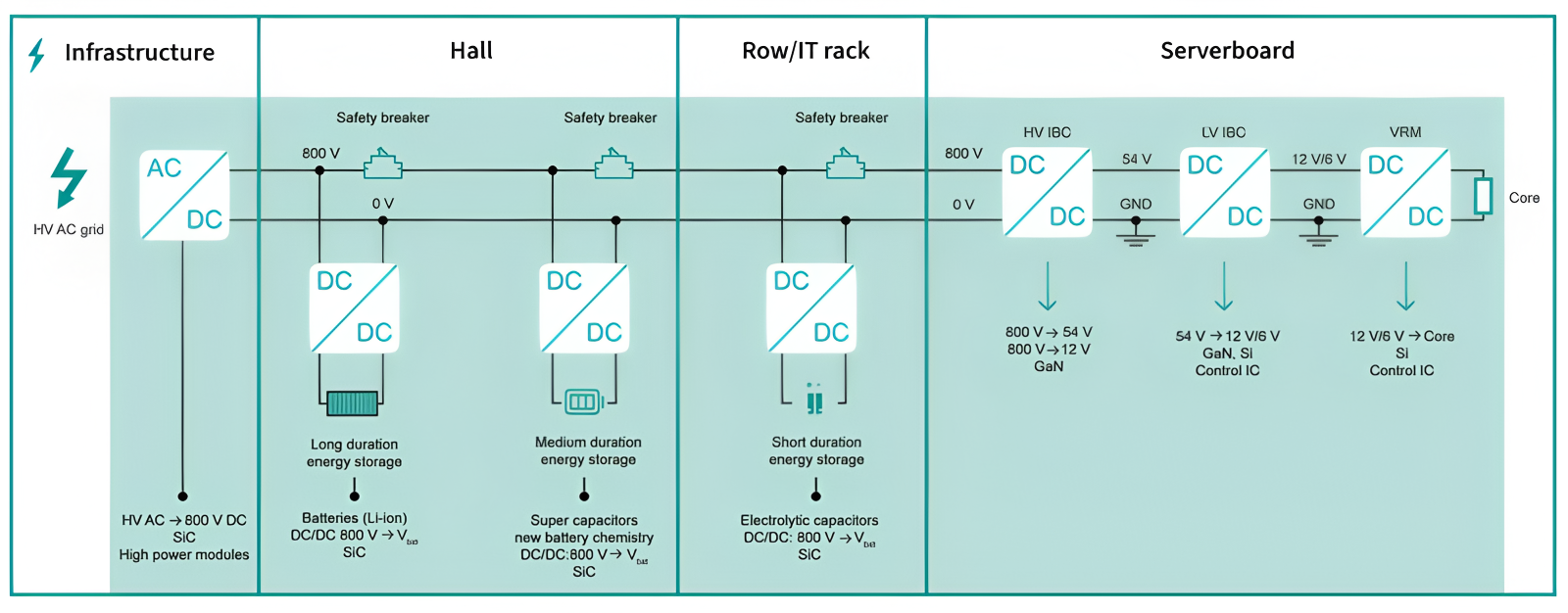

深圳市傾佳電子有限公司(簡稱“傾佳電子”)是聚焦新能源與電力電子變革的核心推動者:

傾佳電子成立于2018年,總部位于深圳福田區,定位于功率半導體與新能源汽車連接器的專業分銷商,業務聚焦三大方向:

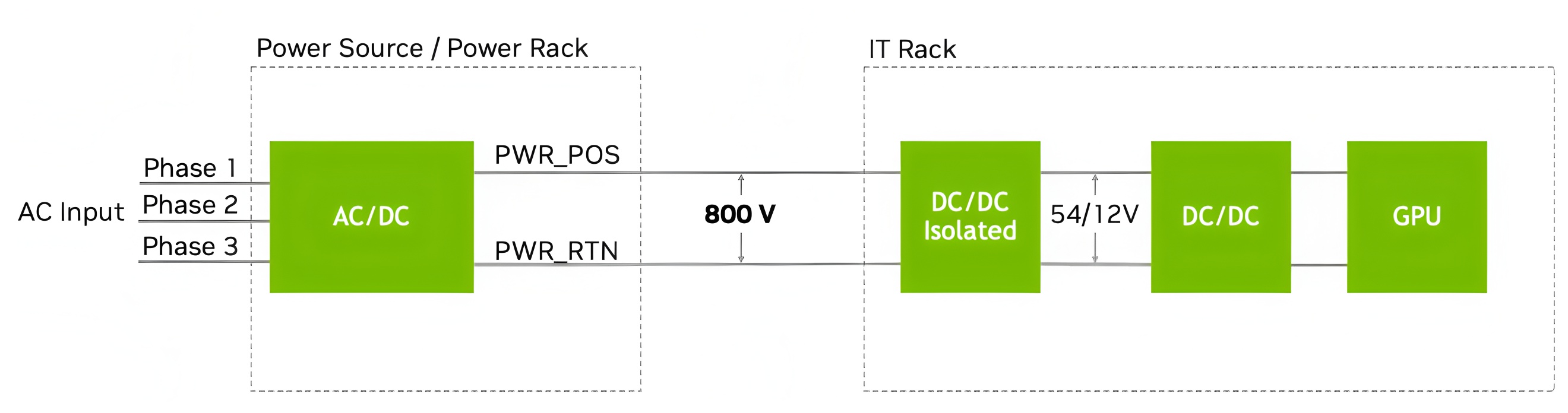

新能源:覆蓋光伏、儲能、充電基礎設施;

交通電動化:服務新能源汽車三電系統(電控、電池、電機)及高壓平臺升級;

數字化轉型:支持AI算力電源、數據中心等新型電力電子應用。

公司以“推動國產SiC替代進口、加速能源低碳轉型”為使命,響應國家“雙碳”政策(碳達峰、碳中和),致力于降低電力電子系統能耗。

需求SiC碳化硅MOSFET單管及功率模塊,配套驅動板及驅動IC,請添加傾佳電子楊茜微芯(壹叁貳 陸陸陸陸 叁叁壹叁)

5.2.3 系統設計師的最終抉擇

選擇基本半導體 (-5V): 當應用(如大功率電機驅動、儲能變流器PCS)具有極高的$dV/dt$、復雜的母線布局(高雜散電感),且可靠性是第一要素(不允許任何串擾引發的失效)時,基本半導體的-5V方案提供了一個經過廠家驗證的、強健的“交鑰匙”方案。系統必須為其配置一個-5V的驅動電源 ,并信任其NBTI可靠性 。

選擇Infineon (0V): 當應用(如高密度OBC、SMPS)對成本、體積和驅動電路的簡潔性有極致追求時 ,選用高$V_{GS(th)}$的器件并采用0V關斷,是實現更高集成度和更低系統成本的最優路徑。

結論: 負壓關斷并非過時技術,而是一種“保守”且“強效”的可靠性策略。基本半導體推薦-5V $V_{GSop}$,是其對器件$V_{GS(th)}$特性(2.7V)的誠實響應,也是對其第三代柵氧工藝平臺(抗NBTI)可靠性的自信背書。

審核編輯 黃宇

-

功率半導體

+關注

關注

23文章

1462瀏覽量

45194 -

SiC MOSFET

+關注

關注

1文章

153瀏覽量

6795 -

基本半導體

+關注

關注

2文章

112瀏覽量

11320

發布評論請先 登錄

傾佳電子深度解析SiC MOSFET負壓關斷的串擾抑制機理與-5V工作電壓的技術意義——暨主流廠商關斷策略橫向對比

傾佳電子深度解析SiC MOSFET負壓關斷的串擾抑制機理與-5V工作電壓的技術意義——暨主流廠商關斷策略橫向對比

評論