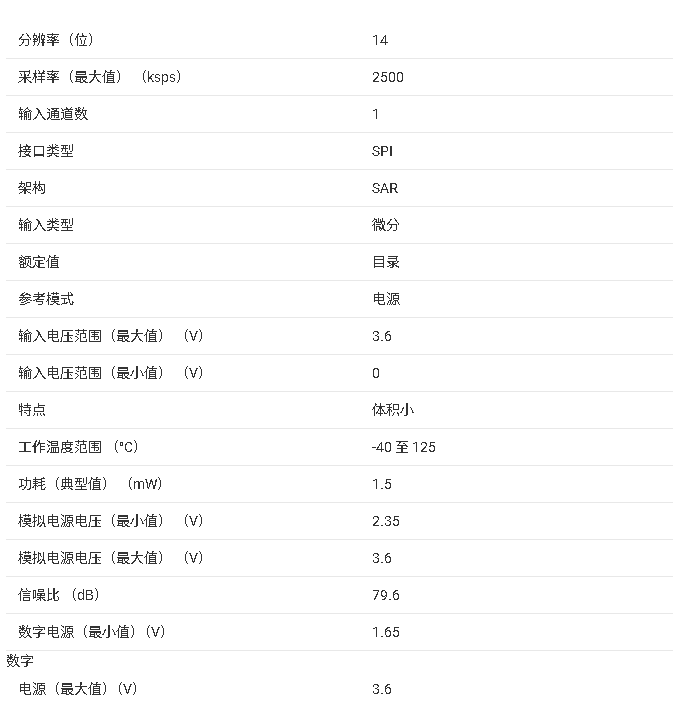

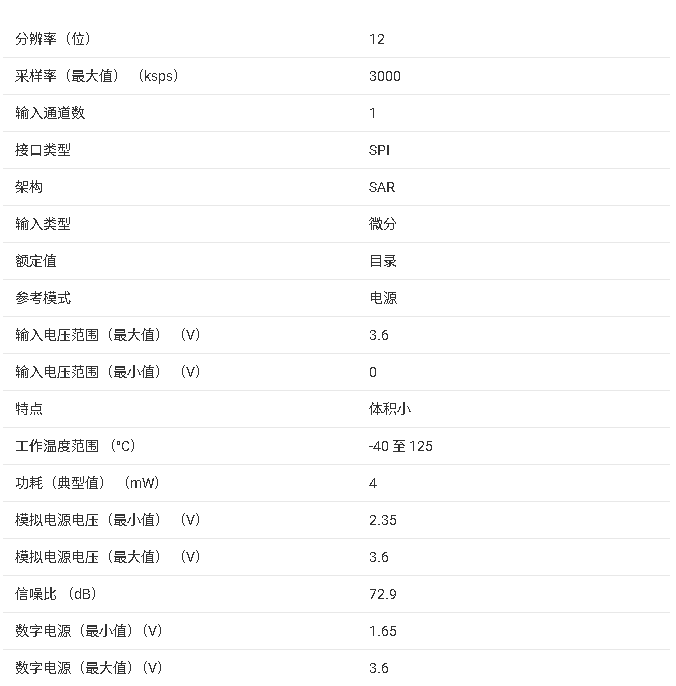

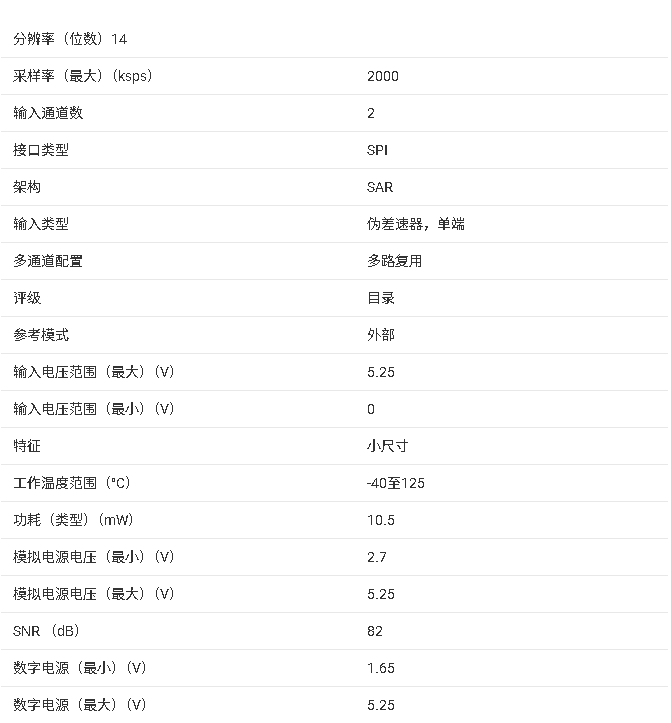

ADS7057器件屬于引腳兼容、高速、低功耗、單通道逐次逼近寄存器(SAR)型模數轉換器(ADC)系列。該器件系列包括多種分辨率、吞吐量和模擬輸入變體(器件列表見表 1)。

該ADS7057是一款14位、2.5MSPS SAR ADC,支持±AVDD范圍內的全差分輸入,適用于2.35 V至3.6 V范圍內的AVDD。

*附件:ads7057.pdf

內部失調校準功能可在整個 AVDD 和溫度工作范圍內保持出色的失調規格。

該器件支持由CS和SCLK信號控制的SPI兼容串行接口。輸入信號使用 CS 下降沿進行采樣,SCLK 用于轉換和串行數據輸出。該器件支持寬數字電源范圍(1.65 V 至 3.6 V),可直接連接到各種主機控制器。該ADS7057符合正常 DVDD 范圍(1.65 V 至 1.95 V)的 JESD8-7A 標準。

該ADS7057采用8引腳小型X2QFN封裝,額定工作范圍為擴展工業溫度范圍(–40°C至+125°C)。該器件外形小巧,功耗極低,適用于空間受限且需要高速、高分辨率數據采集的電池供電應用。

特性

- 2.5 MSPS 吞吐量

- 小包裝尺寸:

- X2QFN-8 封裝(1.5 mm × 1.5 mm)

- 全差分輸入范圍:±AVDD

- 工作范圍廣:

- AVDD:2.35 V 至 3.6 V

- DVDD:1.65 V 至 3.6 V(獨立于 AVDD)

- 溫度范圍:–40°C 至 +125°C

- 卓越的性能:

- 14 位 NMC DNL,±0.9LSB INL

- 2 kHz時為79.5 dB SINAD

- 1 MHz時為77 dB SINAD

- 低功耗:

- 3.6 mW(2.5 MSPS),3.3V AVDD

- 160 μW(100 kSPS),3.3V AVDD

- 100 kSPS 時為 82 μW,采用 2.5V AVDD

- 集成偏移校準

- SPI 兼容串行接口:60 MHz

- 符合 JESD8-7A 標準的數字 I/O

參數

方框圖

ADS7057 是一款 14 位、2.5 MSPS 高速低功耗 SAR ADC,支持全差分輸入,采用超小封裝,兼具高分辨率與低功耗特性,適用于對精度、速度和尺寸有嚴格要求的工業與通信數據采集應用。

核心參數與特性

- 性能規格 :14 位無失碼分辨率,微分非線性(DNL)±0.3 LSB,積分非線性(INL)±0.9 LSB;信號噪聲失真比(SINAD)典型值 79.3 dB(2kHz 時),無雜散動態范圍(SFDR)95 dB,全功率帶寬 200 MHz。

- 供電與功耗 :模擬供電(AVDD)2.35V-3.6V,數字供電(DVDD)1.65V-3.6V(獨立供電);2.5 MSPS 時功耗 3.6 mW(3.3V AVDD),100 kSPS 時低至 160 μW,靜態電流僅 0.02 μA。

- 輸入與參考 :全差分輸入范圍 ±AVDD,共模電壓 AVDD/2±0.1V;以 AVDD 為參考電壓,采樣電容 16 pF,輸入阻抗典型值 50 Ω。

- 接口與時序 :SPI 兼容串行接口,SCLK 最高 60 MHz;CS 下降沿觸發采樣,18 個 SCLK 完成轉換,轉換時間 18×tSCLK,采集時間 95 ns。

- 封裝與環境 :8 引腳 1.5mm×1.5mm X2QFN 超小封裝,工作溫度范圍 -40°C 至 +125°C,ESD 防護等級 HBM ±2000V、CDM ±1000V。

關鍵功能說明

- 工作模式 :支持采集(ACQ)、轉換(CNV)、偏移校準(OFFCAL)三種狀態;上電后自動進入采集狀態,CS 下降沿觸發轉換,轉換后返回采集狀態。

- 偏移校準 :內置偏移校準功能,上電時需提供 24 個 SCLK 啟動校準,正常工作時需 64 個 SCLK,校準后可補償溫漂與電源漂移帶來的誤差。

- 數據格式與傳輸 :輸出數據為二進制補碼格式,14 位數據隨 SCLK 上升沿逐位輸出,MSB 先行;CS 高電平時 SDO 引腳呈高阻態。

- 輸入特性 :模擬輸入引腳具備 ESD 保護,采樣階段開關閉合充電采樣電容,轉換階段斷開輸入以保證信號穩定,支持寬共模電壓范圍。

典型應用場景

適用于光學編碼器、聲納接收器、魚探儀、I-Q 解調器、光線路卡與模塊、熱成像相機、超聲波流量計、手持無線電等高速數據采集場景,可實現雙路同步采樣、單端信號轉差分采集等功能。

應用設計要點

- 電源與去耦 :AVDD 引腳需外接 3.3μF 低 ESR 陶瓷去耦電容,DVDD 引腳配置 1μF 電容,均靠近引腳放置,減少電源噪聲耦合。

- 布局建議 :采用獨立接地平面,分離模擬與數字信號區域;模擬輸入走線遠離數字電路與噪聲源,電荷回踢濾波器組件需貼近器件放置。

- 輸入驅動 :推薦搭配高帶寬低失真運放(如 THS4551)作為輸入驅動;差分輸入端需配置 RC 濾波器(CFLT 建議≥320 pF),平衡穩定性與失真性能。

- 校準與時序 :上電后必須完成偏移校準以保證精度;嚴格遵循時序要求,CS 下降沿至 SCLK 下降沿 setup 時間≥7 ns,SCLK 高低電平時間均不低于 0.45×tSCLK。

-

寄存器

+關注

關注

31文章

5615瀏覽量

130316 -

adc

+關注

關注

100文章

7932瀏覽量

556736 -

分辨率

+關注

關注

2文章

1128瀏覽量

43388 -

模數轉換器

+關注

關注

26文章

4096瀏覽量

130226

發布評論請先 登錄

18 位、2.5Msps、無延遲 SAR ADC可實現 99.8dB SNR 及靈活的模擬輸入范圍

ADS7041超低功耗、超小尺寸、10位、1MSPS、SAR ADC數據表

ADS7044超低功耗、超小尺寸、12位、1MSPS、SAR ADC數據表

ADS7043超低功耗、超小尺寸、12位、1MSPS、SAR ADC數據表

ADS7042超低功耗、超小尺寸、12位、1MSPS、SAR ADC數據表

ADS7042超低功耗、超小尺寸、12位、1-MSPS、SAR ADC數據表

ADS7057 14位、2.5MSPS、差分輸入、小尺寸、低功耗SAR ADC技術手冊

ADS7057 14位、2.5MSPS、差分輸入、小尺寸、低功耗SAR ADC技術手冊

評論