AFE58JD48 設備是一款高度集成的模擬前端 (AFE) 解決方案,專為高級超聲系統而設計。

AFE58JD48 是一款集成式 AFE,針對高級醫療超聲應用進行了優化。該器件通過具有三個芯片的多芯片模塊 (MCM) 實現:一個 16 通道壓控放大器 (VCA) 芯片和兩個 8 通道模數轉換器 (ADC) 芯片。

*附件:afe58jd48.pdf

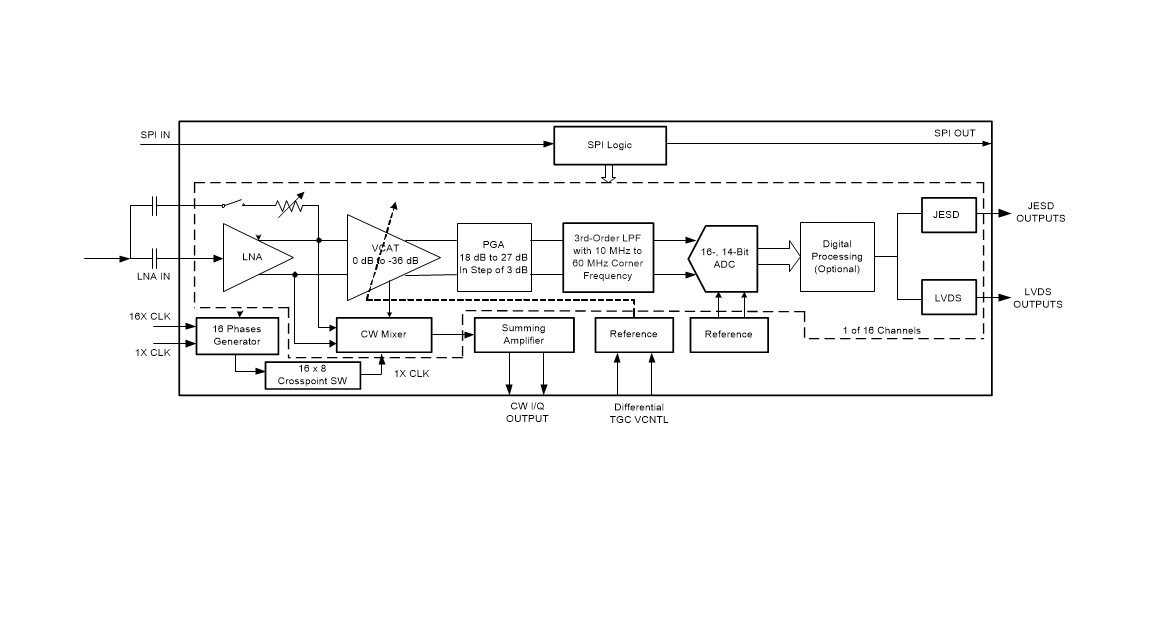

VCA芯片中的每個通道都可以配置為兩種模式之一:時間增益補償(TGC)模式或連續波(CW)模式。在TGC模式下,每個通道包括一個低噪聲放大器(LNA)、一個壓控衰減器(VCAT)、一個可編程增益放大器(PGA)和一個三階低通濾波器(LPF)。LNA可編程增益為21 dB、18 dB或15 dB。LNA 還支持主動終止。VCAT支持0 dB至36 dB的衰減范圍,并具有衰減的模擬電壓控制。PGA 提供 18 dB 至 27 dB 的增益選項,步長為 3 dB。LPF截止頻率可設置在10 MHz至60 MHz之間,以支持不同頻率的超聲應用,尤其是新興的高頻超聲成像應用。在CW模式下,LNA的輸出進入具有16個可選相位延遲的低功耗無源混頻器,然后是帶有帶通濾波器的求和放大器。可以對每個模擬輸入信號施加不同的相位延遲,以執行片內波束成形作。CW 混頻器中的諧波濾波器抑制三次和五次諧波,以提高 CW 多普勒測量的靈敏度。

ADC芯片可配置為以16位或14位的分辨率運行。該ADC主要支持運行速度高達12.8 Gbps的JESD204B接口,并降低了高通道數系統中的電路板布線挑戰。ADC的輸出接口也可以設置為低壓差分信號(LVDS),可以輕松與低成本的現場可編程門陣列(FPGA)連接。ADC可以以125 MSPS 16位的最大速度運行,并通過JESD204B接口發送數字化數據。當使用LVDS接口時,ADC的采樣率和分辨率受到1.28 Gbps的LVDS輸出速率或16位分辨率下80 MSPS的限制。在這種情況下,可以配置14位分辨率的ADC以更高的速度采樣,但仍保持相同的輸出數據速率。ADC設計用于隨采樣率縮放其功率。

該AFE58JD48還包括一個數字解調器模塊。數字同相和正交 (I/Q) 解調器具有可編程抽取濾波器,可在低功耗下加速計算密集型算法。

該器件還允許選擇各種功率和噪聲組合來優化系統性能。因此,該設備是適合由墻壁插座或電池供電的高級系統的超聲 AFE 解決方案。

特性

- 用于超聲應用的 16 通道 AFE:

- 四個可編程 TGC 設置配置文件

- 帶有源端接的低噪聲放大器 (LNA):

- 可編程增益:21 dB、18 dB 和 15 dB

- 線性輸入幅度:0.37/0.5/0.71 V

聚丙烯 - 最大輸入幅度:1 Vpp

- 壓控衰減器 (VCAT):

- 衰減范圍:0 dB–36 dB

- 可編程增益放大器 (PGA):

- 18 dB–27 dB,步長為 3 dB

- 三階、10 ~ 60 MHz 低通濾波器 (LPF)

- ADC空閑通道SNR:

- 16位、125MSPS模式:80dBFS

- 14位、80MSPS模式:79dBFS

- 出色的近場信噪比:74-dBFS

- TGC 模式JESD204B輸出

- 140 mW/通道,0.8 nV/√Hz,125 MSPS,16 位

- 120 mW/通道,0.8 nV/√Hz,80 MSPS,16 位

- 115 mW/通道,0.8 nV/√Hz,65 MSPS,16 位

- 105 mW/通道,0.8 nV/√Hz,40 MSPS,16 位

- TGC 模式 LVDS 輸出

- 120 mW/通道,0.8 nV/√Hz,80 MSPS,16 位

- 115 mW/通道,0.8 nV/√Hz,65 MSPS,16 位

- 150 mW/通道,0.8 nV/√Hz,125 MSPS,16 位,抽取 2,LVDS 0.5x 模式

- CW 模式:63 mW/Ch,1.15 nV/√Hz

- ±0.4 dB(典型值)器件間增益匹配

- 快速一致的過載恢復

- 連續波 (CW) 路徑具有:

- –159 dBc/Hz 1kHz 載波外的相位噪聲

- λ / 16 相位分辨率

- 支持 16 倍和 8 倍連續時鐘

- 12 dB 抑制 3 次和 5 次諧波

- 數字 I/Q 解調器,帶數據縮減功能

- 分數抽取濾波器 M = 1 到 63,增量為 0.25

- 片上 RAM,具有 32 個預設配置文件

- LVDS接口,速度高達1.28 Gbps

- 10 Gbps JESD204B子類 0、1 和 2

- 高達 12.8 Gbps,帶 10 cm PCB 走線

- 每個 JESD 通道 2、4 或 8 個通道

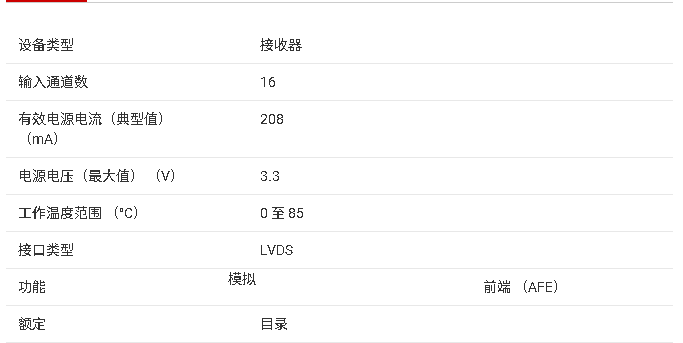

參數

方框圖

AFE58JD48 是德州儀器推出的高集成度 16 通道超聲模擬前端(AFE),專為高端超聲系統及相關成像應用設計。

核心參數與特性

- 通道與工作模式 :16 個通道,支持時間增益補償(TGC)和連續波(CW)兩種模式,TGC 模式含 4 種可編程配置文件。

- 信號鏈性能 :低噪聲放大器(LNA)增益可選 15/18/21 dB,壓控衰減器(VCAT)衰減范圍 0-36 dB,可編程增益放大器(PGA)增益 18-27 dB(3 dB 步進)。

- 濾波與 ADC :3 階低通濾波器(LPF)截止頻率 10-60 MHz;ADC 支持 16 位 / 14 位分辨率,最高采樣率 125 MSPS(16 位 JESD 模式),空閑通道 SNR 達 80-dBFS。

- 接口與功耗 :兼容 JESD204B(最高 12.8 Gbps)和 LVDS(最高 1.28 Gbps)接口;TGC 模式功耗 105-150 mW / 通道,CW 模式低至 63 mW / 通道,噪聲低至 0.8 nV/√Hz。

- 核心功能 :內置數字 I/Q 解調器、分數抽取濾波器(M=1-63,步長 0.25),CW 模式支持 16/8 倍時鐘、λ/16 相位分辨率,可抑制 3 次 / 5 次諧波。

應用場景

適用于醫療超聲成像、高頻超聲成像、無損檢測(NDT)、聲納 / 雷達 / LiDAR 成像設備及多通道數據采集系統。

封裝與訂購信息

- 采用 15mm×15mm NFBGA-289 封裝,與 AFE58JD28/18 引腳兼容。

- 量產型號為 AFE58JD48ZAV 系列,JEDEC 托盤包裝(126 片 / 盤),符合 RoHS 標準。

- 引腳鍍層為 SNAGCU,MSL 等級 3,峰值回流溫度 260°C,工作溫度 0°C 至 85°C。

-

模塊

+關注

關注

7文章

2845瀏覽量

53387 -

adc

+關注

關注

100文章

7694瀏覽量

556585 -

AFE

+關注

關注

8文章

337瀏覽量

124249 -

模數轉換器

+關注

關注

26文章

4057瀏覽量

130209 -

超聲系統

+關注

關注

1文章

46瀏覽量

11515

發布評論請先 登錄

在FPGA里面例化了8個jesd204B的ip核同步接收8塊AFE芯片的信號,怎么連接設備時鐘和sysref到AFE和FPGA?

JESD204B的系統級優勢

JESD204B的優勢

JESD204B標準及演進歷程

TI AFE8092 AFE8030 JESD204C配置及調試手冊 Part B

TI AFE8092 AFE8030 JESD204配置及調試手冊- Part A

JESD204B使用說明

AFE58JD48 12.8 GB JESD204B超聲 AFE技術手冊

AFE58JD48 12.8 GB JESD204B超聲 AFE技術手冊

評論