ADC3664器件是一款低噪聲、超低功耗、14位、125MSPS、高速雙通道ADC。該器件專為實(shí)現(xiàn)最低噪聲性能而設(shè)計(jì),可提供–156.9 dBFS/Hz的噪聲頻譜密度以及出色的線性度和動(dòng)態(tài)范圍。該ADC3664提供IF采樣支持,使該器件適用于廣泛的應(yīng)用。高速控制環(huán)路受益于低至一個(gè)時(shí)鐘周期的短延遲。ADC在125 MSPS時(shí)僅消耗100 mW/ch,其功耗在較低采樣率下可以很好地?cái)U(kuò)展。

該ADC3664使用串行LVDS (SLVDS)接口輸出數(shù)據(jù),從而最大限度地減少數(shù)字互連的數(shù)量。該器件支持雙通道、單通道和半通道選項(xiàng)。該ADC3664與一系列16位分辨率ADC引腳兼容。該器件支持–40至+105?C的擴(kuò)展工業(yè)溫度范圍。

*附件:adc3664.pdf

特性

- 14位125 MSPS ADC

- 本底噪聲:–156.9 dBFS/Hz

- 低功耗:100 mW/ch

- 延遲:2 個(gè)時(shí)鐘周期

- 電壓基準(zhǔn):

- 外部:65 至 125 MSPS

- 內(nèi)部:100 至 125 MSPS

- 保證 14 位,無遺漏代碼

- 輸入帶寬:1.4 GHz (3 dB)

- INL:±2.6 LSB;DNL:±0.9 LSB

- 工業(yè)溫度范圍:–40°C 至 +105°C

- 片上數(shù)字濾波器(可選)

- 抽取 2、4、8、16、32

- 32 位 NCO

- 串行LVDS數(shù)字接口(2線、1線和1/2線)

- 小尺寸:40-VQFN(5 mm × 5 mm)封裝

- 光譜性能(f

在= 5 MHz):- 信噪比:77.5 dBFS

- SFDR:84dBc HD2、HD3

- SFDR:92-dBFS 最差支線

- 光譜性能(f

在= 70 兆赫):- 信噪比:75.5 dBFS

- SFDR:76dBc HD2、HD3

- SFDR:84-dBFS 最差雜散

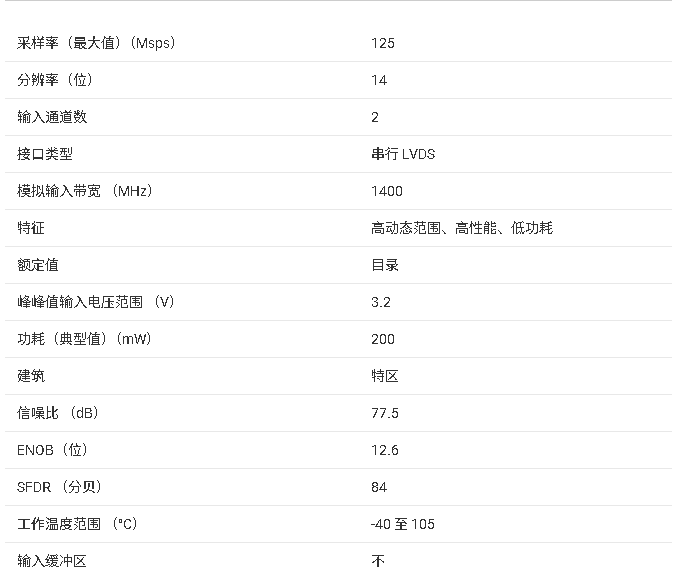

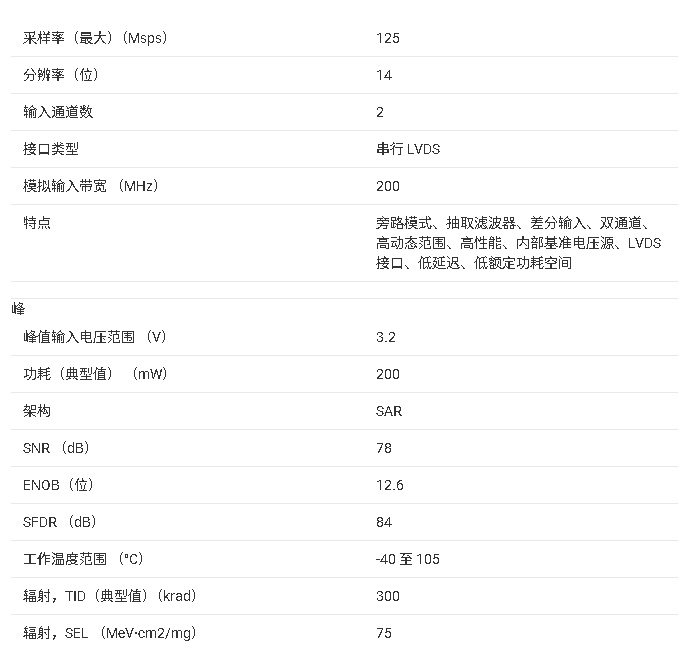

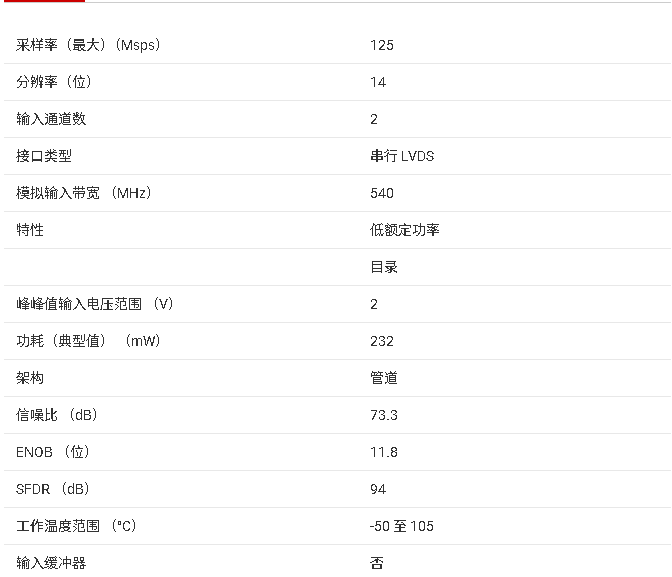

參數(shù)

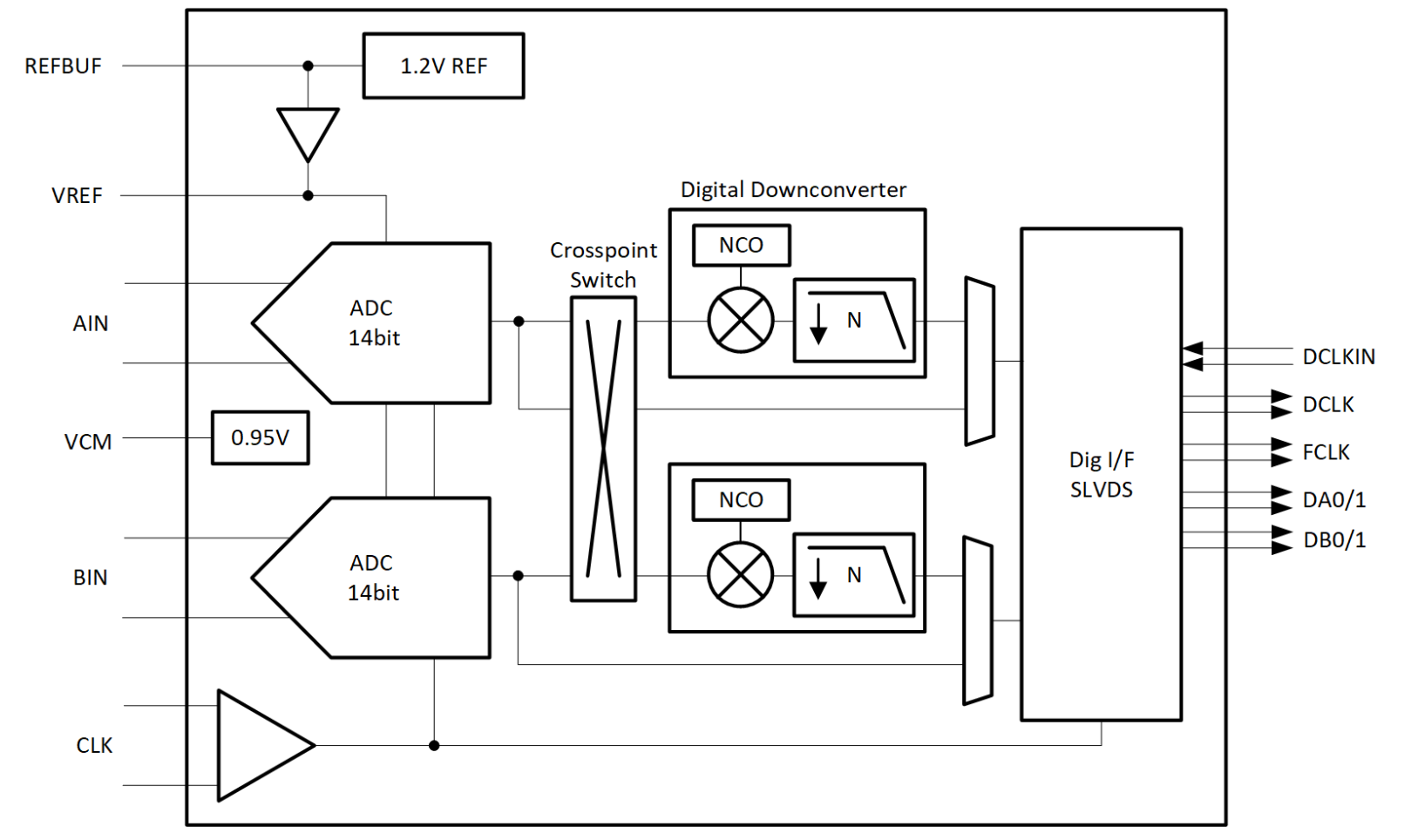

方框圖

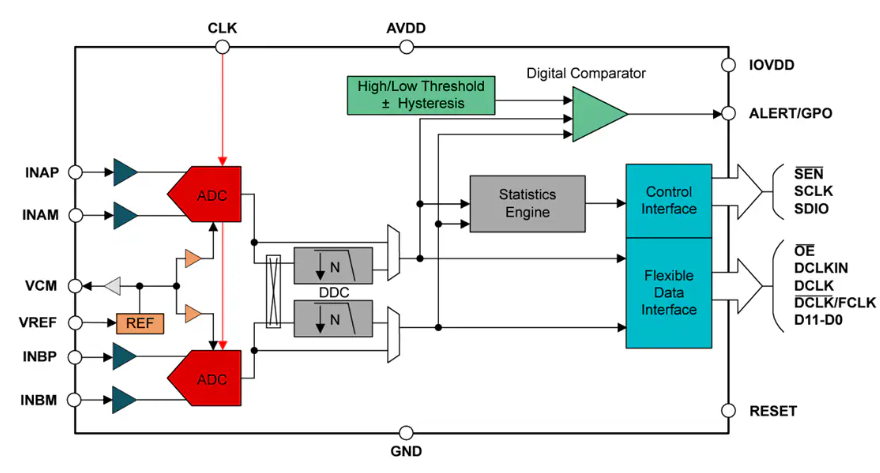

ADC3664 是德州儀器推出的 14 位雙通道高速 ADC,核心優(yōu)勢(shì)為低噪聲、低功耗與靈活數(shù)字信號(hào)處理能力,專為高速數(shù)據(jù)采集、軟件無線電等場(chǎng)景設(shè)計(jì),支持 IF 采樣與多模式數(shù)據(jù)輸出。

核心參數(shù)與特性

- 分辨率與采樣:14 位分辨率無失碼,最高采樣率 125 MSPS;外部參考時(shí)采樣率 65-125 MSPS,內(nèi)部參考時(shí) 100-125 MSPS。

- 動(dòng)態(tài)性能:噪聲譜密度 - 156.9 dBFS/Hz,5MHz 輸入時(shí) SNR 達(dá) 77.5 dBFS、SFDR 92 dBFS;INL±2.6 LSB、DNL±0.9 LSB,線性度優(yōu)異。

- 輸入與帶寬:模擬輸入帶寬 1.4 GHz(-3 dB),差分輸入滿量程 3.2 Vpp;輸入共模電壓 0.95 V,支持 AC/DC 耦合。

- 供電與封裝:模擬 / 數(shù)字供電 1.75V-1.85V,單通道功耗 100 mW(125 MSPS);工作溫度 - 40°C-105°C,采用 40 引腳 WQFN 封裝(5mm×5mm)。

- 接口規(guī)格:串行 LVDS 接口,支持 2 線 / 1 線 / 1/2 線模式;輸出分辨率可配置 14/16/18/20 位,數(shù)據(jù)速率最高 1 Gbps。

關(guān)鍵功能設(shè)計(jì)

- 數(shù)字信號(hào)處理:集成 32 位 NCO 與可編程數(shù)字下變頻器(DDC),支持 2/4/8/16/32 倍實(shí) / 復(fù)抽取;提供 6-dB 數(shù)字增益補(bǔ)償,可減輕外部抗混疊濾波器設(shè)計(jì)壓力。

- 靈活校準(zhǔn)與同步:支持通道平均功能,可通過 SYNC 引腳或 SPI 指令實(shí)現(xiàn)多器件同步;內(nèi)置測(cè)試圖案生成器(斜坡 / 自定義模式),便于系統(tǒng)調(diào)試。

- 參考與時(shí)鐘:支持內(nèi)部 1.6V 參考、外部 1.6V 參考或外部 1.2V 參考(經(jīng)內(nèi)部緩沖放大);時(shí)鐘支持差分 / 單端輸入,單端模式可降低功耗。

- 輸出與控制:支持二進(jìn)制補(bǔ)碼 / 偏移二進(jìn)制輸出格式;通過 SPI 接口或引腳配置核心功能,支持全局 / 局部電源管理,休眠功耗低至 12 mW。

典型應(yīng)用場(chǎng)景

- 數(shù)據(jù)采集:高速數(shù)據(jù)采集系統(tǒng)、源測(cè)量單元(SMU),滿足高精度寬頻段信號(hào)采集需求。

- 通信與儀器:軟件無線電(SDR)、通信基礎(chǔ)設(shè)施、頻譜分析儀,適配 IF 采樣與信號(hào)處理。

- 工業(yè)與雷達(dá):控制環(huán)路、光譜分析、雷達(dá)系統(tǒng),適配低延遲與低功耗需求。

設(shè)計(jì)與使用建議

- 電源與去耦:模擬電源(AVDD)與數(shù)字接口電源(IOVDD)需獨(dú)立供電,就近并聯(lián)低 ESR 去耦電容;參考引腳(VREF/REFBUF)需靠近器件擺放旁路電容,降低噪聲。

- 輸入與時(shí)鐘:模擬輸入建議添加采樣毛刺濾波器,根據(jù)輸入頻率選擇匹配的 RC 參數(shù);時(shí)鐘優(yōu)先選擇低抖動(dòng)差分輸入,長(zhǎng)距離傳輸需終端匹配。

- 布局注意:采用獨(dú)立接地平面,模擬與數(shù)字信號(hào)分區(qū)域布線;差分信號(hào)線長(zhǎng)度匹配,避免阻抗不連續(xù);熱焊盤需焊接至 PCB 接地平面,優(yōu)化散熱。

- 校準(zhǔn)與同步:上電后需硬件復(fù)位初始化,校準(zhǔn)周期約 200000 個(gè)時(shí)鐘周期;多器件同步需確保 SYNC 信號(hào)與采樣時(shí)鐘時(shí)序匹配,抽取模式下同步時(shí)鐘分頻器。

-

MSPS

+關(guān)注

關(guān)注

0文章

574瀏覽量

29024 -

adc

+關(guān)注

關(guān)注

100文章

7796瀏覽量

556639 -

控制環(huán)路

+關(guān)注

關(guān)注

1文章

55瀏覽量

9830 -

噪聲頻譜

+關(guān)注

關(guān)注

0文章

28瀏覽量

2259

發(fā)布評(píng)論請(qǐng)先 登錄

14 位 125Msps 低功率雙通道 ADC 增強(qiáng)了高效基站收發(fā)器的性能

非常低功耗的 12 位 / 14 位 25Msps 至 125Msps ADC 在 125Msps 時(shí)以低于 100mW 工作

四通道/雙通道 14 位、125Msps ADC 消耗的功率僅為同類器件的三分之一

LTC2175-14: 14 位、125Msps 低功率四通道 ADC 數(shù)據(jù)手冊(cè)

TI通過全新的SAR ADC系列(包括業(yè)界超快的18位ADC),縮小高速和精度方面的差距

ADC3664 14位、125MSPS、低噪聲、低功率雙通道ADC數(shù)據(jù)表

ADC3564 14位、125MSPS、低噪聲、超低功耗ADC數(shù)據(jù)表

ADC3644 14位125MSPS低噪聲低功耗雙通道ADC數(shù)據(jù)表

ADS42xx雙通道、14位/12位、160MSPS/125MSPS/65MSPS、超低功耗ADC數(shù)據(jù)表

ADC3244E雙通道、14位、125MSPS模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

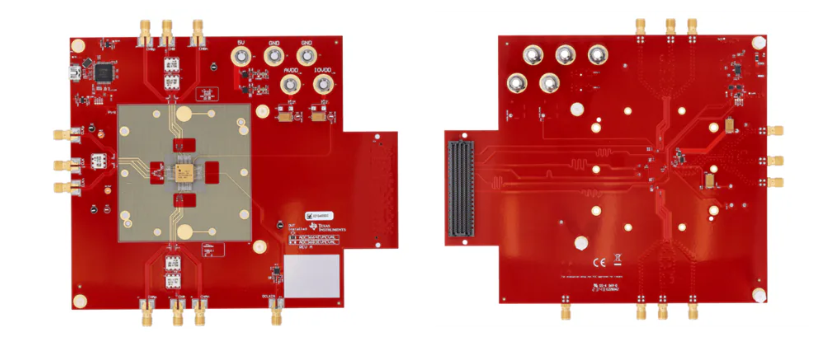

Texas Instruments ADC3664EVMCVAL評(píng)估模塊數(shù)據(jù)手冊(cè)

德州儀器ADC3910系列:高性能低功耗10位125MSPS ADC技術(shù)解析

ADC3664-SP 輻射加固型雙通道模數(shù)轉(zhuǎn)換器(ADC)產(chǎn)品文檔總結(jié)

ADC3244E 具有擴(kuò)展溫度范圍的雙通道 14 位 125MSPS 模數(shù)轉(zhuǎn)換器技術(shù)手冊(cè)

ADC3664 雙通道、14位、125MSPS、高信噪比、低功耗ADC技術(shù)手冊(cè)

ADC3664 雙通道、14位、125MSPS、高信噪比、低功耗ADC技術(shù)手冊(cè)

評(píng)論