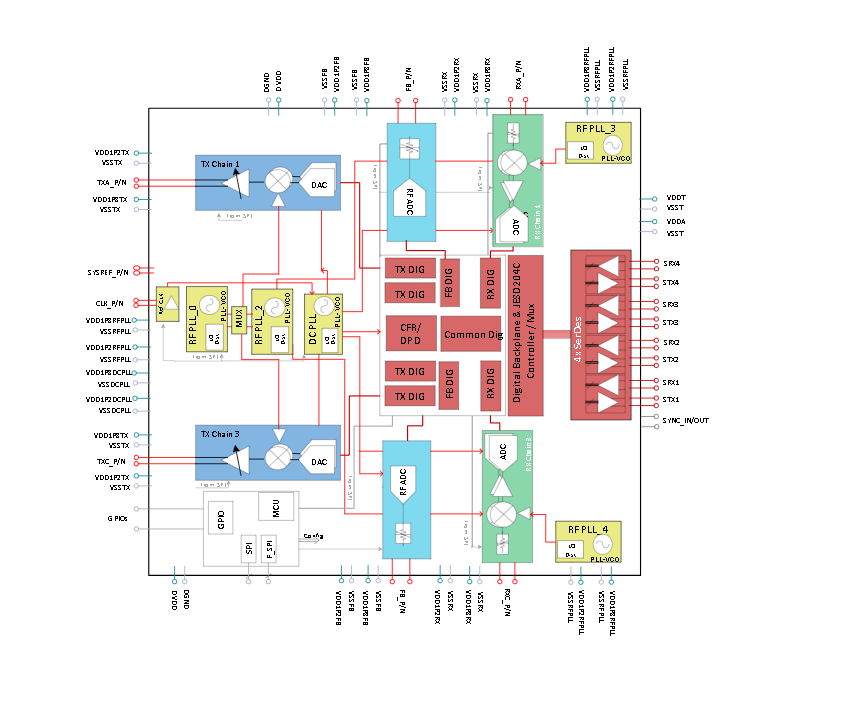

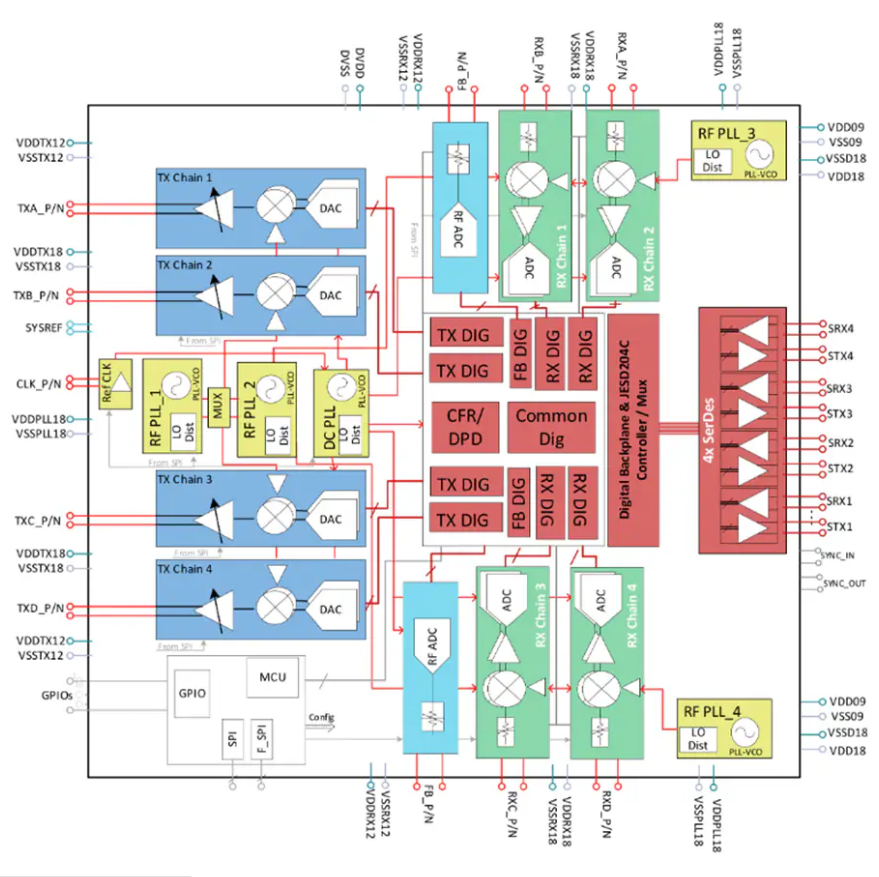

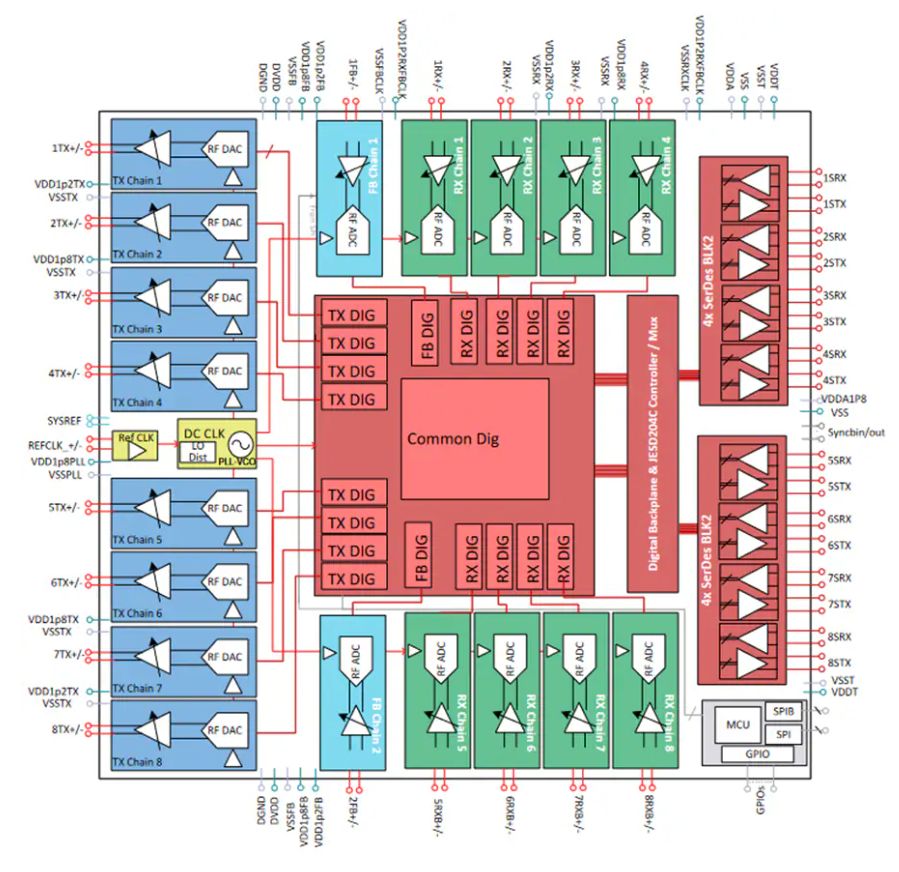

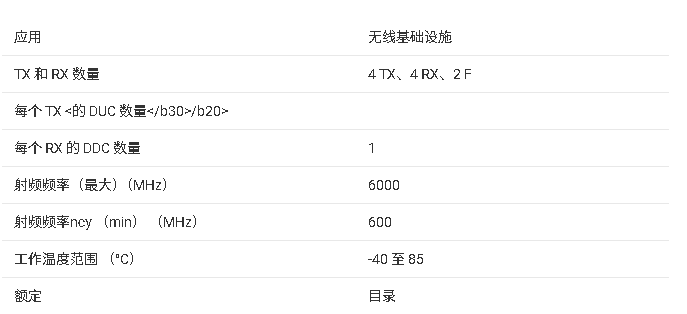

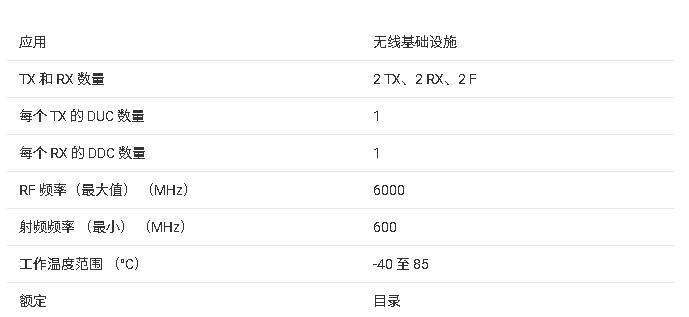

AFE77xxD 是一個引腳兼容的高性能多通道收發器系列,集成了四個 (AFE7768D/AFE7769D) 或兩個 (AFE7728D) 個直接上變頻發射器鏈、四個 (AFE7768D/AFE7769D) 或兩個 (AFE7728D) 直接下變頻接收器鏈、兩個寬帶射頻采樣數字化輔助鏈(反饋路徑)和用于功率放大器 (PA) 線性化的低功耗數字預失真 (DPD) 引擎。發射器和接收器鏈的高動態范圍使無線基站能夠發射和接收 2G、3G、4G 和 5G 信號。集成的波峰因數降低 (CFR) 單元有助于降低輸入信號的峰均比 (PAR),從而通過功率放大器實現更高效的傳輸。集成的硬件加速 DPD 估計器和校正器為 PA 線性化提供了靈活高效的 DPD 解決方案。集成的 DPD 引擎可校正高達 200MHz (AFE77x8D) / 300MHz (AFE7769D) 瞬時帶寬和高達 650MHz (AFE77x8D) / 730MHz (AFE7769D) DPD 擴展帶寬內信號的 PA 非線性失真。專用的 GaN 校正器可解決由于 GaN PA 的電荷捕獲而導致的長期非線性記憶效應。

*附件:afe7768d.pdf

AFE77xxD 的低功耗和高密度通道集成使該器件能夠解決 4G 和 5G 基站的功率和尺寸限制。寬帶和高動態范圍反饋路徑可以通過在各個攔截點進行智能數據捕獲來輔助發射器鏈中功率放大器的 DPD。可用的 29.5Gbps SerDes 速度有助于減少將數據傳入和傳出設備所需的通道數量。

AFE77xxD 的每個接收器鏈包括一個 28 dB 范圍數字步進衰減器 (DSA),然后是一個寬帶無源 IQ 解調器,以及一個基帶放大器,該放大器集成了具有可編程帶寬的抗混疊低通濾波器,可驅動連續時間 Σ-Δ ADC。RX 鏈可以接收高達 200 MHz (AFE77x8D) / 300 MHz (AFE7769D) 的瞬時帶寬 (IBW)。每個接收器通道都有兩個模擬峰值功率檢測器和各種數字功率檢測器,以協助接收器通道的外部或內部自主 AGC 控制,以及一個用于器件可靠性保護的射頻過載檢測器。集成的 QMC(正交失配補償)算法能夠連續監控和校正 RX 鏈 I 和 Q 不平衡失配,而無需注入任何特定信號或執行離線校準。

每個發射器鏈包括兩個 14 位、3.3 Gsps IQ DAC,然后是一個可編程重建和 DAC 鏡像抑制濾波器,一個 IQ 調制器驅動具有 39 dB 范圍增益控制的寬帶 RF 放大器。TX 鏈集成了 QMC 和 LO 泄漏消除算法,利用 FB 路徑可以持續跟蹤和校正 TX 鏈 IQ 失配和 LO 泄漏。

每個FB路徑都基于RF采樣架構,包括一個驅動14位、3.3Gsps RF ADC的輸入RF DSA。直接采樣架構提供了固有的寬帶接收器鏈,并簡化了TX鏈損傷的校準。FB路徑集成了兩個獨立的NCO,允許在兩個觀察到的RF輸入頻段之間快速切換。

合成器部分集成了四個小數N分頻RF PLL,可以生成四個不同的RF LO,使該器件能夠支持多達兩個不同的頻段,每個頻段配置為兩個發射器、兩個接收器和一個反饋路徑(帶AFE7768D/AFE7769D),或者一個發射器、一個接收器和一個反饋路徑(帶AFE7728D)。

特性

- 基于 0-IF 上變頻架構的四通道 (AFE776xD) / 雙通道 (AFE7728D) 發射機:

- 每條鏈高達 650 MHz (AFE77x8D) / 730 MHz (AFE7769D) 的射頻傳輸 DPD 擴展帶寬

- 基于0-IF下變頻架構的四通道(AFE776xD)/雙通道(AFE7728D)接收器:

- 每條鏈高達 200 MHz (AFE77x8D) / 300 MHz (AFE7769D) 的射頻接收帶寬

- 基于直接射頻采樣架構的反饋鏈:

- 高達 650 MHz (AFE77x8D) / 730 MHz (AFE7769D) 的射頻觀察 DPD 擴展帶寬

- 用于 PA 線性化的集成 CFR/DPD

- 高達 200MHz (AFE77x8D) / 300MHz (AFE7769D) 瞬時帶寬

- 高達 650MHz (AFE77x8D) / 730MHz (AFE7769D) DPD 擴展帶寬

- 用于 PA 線性化的集成 CFR/DPD

- 多級 CFR,具有可配置的消除脈沖

- 硬件加速 DPD 估計引擎

- 基于信號動力學的GaN PA線性化校正器

- 智能數據采集

- 射頻頻率范圍:600 MHz 至 6 GHz

- 四個寬帶小數N PLL,用于TX和RX LO的VCO

- 專用整數 N PLL、VCO,用于數據轉換器時鐘生成

- JESD204B和JESD204C SerDes 接口支持:

- 4 個高達 29.5 Gbps 的 SerDes 收發器

- 8b/10b 和 64b/66b 編碼

- 16 位、12 位、24 位和 32 位格式化

- 子類 1 多設備同步

- 封裝:17 mm × 17 mm FCBGA,0.8 mm 間距

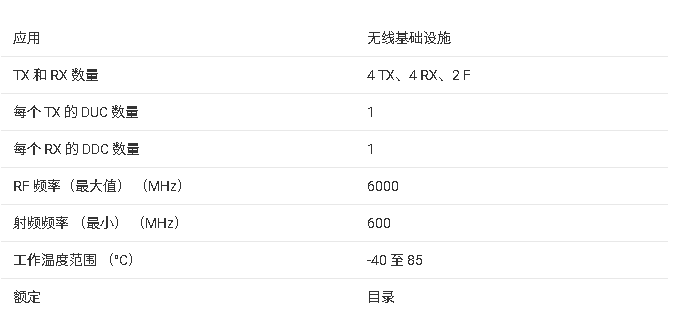

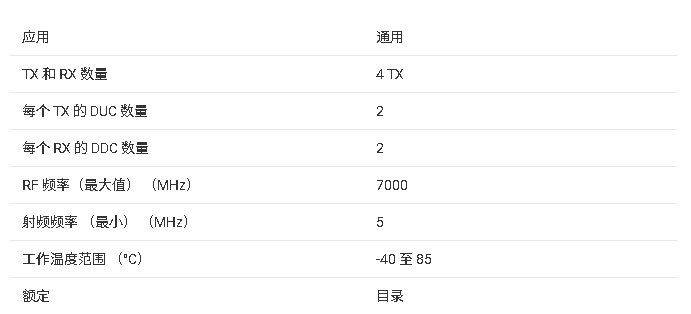

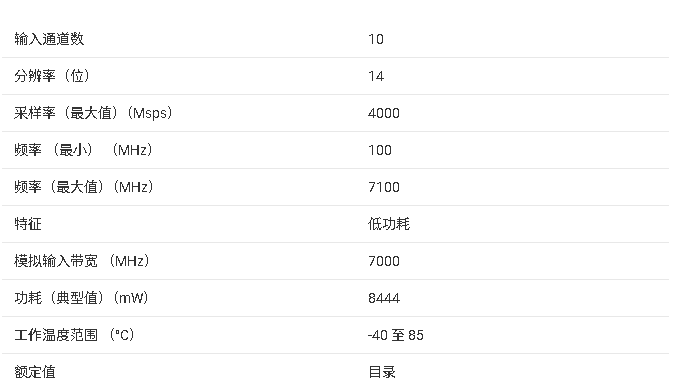

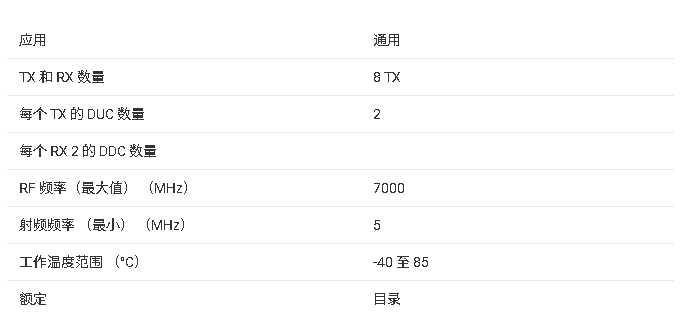

參數

方框圖

一、核心特性與產品定位

1. 基礎參數與架構

- 通道配置 :

- 發射鏈路(TX):2 條 0-IF 上變頻鏈路,每條支持最高 650MHz DPD 擴展帶寬(瞬時帶寬 200MHz),集成 14 位 3.3Gsps IQ DAC、可編程重建濾波器及 39dB 增益控制的 RF 放大器。

- 接收鏈路(RX):2 條 0-IF 下變頻鏈路,每條支持最高 200MHz 瞬時帶寬,集成 28dB 數字步進衰減器(DSA)、寬帶無源 IQ 解調器、抗混疊低通濾波器及連續時間 sigma-delta ADC。

- 反饋路徑(FB):2 條基于直接 RF 采樣的輔助鏈路,每條集成 14 位 3.3Gsps RF ADC、輸入 RF DSA 及 2 個獨立 NCO(數控振蕩器),支持快速切換觀測頻段,輔助 TX 鏈路校準與 PA 線性化。

- 核心增強功能 :

- PA 線性化:內置硬件加速 DPD 估計器與校正器,支持 GaN PA 電荷捕獲導致的長期非線性記憶效應補償,DPD 擴展帶寬最高 650MHz,瞬時帶寬 200MHz,降低 PA 非線性失真。

- 信號優化:集成多階段 CFR(峰值因子降低),可配置抵消脈沖,減少輸入信號峰均比(PAR),提升 PA 效率。

- 校準能力:TX/RX 鏈路均支持正交失配補償(QMC)與 LO 泄漏抵消,無需注入特定信號或離線校準,實時修正 I/Q 失衡與本振泄漏。

- 頻率與時鐘 :

- RF 頻率范圍:600MHz-6GHz,覆蓋 4G/5G 主流頻段(如 Sub-6GHz)。

- 時鐘生成:集成 4 個分數 - N RF PLL(生成 TX/RX LO)與 1 個整數 - N PLL(為數據轉換器提供時鐘),支持 4 種不同 RF LO,可適配 2 個不同工作頻段。

- 接口與同步 :

- 高速接口:支持 JESD204B/C SerDes,4 個 SerDes 收發器最高速率 29.5Gbps,支持 8b/10b 與 64b/66b 編碼,16/12/24/32 位數據格式,減少數據傳輸 lanes 數量。

- 同步能力:支持 Subclass 1 多器件同步,通過 SYSREF 與 SYNC 引腳實現多 AFE7728D 或多通道系統的時鐘與數據同步,適配 mMIMO(大規模多輸入多輸出)場景。

2. 環境適應性與封裝

- 工作條件 :

- 封裝與可靠性 :

- 封裝:17mm×17mm FCBGA(球柵陣列),400 引腳,0.8mm 引腳間距,底部無熱焊盤(需通過 PCB 布局優化散熱)。

- ESD 防護:需遵循靜電放電防護規范(如人體放電模型 HBM±2000V),避免裝配與使用過程中器件損壞。

3. 典型應用場景

- 5G 小基站 / 宏基站 :作為 RRU(遠程射頻單元)核心收發器,支持多頻段信號發射與接收,DPD/CFR 功能提升 PA 效率,降低基站功耗。

- 有源天線系統(AAS) :適配 mMIMO 架構,多器件同步能力支持多通道信號協同,滿足大規模天線陣列的高精度相位與幅度一致性要求。

- 分布式天線系統(DAS) :小型化封裝與低功耗特性,適配室內分布式覆蓋場景,寬頻段支持可兼容多運營商頻段。

- 中繼器(Repeater) :高動態范圍 RX 鏈路可接收弱信號,TX 鏈路的功率控制與線性化能力確保中繼信號質量。

二、關鍵性能參數

1. 核心射頻性能(典型值,常溫環境)

| 性能類別 | 參數 | 規格 | 單位 |

|---|---|---|---|

| 發射鏈路(TX) | 瞬時帶寬(IBW) | 200 | MHz |

| DPD 擴展帶寬 | 650 | MHz | |

| DAC 分辨率 / 速率 | 14 位 / 3.3Gsps | - | |

| 增益控制范圍 | 39 | dB | |

| LO 泄漏(@2GHz) | -60 | dBm | |

| 接收鏈路(RX) | 瞬時帶寬(IBW) | 200 | MHz |

| ADC 動態范圍(DR) | 65 | dB | |

| 噪聲系數(NF) | 4.5 | dB | |

| DSA 衰減范圍 | 28 | dB | |

| 輸入三階截點(IIP3) | -10 | dBm | |

| 反饋路徑(FB) | ADC 分辨率 / 速率 | 14 位 / 3.3Gsps | - |

| 輸入帶寬 | 600-6000 | MHz | |

| DSA 衰減范圍 | 31 | dB | |

| DPD/CFR | DPD 校正帶寬 | 650(擴展)/200(瞬時) | MHz |

| CFR 峰值抑制 | 6 | dB |

三、核心功能架構

1. 發射鏈路(TX)

- 信號流程 :基帶 IQ 數據經 JESD204C 接口輸入,由 14 位 3.3Gsps IQ DAC 轉換為模擬信號,經可編程重建濾波器與 DAC 鏡像抑制濾波器處理后,送入 IQ 調制器與 RF 放大器,最終通過 TX 天線端口輸出。

- 關鍵模塊 :

- IQ 調制器:實時修正正交失衡(通過 QMC 算法)與 LO 泄漏,保障調制精度。

- RF 放大器:39dB 增益控制范圍,支持精細功率調節,適配不同 PA 驅動需求。

- DPD 集成:DPD 引擎根據 FB 路徑反饋的 PA 輸出信號,生成預失真系數,對 TX 輸入信號進行預處理,抵消 PA 非線性失真。

2. 接收鏈路(RX)

- 信號流程 :RF 信號經 RX 天線端口輸入,先通過 28dB DSA 調節衰減(適配不同強度輸入信號),再經寬帶無源 IQ 解調器下變頻至基帶,由抗混疊低通濾波器濾除高頻噪聲,最終送入連續時間 sigma-delta ADC 轉換為數字信號,通過 JESD204C 接口輸出。

- 關鍵模塊 :

- 功率檢測:集成 2 個模擬峰值功率檢測器與多個數字功率檢測器,輔助外部 / 內部 AGC(自動增益控制),保護器件免受過載損傷。

- QMC 算法:實時監測并修正 I/Q 通道幅度與相位失衡,無需離線校準,確保接收信號保真度。

3. 反饋路徑(FB)

- 核心作用 :通過直接 RF 采樣采集 PA 輸出信號,送入 14 位 3.3Gsps RF ADC 轉換為數字信號,用于 TX 鏈路 QMC 校準、LO 泄漏抵消及 DPD 系數估計。

- 靈活性設計 :2 個獨立 NCO 支持快速切換 2 個觀測頻段,無需重新配置硬件,適配多頻段 PA 線性化場景;輸入 RF DSA 可調節信號幅度,確保 ADC 工作在最佳動態范圍。

4. 時鐘與同步

- PLL 配置 :4 個分數 - N RF PLL 生成 TX/RX 所需的 RF LO(600MHz-6GHz),支持 4 種不同頻率,可同時適配 2 個工作頻段;1 個整數 - N PLL 為 DAC/ADC 提供高精度時鐘,保障數據轉換器性能。

- 多器件同步 :支持 JESD204B/C Subclass 1 同步,通過 SYSREF(系統參考時鐘)與 SYNC(同步信號)引腳,實現多 AFE7728D 之間的時鐘相位對齊與數據幀同步,滿足 mMIMO 多通道協同需求。

-

收發器

+關注

關注

10文章

3789瀏覽量

110426 -

功率放大器

+關注

關注

104文章

4131瀏覽量

138773 -

接收器

+關注

關注

15文章

2629瀏覽量

76135 -

發射器

+關注

關注

7文章

916瀏覽量

55096 -

輸入信號

+關注

關注

0文章

515瀏覽量

13101

發布評論請先 登錄

AFE7768D雙通道 RF 收發器技術總結

AFE7768D雙通道 RF 收發器技術總結

評論