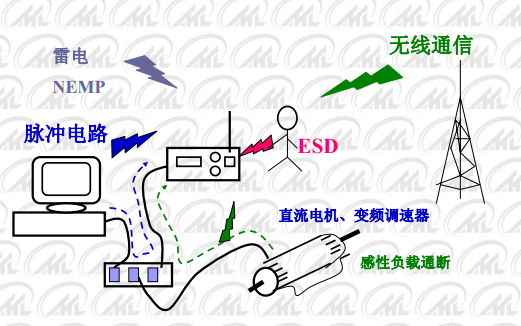

靜電在自然界中無處不在。從芯片制造、封裝測試、運輸存儲到組裝使用,靜電可能在任一環節對芯片造成不可逆損。

1. 隱蔽性

(1)人體通常需2~3KV靜電才能感知,而現代半導體器件可能僅需不到20V即會受損。(2)在無塵室中,技術人員身著防靜電服時,仍可能攜帶足以損傷芯片的靜電。

2. 潛在性

(1)部分受損元器件外觀完好,初始功能正常,卻已留下“內傷”。

(2)此類產品可通過常規檢測出廠,但在實際使用中(1周至6個月內)易提前失效。

3.隨機性

(1)從芯片生產到使用壽命結束,靜電威脅可能來自人體、設備、環境等各方面。

(2)靜電產生的不確定性導致質量問題難以系統性預防與追蹤。

4. 復雜性

(1)靜電損傷的失效分析需借助掃描電鏡等高精密儀器,耗時耗力。

(2)部分損傷特征易被誤判為“早期失效”或“原因不明失效”,掩蓋真相。

先進工藝下的ESD防護困境

1. 技術進步帶來的負面影響

(1)隨著晶體管特征尺寸縮小,芯片ESD防護能力持續減弱。

(2)65nm至90nm工藝節點下,柵氧化層厚度小于2nm,擊穿電壓降低,對ESD保護電路提出更高要求。

2. 工藝特性加劇ESD風險

(1)輕摻雜漏技術易引發尖端放電,使MOS管更易被靜電擊穿。

(2)硅化物工藝為靜電電流提供進入芯片內部的路徑,增加損壞風險。

3. 防護成本不斷攀升

(1)市場對防護等級要求提升,迫使設計人員開發更優異的ESD防護方案。

(2)從0.18微米工藝節點開始,專用定制方案比例增加,顯著推高設計成本。

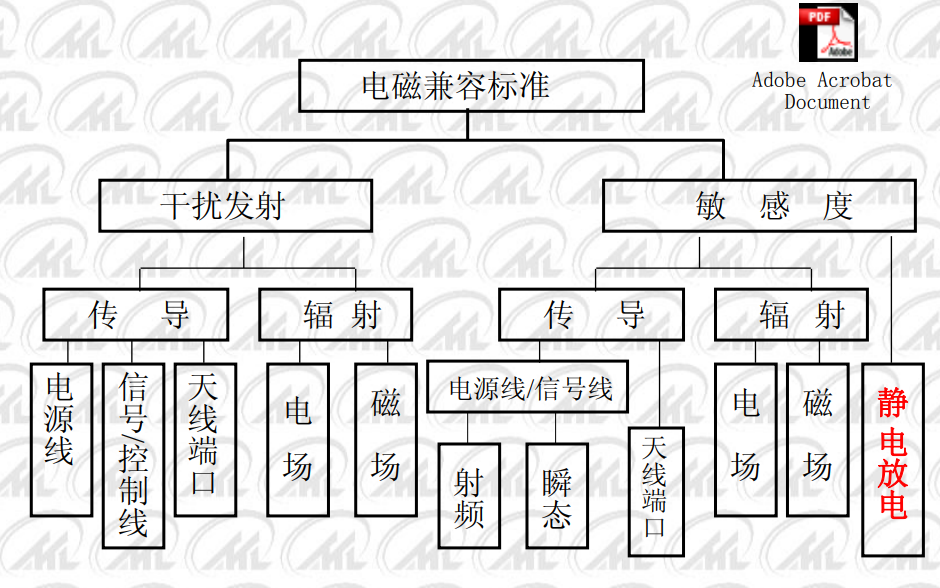

ESD防護電路設計的核心原則

面對日益嚴峻的靜電挑戰,ESD防護電路設計需要遵循五個基本原則,這些原則共同定義了ESD防護的設計窗口。

1. 正常狀態下的關閉特性。

在無ESD事件發生時,保護器件必須保持關閉狀態,任何誤觸發都可能導致核心電路功能異常。

2. 快速響應能力。

當芯片遭遇ESD事件時,保護器件必須在納秒級時間內迅速開啟,特別是應對快速的器件充電模型事件。響應速度的絲毫延遲都可能導致核心電路損毀。

3. 電壓鉗位能力。

ESD事件期間,芯片管腳上的總電壓(包括保護器件上的電壓與金屬互連線上的電壓)必須不超過核心電路的耐受極限,否則將造成不可逆損傷。

4. 魯棒性。

在設計的ESD保護等級下,防護電路本身必須能夠承受靜電沖擊而不損壞,這關系到器件在真實環境中的生存能力。

5. 自恢復功能。

確保系統持續穩定運行。ESD事件結束后,保護器件應能自動返回關閉狀態,避免進入閂鎖狀態而導致電路故障。基于這些原則,可以明確ESD防護電路的安全設計窗口:防護電路的開啟電壓必須低于內部器件柵氧化層的擊穿電壓;保持電壓需高于電路正常工作電壓,防止誤開啟;工作電流應小于器件的熱失效電流,避免二次擊穿。隨著工藝節點不斷縮小,ESD設計窗口日益狹窄,芯片抗擊靜電能力持續減弱,這對防護設計提出了更高要求。

結語

靜電放電已成為半導體器件最常見的失效機理之一。在芯片設計階段,必須充分考慮被防護器件的抗靜電能力,合理選擇ESD防護方案,以保障芯片在貼裝、測試、轉運及最終應用過程中免受ESD損傷。

-

ESD

+關注

關注

50文章

2416瀏覽量

180178 -

靜電

+關注

關注

2文章

559瀏覽量

38344 -

半導體器件

+關注

關注

12文章

808瀏覽量

34224

發布評論請先 登錄

晶閘管型防護器件—半導體放電管

電路靜電防護小科普:了解放電器件與ESD防護方法

ESD靜電阻保護器件的應用

靜電放電ESD的介紹和原理及解決方法概述

半導體器件的靜電放電(ESD)失效機理與防護設計

半導體器件的靜電放電(ESD)失效機理與防護設計

評論