ADS911x是18位高速模數(shù)轉(zhuǎn)換器(ADC)系列,具有用于ADC輸入的集成驅(qū)動器。集成的ADC驅(qū)動器簡化了信號鏈,降低了精密應(yīng)用的功耗,并支持超過1MHz的高頻信號。由于不需要外部去耦電容,集成ADC基準電壓緩沖器針對寬帶寬應(yīng)用進行了優(yōu)化。

ADS911x使用串行LVDS(SLVDS)數(shù)據(jù)接口,可實現(xiàn)高速數(shù)字通信,同時最大限度地降低數(shù)字開關(guān)噪聲。使用每個ADC通道的單獨SLVDS輸出或兩個ADC通道的一個SLVDS輸出讀取雙通道ADC數(shù)據(jù)。

*附件:ads9117.pdf

特性

- 高速低功耗:

- ADS9119:20MSPS,274mW

- ADS9118:10MSPS,83mW

- ADS9117:5MSPS,59mW

- 功能集成:

- 集成ADC驅(qū)動器

- 集成精密參考

- 共模電壓輸出緩沖器

- 高性能:

- 18 位無缺失代碼

- INL:±0.8LSB,DNL:±0.4LSB

- 信噪比:95.5dB

- 寬輸入帶寬:

- ADS9119和ADS9118:90MHz (–3dB)

- ADS9117:45MHz (–3dB)

- 串行LVDS接口:

- 擴展工作范圍:–40°C 至 +125°C

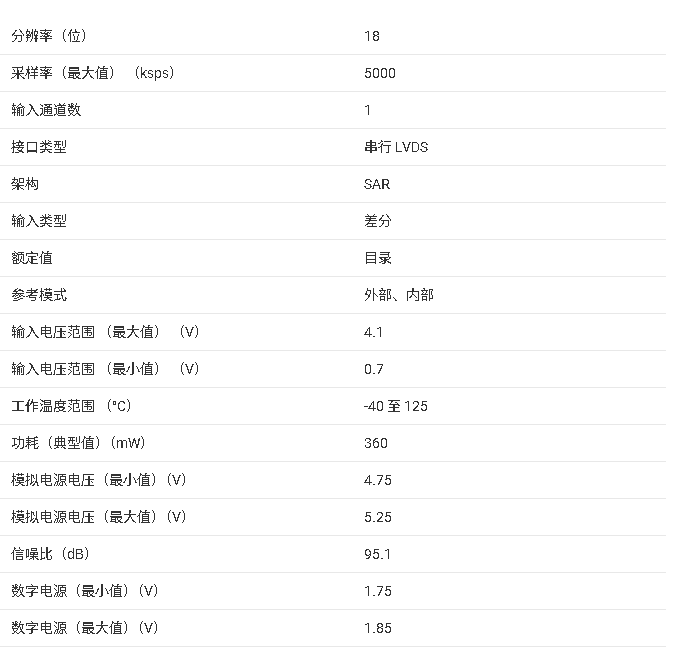

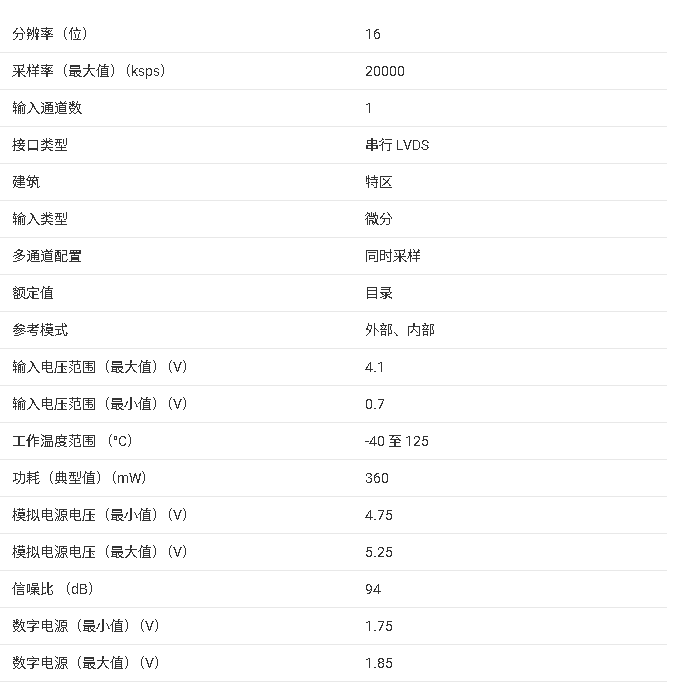

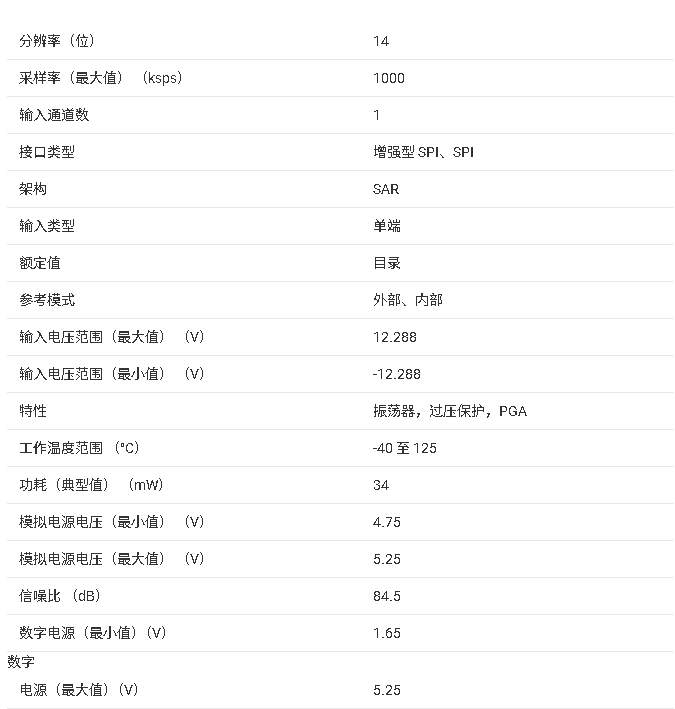

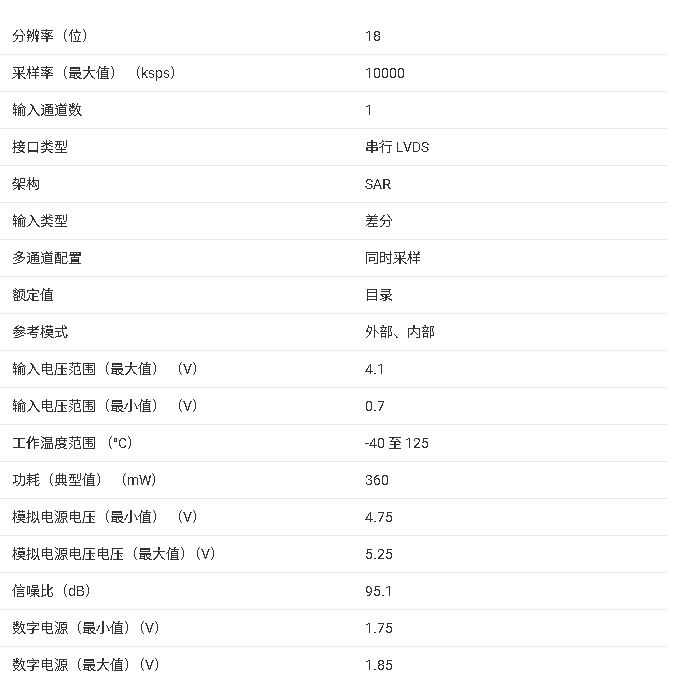

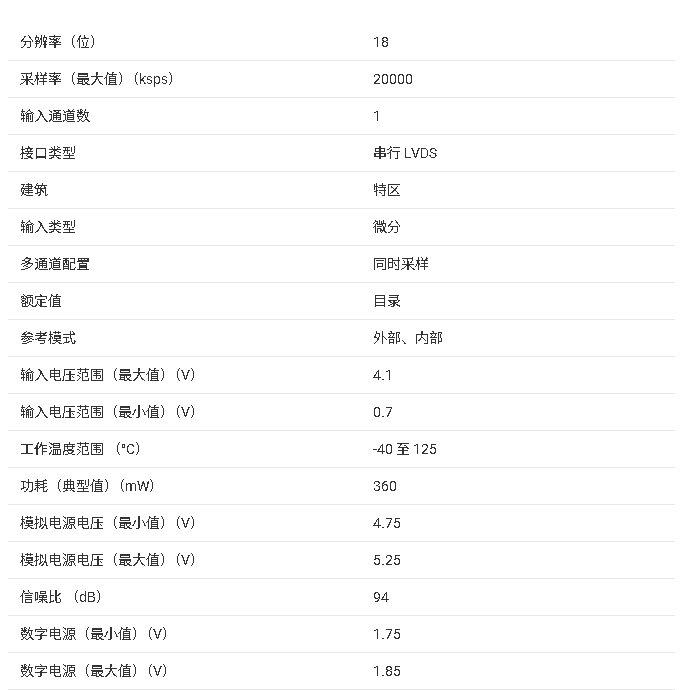

參數(shù)

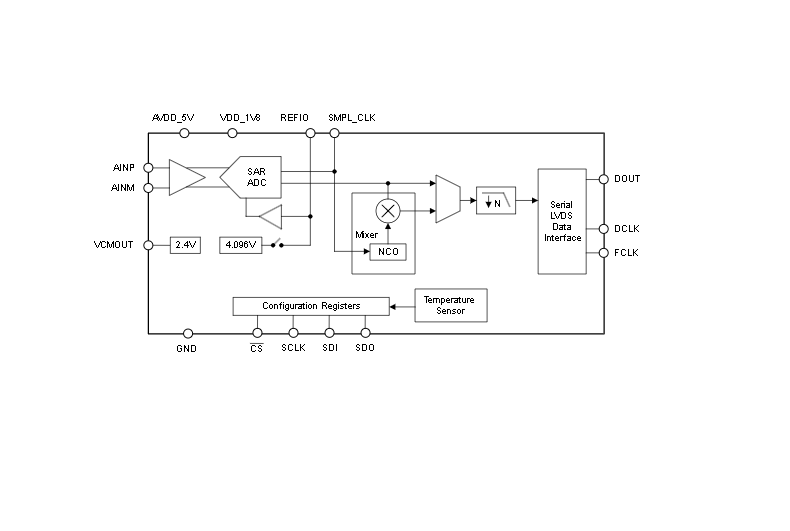

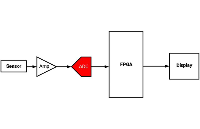

方框圖

一、核心特性

1. 采樣性能與輸入特性

- 采樣速率 :三款型號速率差異化,ADS9119 最高 20MSPS,ADS9118 10MSPS,ADS9117 5MSPS,滿足不同實時性需求。

- 輸入帶寬 :ADS9119/ADS9118 輸入帶寬 90MHz(-3dB),ADS9117 45MHz,支持高頻信號采集(如 1MHz 信號);全量程輸入范圍 ±3.2V(差分),輸入偏置電流低至 0.1nA,溫漂 0.1nA/℃,減少信號失真。

- 精度指標 :無失碼 18 位,微分非線性(DNL)±0.4LSB,積分非線性(INL)±0.8LSB;信噪比(SNR)典型 95.5dB,總諧波失真(THD)低至 -118dB,寬溫(-40℃~125℃)下性能穩(wěn)定。

2. 集成功能與信號處理

- 模擬前端 :集成 ADC 輸入驅(qū)動,無需外部放大器;內(nèi)置二階低通抗混疊濾波器,抑制帶外噪聲;VCMOUT 引腳提供 2.4V 共模電壓,用于輸入信號電平匹配。

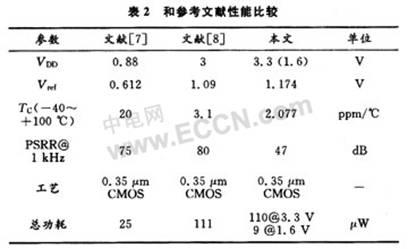

- 參考電壓 :片內(nèi)集成 4.096V 精密參考源,溫度漂移 6~20ppm/℃,REFIO 引腳可配置為外部參考輸入,需外接 10μF 電容 decoupling 以降低噪聲。

- 數(shù)據(jù)處理 :支持 2/4/8/16 倍過采樣(OSR),通過平均算法降低噪聲;內(nèi)置數(shù)字下變頻器(DDC),含 24 位數(shù)控振蕩器(NCO),可輸出 I/Q 正交信號,適配信號解調(diào)場景。

3. 數(shù)字接口與控制

- LVDS 接口 :支持單數(shù)據(jù)率(SDR)與雙數(shù)據(jù)率(DDR)輸出,數(shù)據(jù)幀寬度可選 20 位或 24 位;差分時鐘(DCLK)與幀時鐘(FCLK)同步輸出,減少數(shù)字噪聲串擾,支持多器件同步(SMPL_SYNC 引腳)。

- 配置接口 :SPI 接口用于寄存器配置(3 個寄存器組),支持菊花鏈(Daisy-Chain)多器件級聯(lián);提供測試模式(固定圖案、數(shù)字斜坡、交替圖案),便于調(diào)試數(shù)據(jù)接口。

- 低功耗設(shè)計 :20MSPS 時總功耗 274mW(ADS9119),支持掉電模式(AVDD_5V 電流典型 2μA)與通道獨立掉電,適配低功耗場景。

二、電氣規(guī)格與環(huán)境特性

1. 電源需求

- 模擬電源(AVDD_5V) :4.75V~5.25V,需與 AGND 之間并聯(lián) 10μF+0.1μF 電容 decoupling,降低電源噪聲對模擬信號的影響。

- 數(shù)字電源(VDD_1V8) :1.75V~1.85V,需與 DGND 并聯(lián) 1μF+0.1μF 電容,避免數(shù)字噪聲串擾模擬部分;兩種電源獨立供電,減少相互干擾。

2. 熱特性與封裝

- 封裝形式 :采用 6mm×6mm 40 引腳 VQFN(RHA)封裝,暴露熱焊盤需連接至接地平面,確保散熱;結(jié)到環(huán)境熱阻(RθJA)25.8℃/W,結(jié)到板熱阻(RθJB)7.5℃/W,高負載下結(jié)溫不超 150℃。

- ESD 防護 :模擬輸入引腳(AINP/AINM)人體放電模型(HBM)±2000V,其他引腳 HBM±1000V;帶電器件模型(CDM)所有引腳 ±500V,提升組裝與使用過程中的抗靜電能力。

三、功能模塊與操作模式

1. 數(shù)據(jù)處理功能

- 數(shù)據(jù)平均 :支持 2/4/8/16 倍過采樣,通過寄存器配置 OSR 實現(xiàn),輸出數(shù)據(jù)率隨過采樣比降低(如 16 倍過采樣時,20MSPS 降至 1.25MSPS),同時提升 SNR 性能。

- 數(shù)字下變頻(DDC) :集成數(shù)字混頻器與 NCO,NCO 頻率可通過寄存器配置(公式:fNCO ? =224fSMP L _CLK? ? ×NCOFREQUENCY ? ),輸出 24 位 I/Q 數(shù)據(jù),適用于信號解調(diào)與頻率分析。

- 溫度監(jiān)測 :內(nèi)置 10 位溫度傳感器,通過 SPI 讀取溫度數(shù)據(jù)(范圍 -40℃~125℃),可用于系統(tǒng)溫度補償。

2. 工作模式與控制

- 正常模式 :采樣時鐘(SMPL_CLK)觸發(fā)轉(zhuǎn)換,LVDS 接口輸出 18 位 MSB 對齊數(shù)據(jù),支持二進制補碼或無符號格式。

- 掉電模式 :PWDN 引腳(低有效)或寄存器配置觸發(fā),模擬部分斷電,AVDD_5V 電流降至 2μA;復(fù)位(RESET 引腳,低有效)可重置所有寄存器至默認值。

- 多器件同步 :SMPL_SYNC 引腳用于多 ADC 同步采樣,通過脈沖復(fù)位內(nèi)部過采樣濾波器,確保多通道數(shù)據(jù)時序一致。

四、硬件設(shè)計要點

1. 電源與參考電路

- 電源 decoupling :AVDD_5V 與 AGND 之間、VDD_1V8 與 DGND 之間均需并聯(lián) 10μF 鉭電容 + 0.1μF 陶瓷電容,電容需緊貼引腳,避免寄生電感。

- 參考電路 :使用內(nèi)部參考時,REFIO 與 REFM 之間并聯(lián) 10μF 電容;使用外部參考時,需將 REFIO 接 4.096V 精密參考源(如 REF7040),并禁用內(nèi)部參考(寄存器 PD_REF=1)。

2. 輸入信號布線

- 差分走線 :AINP/AINM 需差分布線,阻抗匹配(建議 100Ω),長度誤差≤5mil,與數(shù)字信號(SCLK、LVDS 線)間距≥2mm,減少串擾;高頻信號(>2MHz)需開啟 HI_FREQ_EN 位,優(yōu)化輸入 slew rate。

- 時鐘設(shè)計 :SMPL_CLK 支持差分 LVDS 或單端 CMOS 輸入,差分輸入時需在 SMPL_CLKP/SMPL_CLKM 引腳外接 100Ω 匹配電阻;時鐘抖動需控制在 0.3~0.8ps RMS,避免 SNR 性能退化。

3. LVDS 接口設(shè)計

- 差分匹配 :DOUTP/DOUTM、DCLKP/DCLKM、FCLKP/FCLKM 均為差分對,需在接收端(如 FPGA)附近并聯(lián) 100Ω 電阻,傳輸線長度控制在 20mm 以內(nèi),減少信號反射。

- 時序同步 :DDR 模式下,數(shù)據(jù)在 DCLK 上升沿與下降沿均傳輸,需確保 DCLK 占空比 45%~55%;SDR 模式僅上升沿傳輸,數(shù)據(jù)延遲需匹配系統(tǒng)時序要求。

五、適用場景

- 測試測量 :源測量單元(SMU)、功率分析儀,依托高采樣速率(20MSPS)與寬帶寬(90MHz),精準捕獲測試信號(如電壓、電流波形)。

- 工業(yè)自動化 :伺服驅(qū)動位置反饋、電機控制,利用多器件同步功能與低延遲(3~12ns),實現(xiàn)多軸運動控制的精準同步采樣。

- 能源與海事 :電網(wǎng)功率質(zhì)量分析、海事設(shè)備信號采集,寬溫特性(-40℃~125℃)與高抗干擾能力,適配惡劣環(huán)境。

六、訂單與封裝信息

| 型號 | 封裝 | 采樣速率 | 包裝方式 | RoHS 合規(guī) | 工作溫度 |

|---|---|---|---|---|---|

| ADS9117RHAR | 40 引腳 VQFN | 5MSPS | 2500 片卷帶(大) | 是 | -40℃~125℃ |

| ADS9118RHAR | 40 引腳 VQFN | 10MSPS | 2500 片卷帶(大) | 是 | -40℃~125℃ |

| ADS9119RHAR | 40 引腳 VQFN | 20MSPS | 2500 片卷帶(大) | 是 | -40℃~125℃ |

三款型號引腳完全兼容,僅采樣速率與帶寬差異,可根據(jù)項目需求靈活替換,無需修改 PCB 布局。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

adc

+關(guān)注

關(guān)注

100文章

7511瀏覽量

555926 -

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

4013瀏覽量

130100 -

基準電壓

+關(guān)注

關(guān)注

3文章

115瀏覽量

24164 -

高頻信號

+關(guān)注

關(guān)注

1文章

165瀏覽量

22784 -

集成驅(qū)動器

+關(guān)注

關(guān)注

0文章

44瀏覽量

5629

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

使用 18 位 SAR ADC ADS8881的高性能數(shù)據(jù)采集系統(tǒng)相關(guān)技術(shù)資料下載

功率:AVDD = 5V 時為 35mW利用 ADS8881(18 位,1Msps SAR

發(fā)表于 07-13 14:19

高性能DAQ系統(tǒng)的ADC電壓基準兩級緩沖器優(yōu)化設(shè)計

位 2MSPS SAR ADC)。主要特色兩級緩沖器設(shè)計,用于降低電壓

發(fā)表于 12-07 11:51

一種使用18位SAR ADC ADS8881的高性能數(shù)據(jù)采集系統(tǒng) (DAQ)

緩沖器驅(qū)動器利用由 THS4281 和 OPA333 構(gòu)成的復(fù)合緩沖器在最低功耗下實現(xiàn)所需的性能。 特性:18 位,1

發(fā)表于 09-14 10:34

14位Pipeline ADC設(shè)計的帶隙電壓基準源技術(shù)

14位Pipeline ADC設(shè)計的帶隙電壓基準源技術(shù)

發(fā)表于 04-23 09:42

?4021次閱讀

快速、16 位、5Msps 雙通道 SAR ADC提供了靈活的差分輸入和寬共模范圍

快速、16 位、5Msps 雙通道 SAR ADC提供了靈活的差分輸入和寬共模范圍

發(fā)表于 03-21 16:38

?7次下載

AD7641:18位,2 MSPS SAR ADC數(shù)據(jù)Sheet

AD7641:18位,2 MSPS SAR ADC數(shù)據(jù)Sheet

發(fā)表于 04-16 20:32

?2次下載

ADS921x具有全差分ADC輸入驅(qū)動器的雙路同步采樣18位10MSPS SAR ADC數(shù)據(jù)表

電子發(fā)燒友網(wǎng)站提供《ADS921x具有全差分ADC輸入驅(qū)動器的雙路同步采樣18位10MSPS

發(fā)表于 07-12 09:27

?0次下載

ADS9129 16 位 20MSPS SAR ADC,帶 ADC 驅(qū)動器和基準驅(qū)動器技術(shù)手冊

ADS912x是16位高速模數(shù)轉(zhuǎn)換器(ADC)系列,集成了用于ADC輸入的驅(qū)動器。集成的

ADS8671 14位、1MSPS、1通道SAR ADC技術(shù)手冊

該ADS8671和ADS8675屬于基于逐次逼近 (SAR) 模數(shù)轉(zhuǎn)換器 (ADC) 的集成數(shù)據(jù)采集系統(tǒng)系列。這些器件具有高速、高精度

ADS9117 18位5MSPS SAR ADC,帶ADC驅(qū)動器和基準電壓源技術(shù)手冊

ADS9117 18位5MSPS SAR ADC,帶ADC驅(qū)動器和基準電壓源技術(shù)手冊

評論