以下文章來源于OpenFPGA,作者碎碎思OpenFPGA

在游戲、影視和顯示領(lǐng)域,4K 已經(jīng)成為標(biāo)配。而今天,我們就來聊聊——如何用 FPGA 實(shí)現(xiàn) 4K 視頻的輸入輸出與處理。

從 HDMI 1.4 到 HDMI 2.0:瓶頸與突破

目前,大多數(shù)基于 HDMI 的 FPGA 圖像處理方案,通常采用兩種思路:

直接用 FPGA IO 管腳配置為 TMDS 接收/發(fā)送模式,詳見下面鏈接;

https://github.com/Digilent/vivado-library

通過外部 HDMI PHY 收發(fā)芯片,將并行視頻數(shù)據(jù)與 TMDS 信號(hào)互轉(zhuǎn)。

這些方案在 HDMI 1.4 時(shí)代已經(jīng)相當(dāng)成熟,能夠?qū)崿F(xiàn):

最高 4K@24Hz 視頻輸入輸出

或者 1080p@120Hz 的高幀率顯示

這樣的性能足以滿足多數(shù)中低速應(yīng)用,比如工業(yè)檢測、嵌入式顯示屏等。

但問題來了——

要實(shí)現(xiàn)更流暢的 4K@60Hz 視頻傳輸,就必須邁入 HDMI 2.0 時(shí)代。

挑戰(zhàn):18 Gbps 的帶寬壓力

HDMI 2.0 標(biāo)準(zhǔn)要求帶寬高達(dá) 18 Gbps,這遠(yuǎn)遠(yuǎn)超過傳統(tǒng) FPGA I/O 能承受的速率。

而在這類高帶寬設(shè)計(jì)中,高速串行收發(fā)器(GTH/GTY) 就成了關(guān)鍵。

在這方面,AMD Artix UltraScale+ FPGA 表現(xiàn)亮眼。 它內(nèi)部集成的 GTH 收發(fā)器 可支持 最高 6 Gbps 的速率,完全能勝任 4K@60Hz 的傳輸需求。

這也意味著:我們終于能在一塊 FPGA 上,完整跑通 HDMI 2.0 的 4K 視頻鏈路!

架構(gòu)設(shè)計(jì):從輸入到輸出,一氣呵成

本項(xiàng)目的目標(biāo),是構(gòu)建一個(gè)簡潔高效的 4K 視頻直通參考設(shè)計(jì)(Pass-through Design)。

簡單來說,就是——

從相機(jī)或筆記本電腦輸入 HDMI 視頻 → FPGA 處理 → 輸出到顯示器,實(shí)時(shí)顯示高分辨率畫面。

整個(gè)系統(tǒng)由以下幾個(gè)關(guān)鍵模塊組成:

AMD MicroBlaze 軟核處理器

負(fù)責(zé)初始化與配置各個(gè) IP 核;

通過串口菜單提供簡易的系統(tǒng)控制界面;

控制時(shí)鐘發(fā)生器(Clock Wizard)和視頻參數(shù)。

HDMI RX 1.4 / 2.0 子系統(tǒng)

接收來自外部源(相機(jī)/筆記本)的 HDMI 信號(hào);

將 TMDS 信號(hào)解碼為 FPGA 可處理的視頻流格式。

HDMI TX 1.4 / 2.0 子系統(tǒng)

將處理后的視頻流重新編碼為 TMDS 信號(hào);

輸出到 HDMI 顯示設(shè)備(如 4K 顯示器)。

視頻物理層控制器(PHY Controller)

負(fù)責(zé) HDMI 子系統(tǒng)與 FPGA 內(nèi)部 GTH 收發(fā)器之間的接口;

管理數(shù)據(jù)傳輸與時(shí)鐘同步。

視頻測試模式生成器(TPG)

當(dāng)沒有外部視頻輸入時(shí),可自動(dòng)生成測試圖案;

便于驗(yàn)證 HDMI 輸出鏈路是否工作正常。

實(shí)踐:基于 AMD 官方參考設(shè)計(jì)

整個(gè)方案的實(shí)現(xiàn)基于 AMD 官方 HDMI 參考設(shè)計(jì),在此基礎(chǔ)上進(jìn)行了調(diào)整與優(yōu)化:

增加了對(duì) HDMI 2.0 幀率與分辨率的支持;

通過 MicroBlaze 實(shí)現(xiàn)靈活的軟件可配置控制;

充分利用 Artix UltraScale+ 的 GTH 特性,實(shí)現(xiàn)穩(wěn)定的高速傳輸。

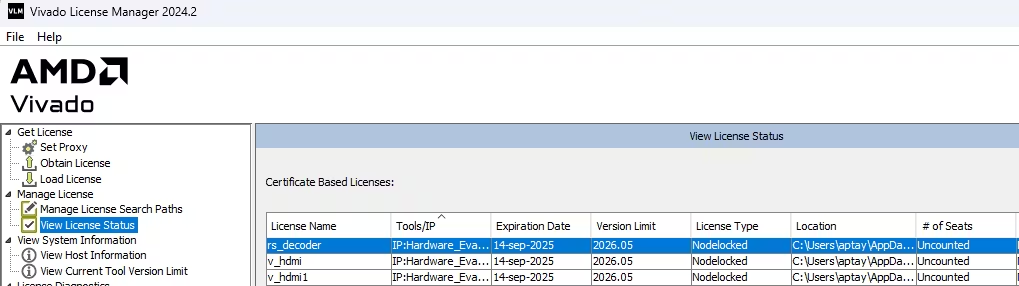

許可

我不清楚我電腦里Vivado為啥都有l(wèi)icense,如果沒有的話可以通過官網(wǎng)申請(qǐng)?jiān)囉茫斠姡?/p>

xilinx_ip_license申請(qǐng)

這里提供一個(gè)網(wǎng)絡(luò)下載的license,我電腦里應(yīng)該時(shí)安裝了這個(gè),大家可以嘗試一下:

分享一波“各種各樣”的資源

創(chuàng)建參考設(shè)計(jì)

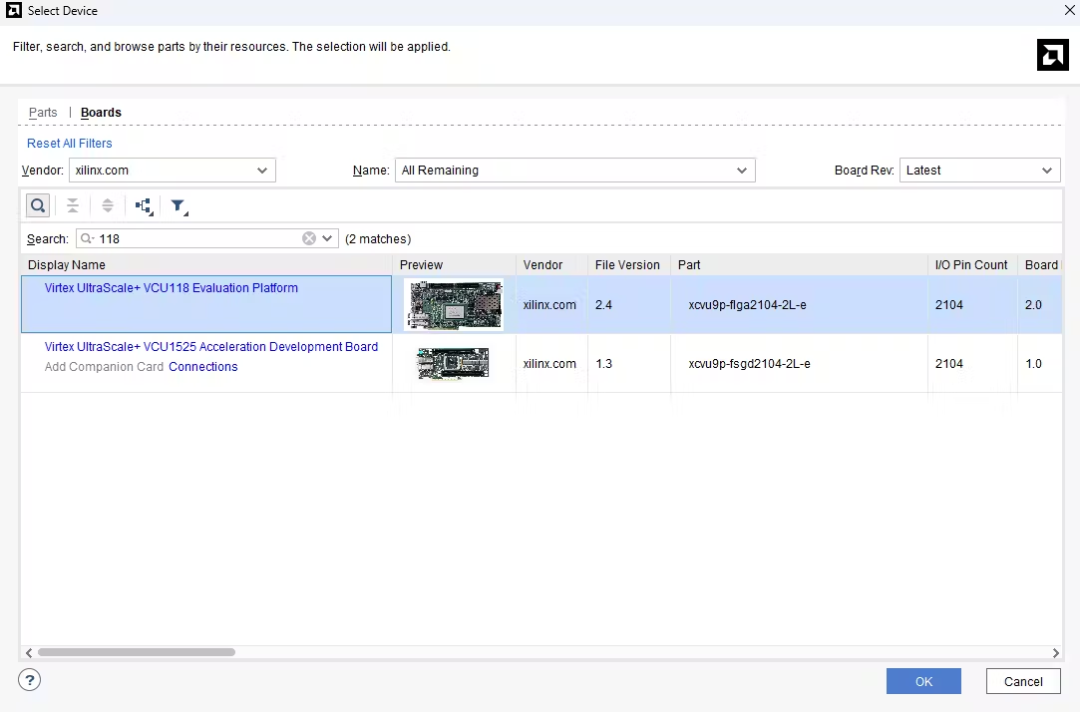

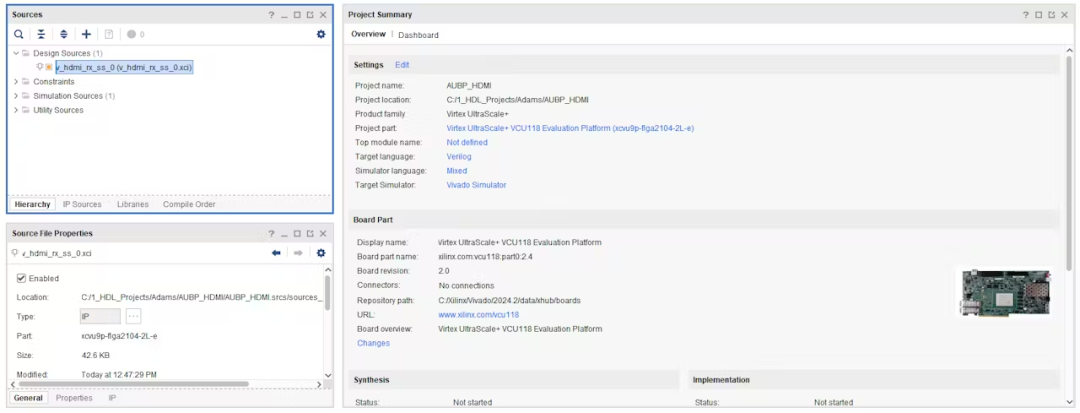

在 AMD Vivado 設(shè)計(jì)套件中創(chuàng)建設(shè)計(jì)之前,我們打開一個(gè)針對(duì) VCU118 的項(xiàng)目。

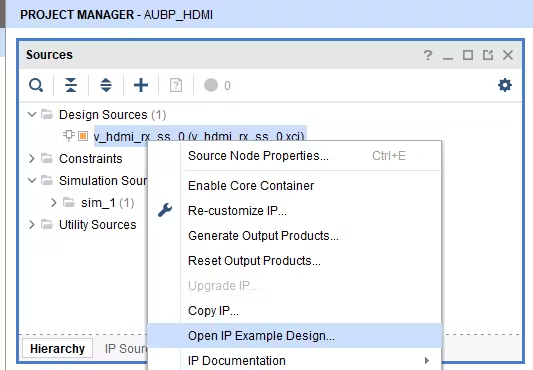

項(xiàng)目打開后,打開 IP 庫并選擇 HDMI 1.4 / 2.0 接收器子系統(tǒng)。

這會(huì)將 IP 添加到項(xiàng)目中。選擇 IP。

右鍵單擊選定的 IP,然后選擇“打開 IP 示例設(shè)計(jì)”。

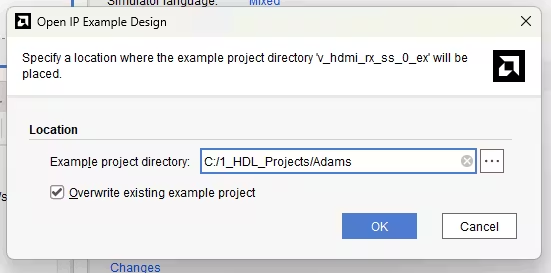

對(duì)話框打開后,選擇要存儲(chǔ)項(xiàng)目的位置。

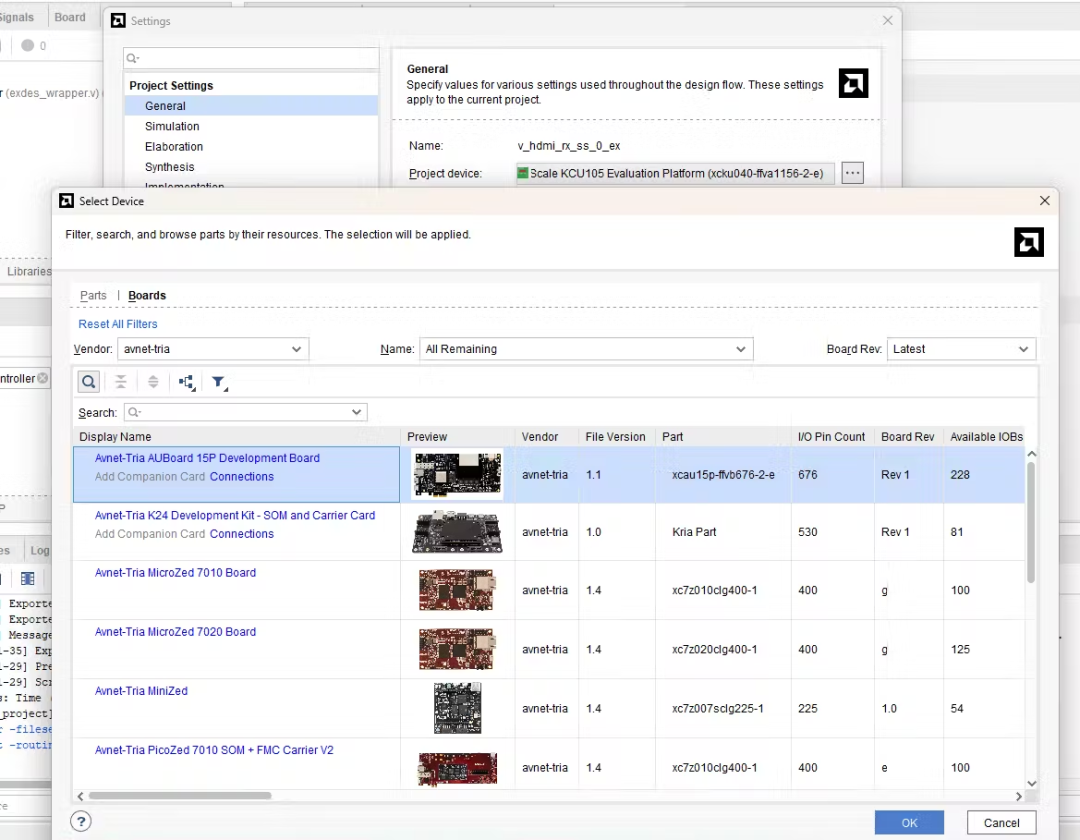

這將打開一個(gè)針對(duì) VCU118 的示例設(shè)計(jì)。我們需要將目標(biāo)板更改為自己的開發(fā)板。

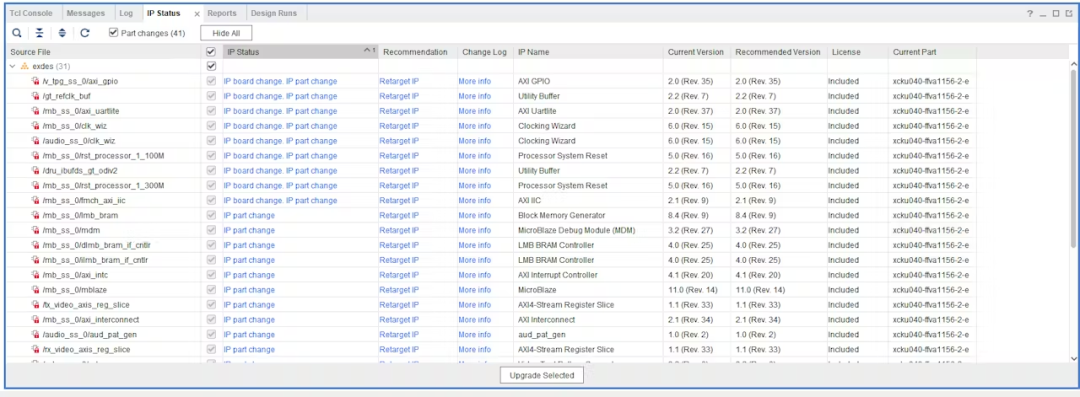

更換FPGA芯片IP會(huì)被鎖定,需要更新:

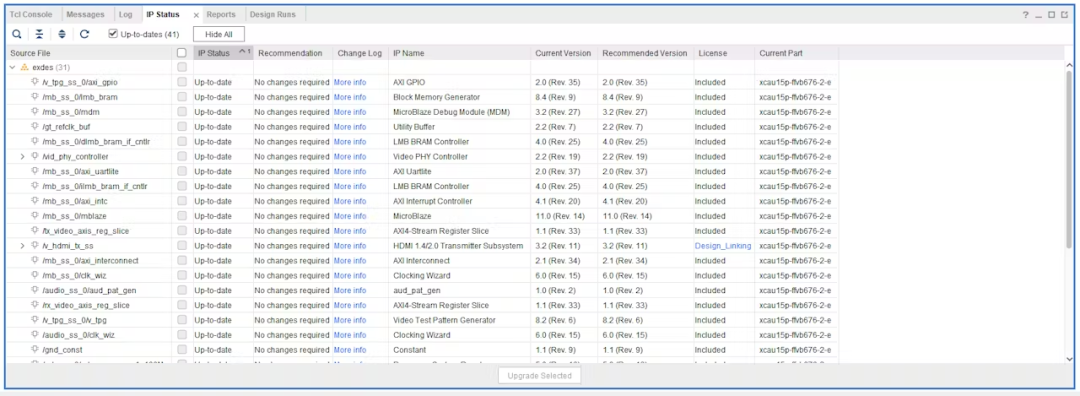

更新選定的 IP 并重新運(yùn)行 IP 狀態(tài)報(bào)告,IP 現(xiàn)在應(yīng)該顯示為最新的。

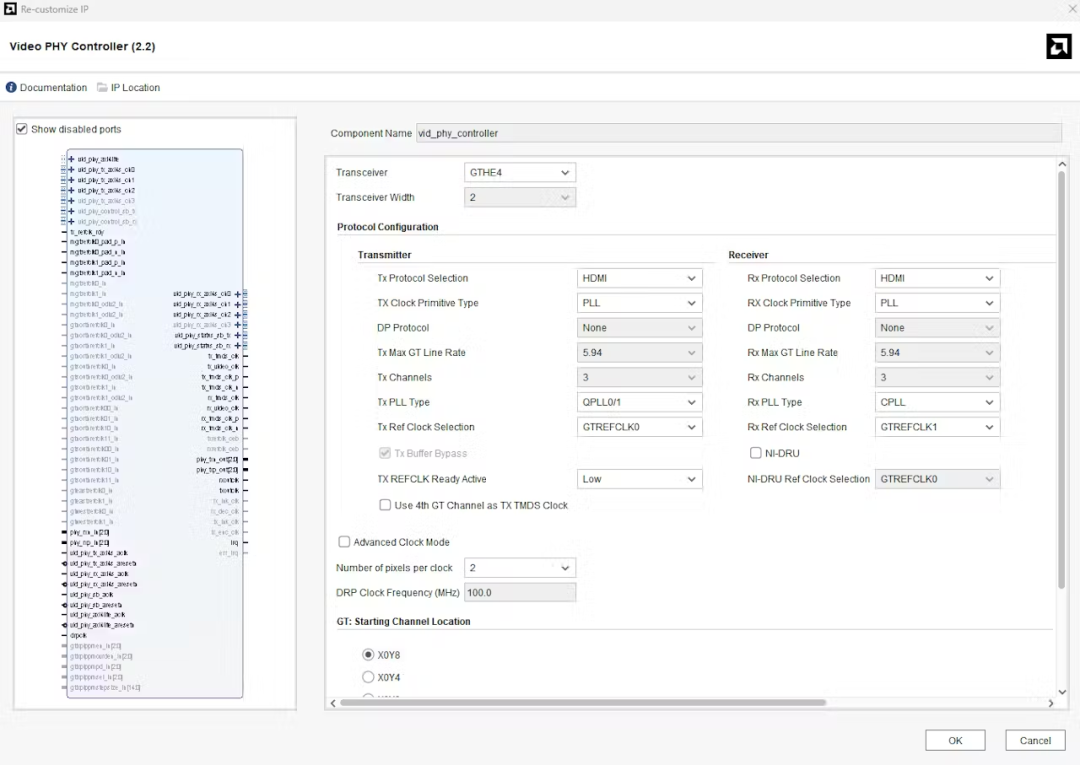

下一步是對(duì)視頻 PHY 控制器進(jìn)行修改,以更新 AMD Artix UltraScale+ 設(shè)備上提供的 GTHE4。確保將時(shí)鐘原語設(shè)置為 PLL。

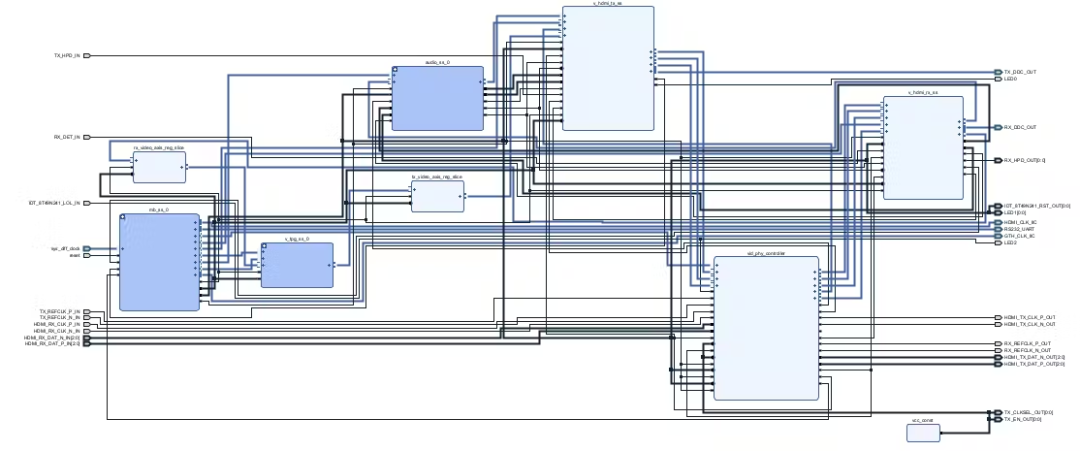

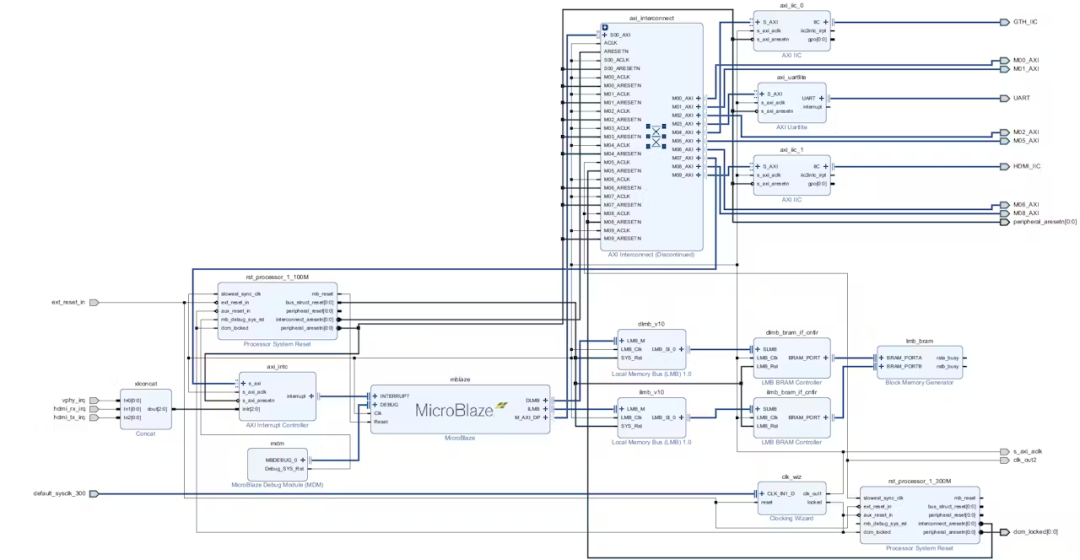

設(shè)計(jì)應(yīng)如下所示。

在本設(shè)計(jì)中,視頻通過 TGP 從 HDMI Rx 傳輸?shù)?HDMI Tx。為了確保能夠支持最高的分辨率和幀率,視頻像素以每時(shí)鐘 2 像素或每時(shí)鐘 4 像素的速率提供(取決于模塊的配置)。

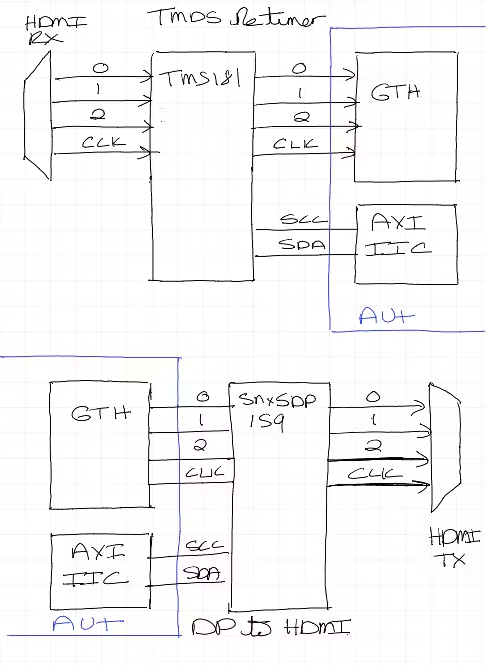

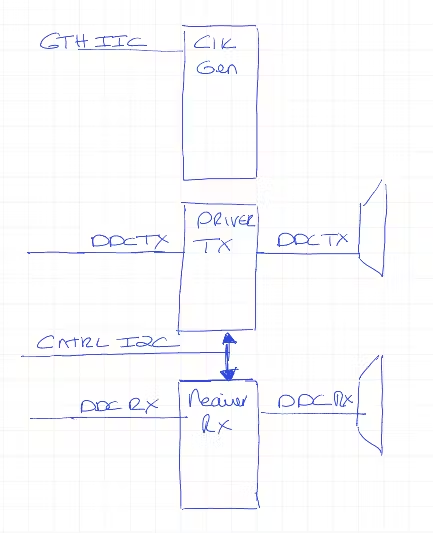

該設(shè)計(jì)的架構(gòu)如下所示。外部傳輸路徑使用 Display Port 轉(zhuǎn) HDMI 轉(zhuǎn)換器,接收器使用 TMDS 重定時(shí)器。

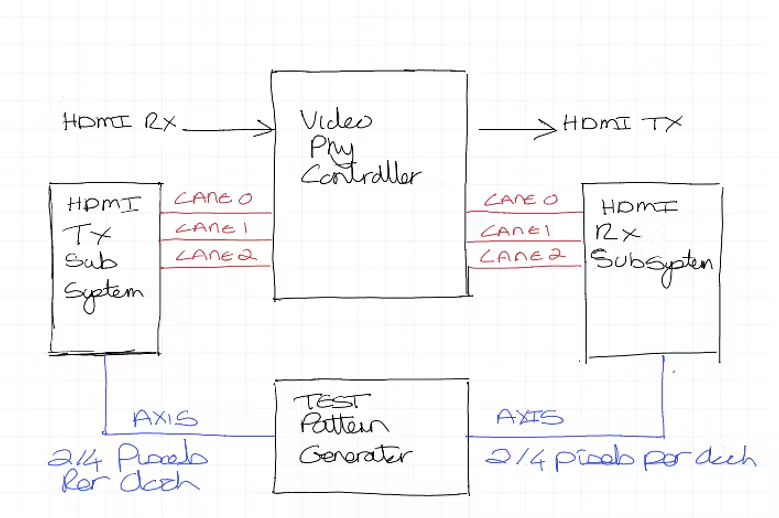

在內(nèi)部,視頻物理層控制器(Video Phy Controller)與 GTH 收發(fā)器相連,用于發(fā)送(Tx)和接收(Rx)操作,并為 HDMI 發(fā)送端和接收端各提供 3 條數(shù)據(jù)通道(data lane)。這些通道與 HDMI 子系統(tǒng)相互連接。

HDMI 解決方案需要多個(gè) IIC 接口用于連接 HDMI Tx 和 Rx 的 DDC,這些 DDC 直接連接或來自 HDMI Tx/Rx 子系統(tǒng)。這些解決方案還需要 IIC 接口用于 SN65DP159RGZT 和 TMS181(驅(qū)動(dòng)和均衡芯片),用于改善輸入和輸出 GTH 信號(hào)。

我們還需要第二個(gè)通道 AXI IIC 連接到時(shí)鐘發(fā)生器。該時(shí)鐘發(fā)生器提供 GTH 參考時(shí)鐘。

本次板卡的 IIC 網(wǎng)絡(luò)如下所示。

在 AMD MicroBlaze 處理器模塊內(nèi),添加第二個(gè) AXI IIC 并將其信號(hào)連接到外部。

修改約束后就可以進(jìn)行綜合實(shí)現(xiàn)了~

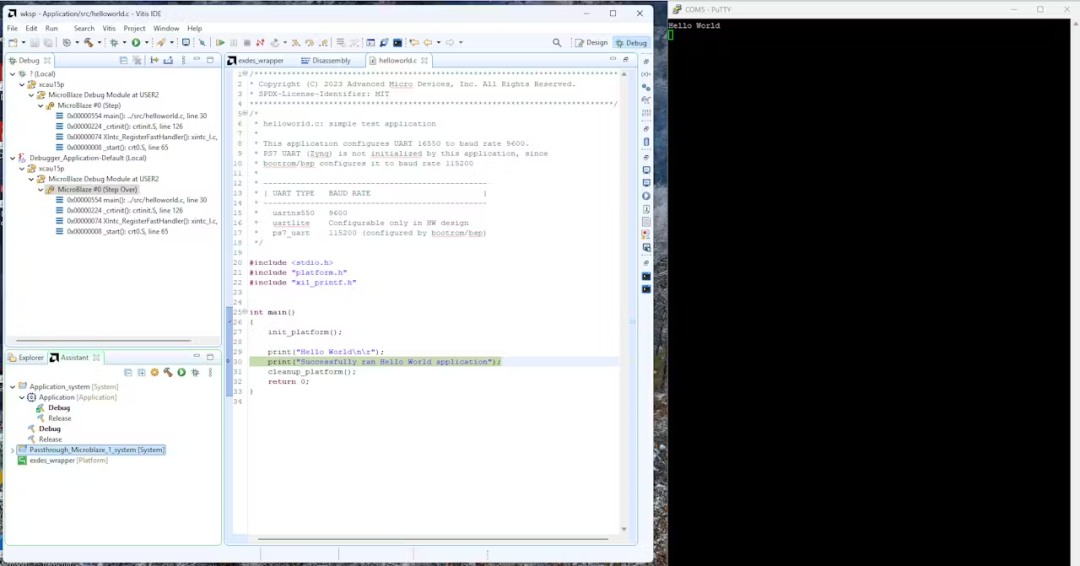

從 AMD Vivado 設(shè)計(jì)套件導(dǎo)出 XSA,有了 XSA,我們可以在 AMD Vitis 統(tǒng)一軟件平臺(tái)中創(chuàng)建一個(gè)簡單的 Hello World 應(yīng)用程序。這個(gè) Hello World 應(yīng)用程序?qū)?chuàng)建一個(gè)平臺(tái)和一個(gè)應(yīng)用程序。編譯并運(yùn)行 Hello World 應(yīng)用程序確保我們能夠在 AMD MicroBlaze 處理器上生成并運(yùn)行應(yīng)用程序。

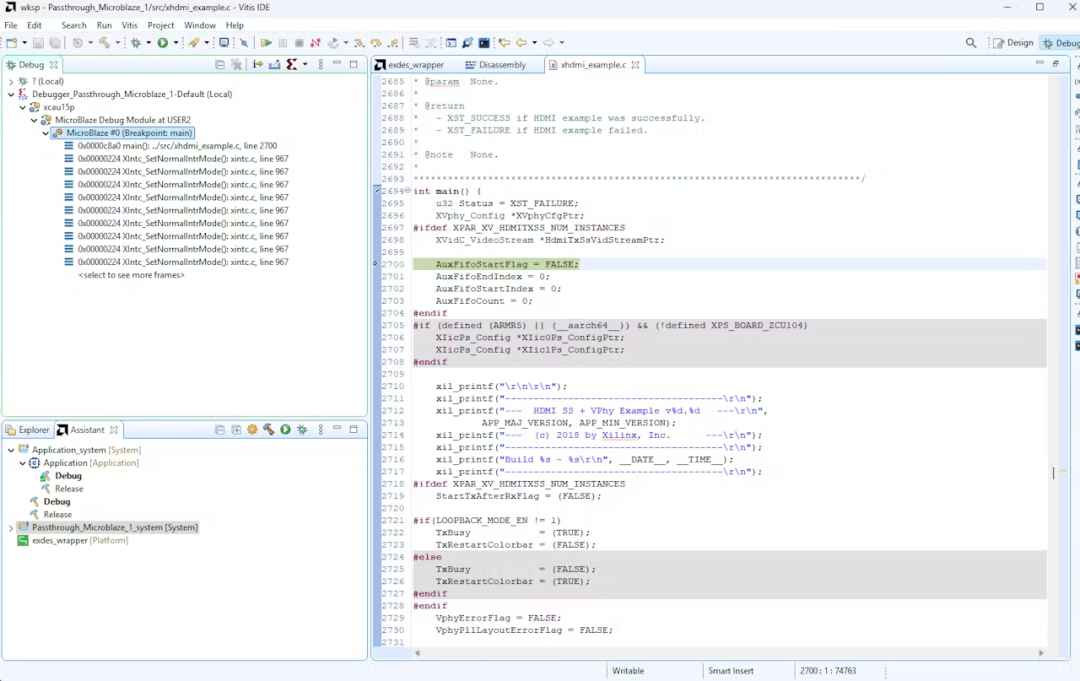

現(xiàn)在我們知道我們有一個(gè)可行的系統(tǒng),并且可以在 AMD MicroBlaze 處理器上執(zhí)行程序,我們需要為 HDMI 直通創(chuàng)建應(yīng)用軟件。

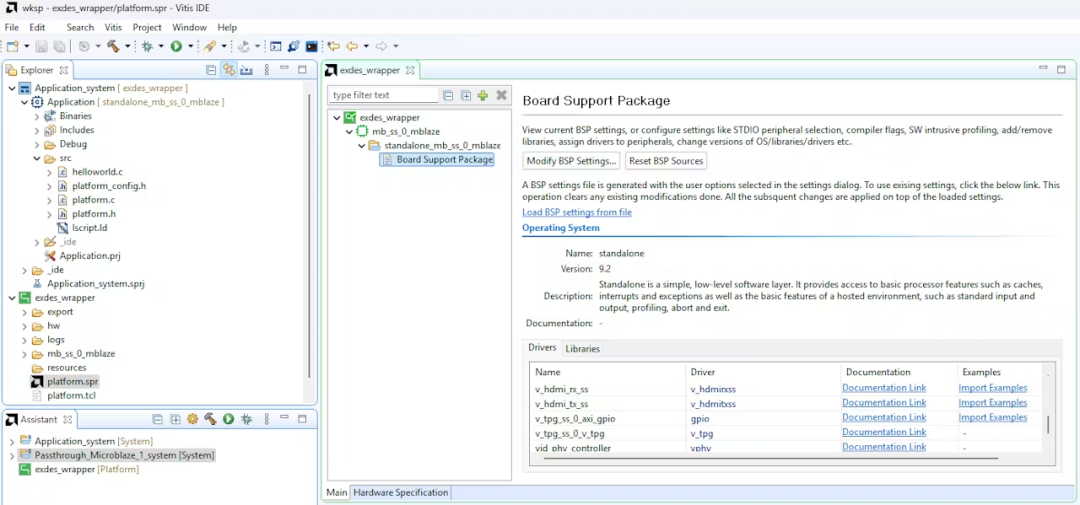

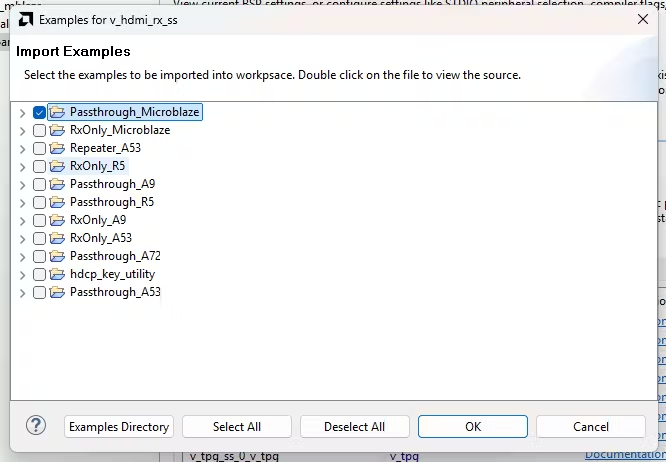

在平臺(tái)中,打開 platform.spr 文件并選擇板級(jí)支持包 (Board Support Package)。在板級(jí)支持包下,向下滾動(dòng)找到 v_hdmi_rx_ss 驅(qū)動(dòng)程序,然后選擇導(dǎo)入示例。

這將為我們提供一系列應(yīng)用示例。在本例中,我們將使用 Passthrough_MicroBlaze。

這樣就創(chuàng)建好了應(yīng)用程序。不過,我們需要對(duì)主應(yīng)用程序示例進(jìn)行一些修改,確保時(shí)鐘發(fā)生器芯片配置正確。

主要的修改是對(duì)條件編譯進(jìn)行修改,更改正在編程的 I2C 時(shí)鐘發(fā)生器類型。默認(rèn)情況下,軟件預(yù)期編程 Si5324 設(shè)備,而 我們的開發(fā)板具有瑞薩 8T49N24 時(shí)鐘發(fā)生器設(shè)備。

int I2cClk(u32 InFreq, u32 OutFreq) { int Status; //#if(!defined XPS_BOARD_ZCU104) #if(defined XPS_BOARD_ZCU104) /* Free running mode */ if(InFreq == 0) { Status = Si5324_SetClock((XPAR_IIC_0_BASEADDR), (I2C_CLK_ADDR), (SI5324_CLKSRC_XTAL), (SI5324_XTAL_FREQ), OutFreq); if(Status != (SI5324_SUCCESS)) { xil_printf("Error programming SI5324 "); return0; } } /* Locked mode */ else{ Status = Si5324_SetClock((XPAR_IIC_0_BASEADDR), (I2C_CLK_ADDR), (SI5324_CLKSRC_CLK1), InFreq, OutFreq); if(Status != (SI5324_SUCCESS)) { xil_printf("Error programming SI5324 "); return0; } } #else /* Reset I2C controller before issuing new transaction. * This is required torecover the IIC controllerincasea previous * transaction is pending. */ XIic_WriteReg(XPAR_IIC_0_BASEADDR, XIIC_RESETR_OFFSET, XIIC_RESET_MASK); /* Free running mode */ if(InFreq == 0) { Status = IDT_8T49N24x_SetClock((XPAR_IIC_0_BASEADDR), (I2C_CLK_ADDR), (IDT_8T49N24X_XTAL_FREQ), OutFreq, TRUE); if(Status != (XST_SUCCESS)) { print("Error programming IDT_8T49N241 "); return0; } } /* Locked mode */ else{ Status = IDT_8T49N24x_SetClock((XPAR_IIC_0_BASEADDR), (I2C_CLK_ADDR), InFreq, OutFreq, FALSE); if(Status != (XST_SUCCESS)) { print("Error programming IDT_8T49N241 "); return0; } } #endif return1; }

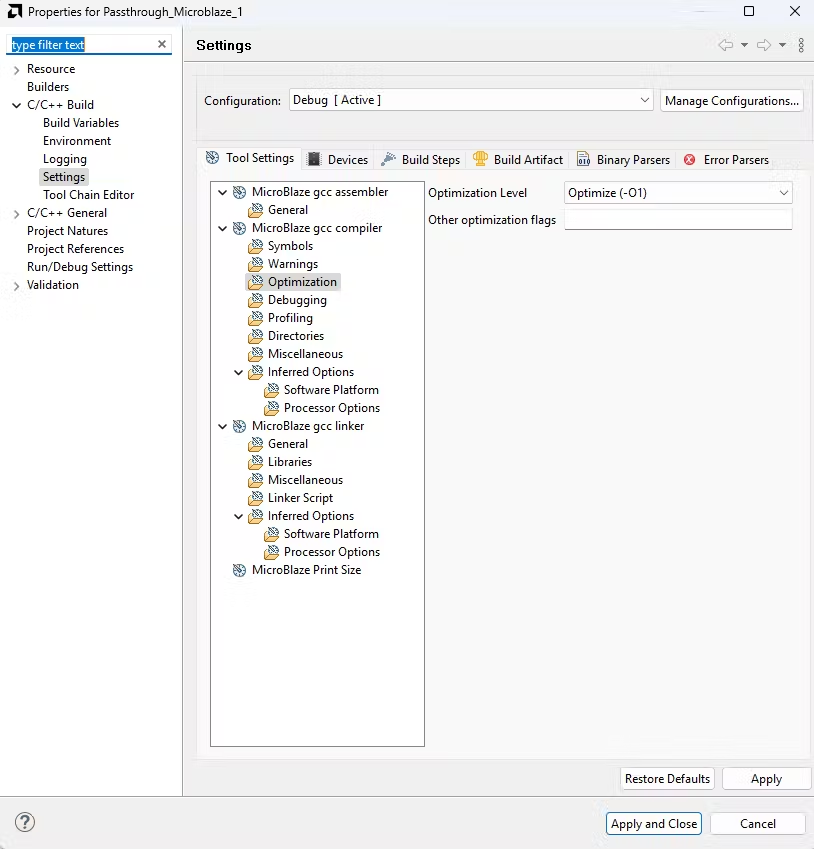

為了確保軟件應(yīng)用程序能夠適應(yīng)所提供的 256KB 內(nèi)存,將優(yōu)化級(jí)別設(shè)置為 O1。

完成這些更改后,我們就可以構(gòu)建應(yīng)用程序并在開發(fā)板上進(jìn)行調(diào)試。完整的源代碼可以在 git 項(xiàng)目中獲取。

https://github.com/ATaylorCEngFIET/4K-at-60Hz

下板測試

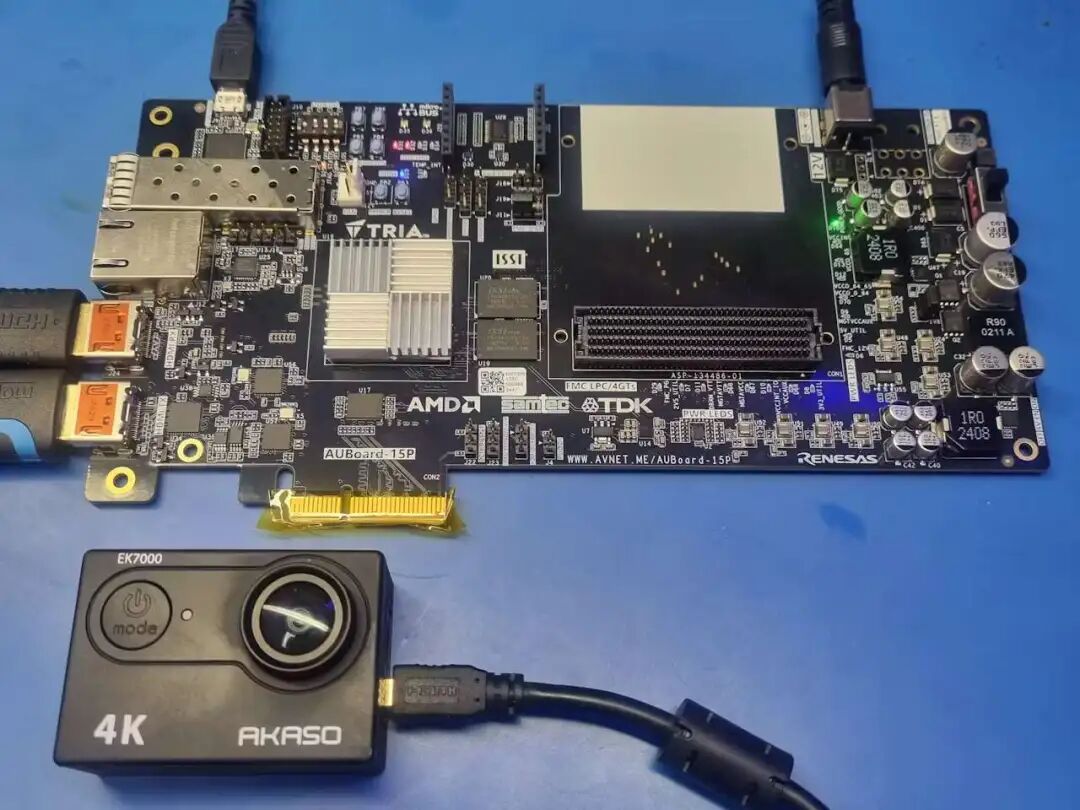

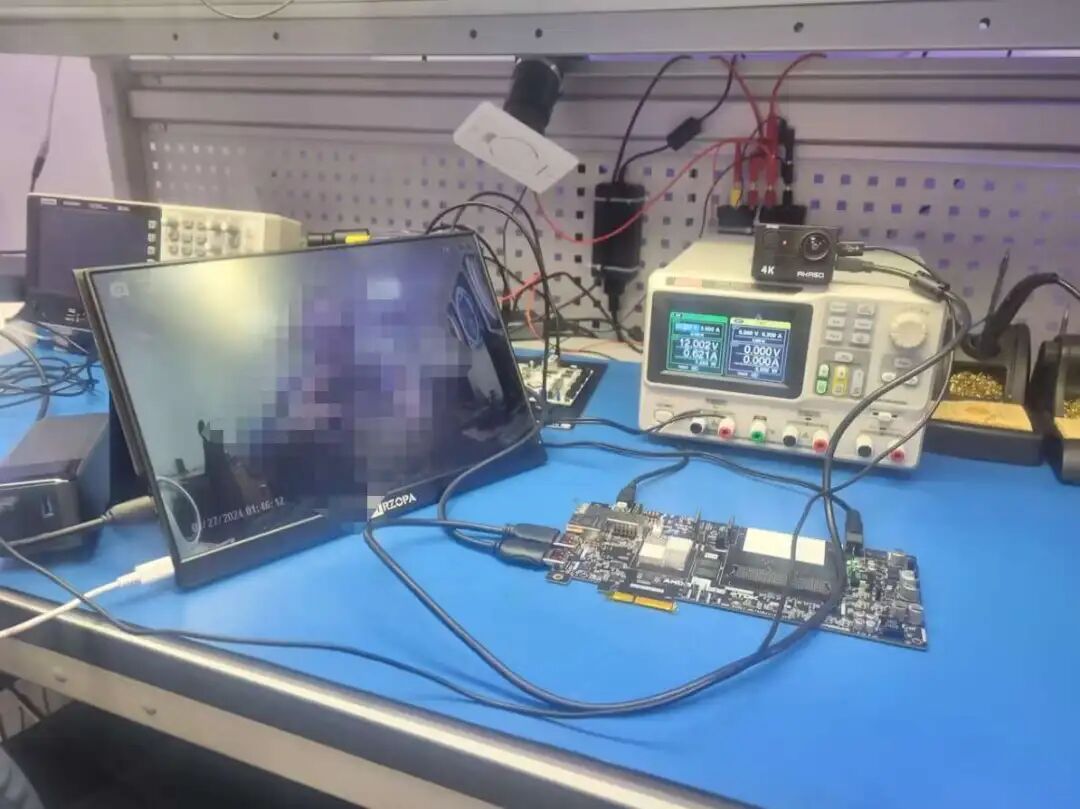

測試非常簡單。我們需要提供一個(gè) HDMI 接收器和一個(gè) HDMI 源。

初始測試的 HDMI 接收器是一臺(tái)支持 4K 的顯示器和一臺(tái)支持 1080p 的小型顯示器。HDMI 源是一臺(tái) 4K 運(yùn)動(dòng)相機(jī),它也可以切換輸出模式。

打開電路板并下載應(yīng)用程序進(jìn)行調(diào)試。

運(yùn)行應(yīng)用程序,將 HDMI 接收器和源連接到攝像頭,并將分辨率設(shè)置為 1080P。它會(huì)顯示正在傳輸?shù)膱D像。

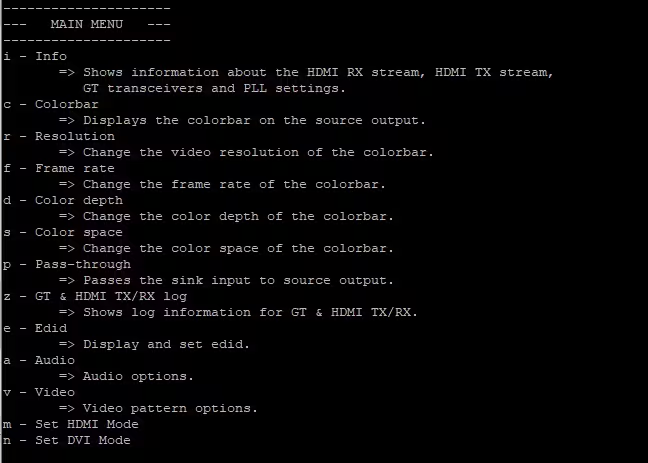

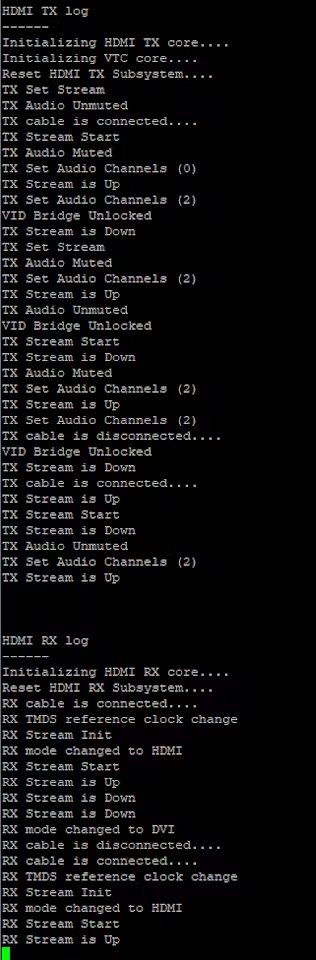

運(yùn)行該應(yīng)用程序?qū)⑼ㄟ^ UART 輸出一個(gè)菜單。通過此菜單,我們可以控制在 AMD MicroBlaze 處理器上運(yùn)行的應(yīng)用程序。此外,我們還可以提取有關(guān)圖像處理流水線的配置和性能的信息。

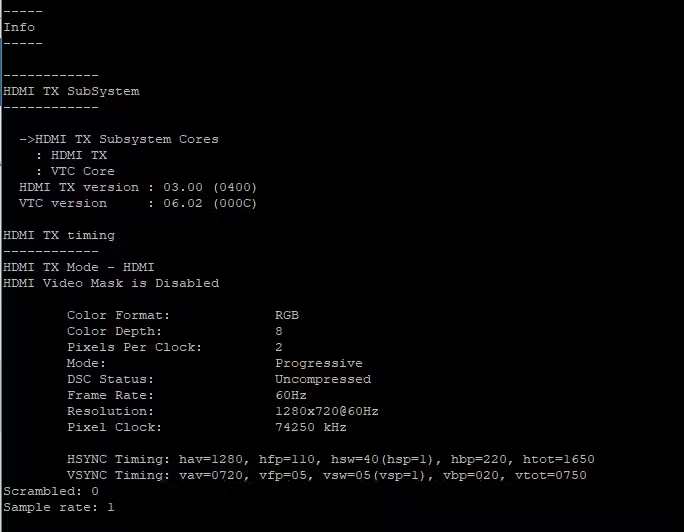

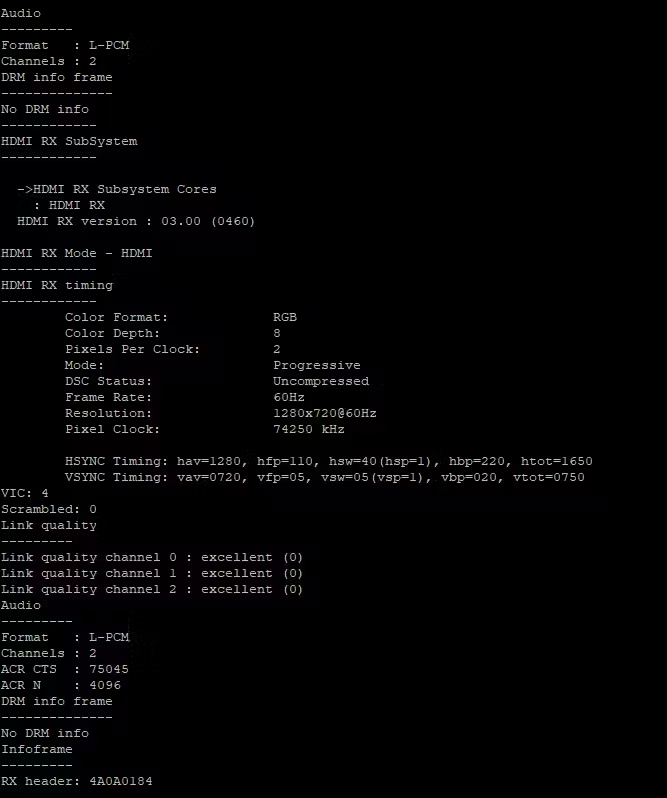

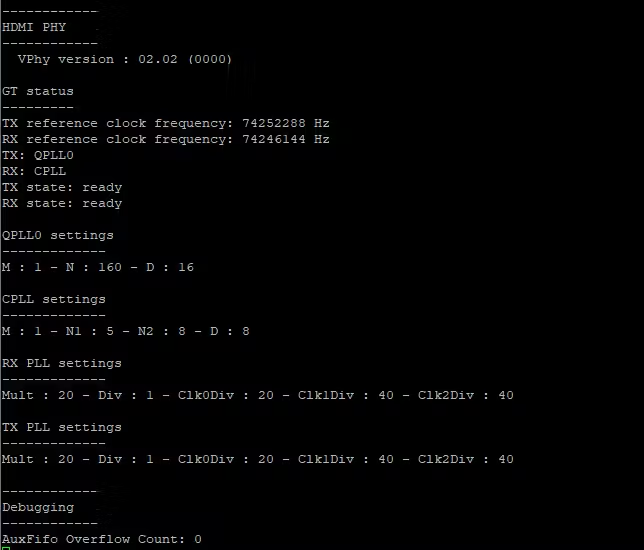

按“i”將提供有關(guān) HDMI TX 和 RX 子系統(tǒng)的信息。

我們還可以通過終端提取 GTH 日志。

將 HDMI 接收器連接到支持 4K 的顯示器后,我們可以看到更新后的分辨率。

最終結(jié)果

這套設(shè)計(jì)能在 FPGA 平臺(tái)上輕松實(shí)現(xiàn) 4K@60Hz 視頻輸入輸出,為高性能視覺系統(tǒng)、視頻采集卡、顯示控制器等應(yīng)用提供了強(qiáng)大支撐。

總結(jié):FPGA,讓 4K 不再遙遠(yuǎn)

過去,4K 視頻處理常被認(rèn)為是 GPU 或?qū)S眯酒摹爸鲌觥薄?但如今,借助 AMD FPGA 強(qiáng)大的可編程邏輯與高速收發(fā)器, 4K@60Hz 視頻系統(tǒng) 已能在單片 FPGA 上靈活實(shí)現(xiàn)。

未來,我們可以想象更多:

視頻疊加、AI 視覺檢測、HDR 動(dòng)態(tài)調(diào)節(jié)……

這些都可以通過硬件邏輯實(shí)時(shí)完成。

參考設(shè)計(jì)

https://github.com/ATaylorCEngFIET/4K-at-60Hz

-

FPGA

+關(guān)注

關(guān)注

1661文章

22442瀏覽量

637468 -

視頻

+關(guān)注

關(guān)注

6文章

2006瀏覽量

75017 -

圖像處理

+關(guān)注

關(guān)注

29文章

1342瀏覽量

59602

原文標(biāo)題:FPGA 玩轉(zhuǎn) 4K 視頻輸入輸出:讓圖像處理更“絲滑”

文章出處:【微信號(hào):FPGA研究院,微信公眾號(hào):FPGA研究院】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

4K H265高清播放開發(fā)板, 支持4K輸入輸出

Thunderbolt 2如何實(shí)現(xiàn)4k視頻分辨率

哪個(gè)FPGA板能夠顯示4k視頻

Spartan 6是否能夠在60hz處理4k的輸入視頻流?

玩轉(zhuǎn)FPGA邊緣視覺——4k視頻圖像抓取

玩轉(zhuǎn)FPGA邊緣視覺——4k視頻圖像抓取

盤點(diǎn)2019最受歡迎的4k視頻軟件

Thunderbolt? 2 如何實(shí)現(xiàn) 4k 視頻分辨率

從高清到4K,矩陣切換器帶你暢享極致視頻體驗(yàn)

使用dp接口播放4K視頻的技巧

HDMI接口如何實(shí)現(xiàn)4K視頻傳輸

RK3576的MIPI CSI-2接口,4K視頻輸入與兼容實(shí)現(xiàn)技巧

如何用FPGA實(shí)現(xiàn)4K視頻的輸入輸出與處理

如何用FPGA實(shí)現(xiàn)4K視頻的輸入輸出與處理

評(píng)論