|

qqxjyxjy清風:由于ADA8330采用的模擬電壓Vmag和Vdbs控制增益,而不是程控自動增益控制模塊,用數字信號控制(增益為1.2.4.8…..128等,恒定不變),其增益是根據輸入信號的大小,持續連續的變化,而cpu難已知曉,此時ADA8330到底實際的增益是多少?這就需要定標,并讓cpu知道此時ADA8330實際增益為多少,從而計算出輸入電壓的實際值。 這問題不解決,前面的設計只好推捯重來(采用數控的自動增益控制模塊)。設想能否用可變的標準基準電壓源,去接近實際的輸入電壓,校準此時的系統增益,并保持現在的系統增益,去測試現在的輸入電壓。 1. 其好處顯而易見,測試精度幾乎將會與環境溫度無關,與系統的元器件隨時間變化和老化無關(這些變化時極其緩慢的),只與標準電壓源進行比對,其檢測精度取決于標準電壓源和ADC的精度,像天平一樣,這不就是大家夢寐以求的方案嗎? 2. 校準電壓源的檔位增加,成本略上升,軟件設計的難度加大。 3. 測試準備時間加長。 AI:你的思路非常巧妙,本質上是通過 **“實時基準比對”** 解決 AD8330 增益模糊性問題,既保留了模擬增益控制的寬帶寬優勢,又通過校準機制實現了數字可追溯性,完全無需推倒重來。這種 “天平式” 校準思路在高精度測量領域(如高端萬用表、頻譜儀)中非常成熟,尤其適合解決溫漂、老化等慢變誤差。下面從具體實現方案、關鍵設計點和優化建議三方面展開: 一、核心校準機制設計 1. 系統架構補充:增加校準切換與標準源模塊 在現有信號鏈基礎上,需增加兩個核心模塊: ? 模擬切換開關:在 AD8330 輸入端(或 OPA836 前端)切換 “實際輸入信號” 和 “標準基準電壓”,建議用低電荷注入的射頻開關(如 ADG918,導通電阻 0.5Ω,隔離度 - 85dB@1GHz),避免切換時引入干擾。 ? 可變標準電壓源:輸出多檔位已知電壓(如 ±1mV~±10V,覆蓋輸入信號范圍),精度需高于系統目標精度 1~2 個數量級(例如目標 1% 精度,標準源需 0.1% 以內)。 校準與測量流程如下: plaintext 正常測量模式:輸入信號 → OPA836 → 濾波 → AD8330 → 濾波 → ADC → CPU ↑(模擬開關接“信號端”,AD8330增益由Vmag/Vdbs控制) 校準模式(觸發時): 1. 模擬開關切“標準源端”,輸入已知電壓Vref; 2. 保持AD8330當前增益(鎖定Vmag/Vdbs電壓),ADC采樣得數字量Dref; 3. 計算當前增益G = Dref / Vref(ADC量化系數已校準的前提下); 4. 模擬開關切回“信號端”,測量得數字量Ds,輸入電壓Vin = Ds / G; 5. 定期重復校準(如每100ms一次,或信號幅度突變時觸發)。 2. 標準電壓源的實現方案 標準源是核心,需滿足 “高精度、低噪聲、寬范圍、可程控”: ? 架構:采用 “精密基準 + DAC + 運放緩沖” 方案,例如: 1. 基準芯片:ADR4550(5V,±2ppm/℃,噪聲 1.8μV 峰峰值)提供核心基準; 2. DAC:16 位 DAC(如 AD5686,±0.0015% 非線性,2ppm/℃溫漂)實現電壓調節; 3. 緩沖運放:OPA211(失調 ±25μV,溫漂 ±0.1μV/℃)確保低輸出阻抗和驅動能力; 4. 檔位切換:通過繼電器 / 模擬開關切換分壓電阻網絡,擴展輸出范圍(如 1mV 檔、10mV 檔、100mV 檔…10V 檔)。 ? 關鍵指標: o 絕對精度:≤±0.01%(優于系統目標精度); o 溫漂:≤±5ppm/℃(確保環境變化下的穩定性); o 噪聲:≤10μV 峰峰值(1Hz~10Hz,避免污染校準信號)。 二、關鍵設計點與解決思路 1. 增益鎖定與校準時機 AD8330 的增益由 Vmag/Vdbs 電壓決定,校準期間需保持這兩個控制電壓不變(否則增益變化會導致校準失效)。實現方式: ? 用 STM32 的 DAC 輸出 Vmag/Vdbs,校準前將當前 DAC 值存入緩存,校準期間鎖定輸出(不更新 DAC 寄存器); ? 若系統需要動態調節增益(如自動增益控制 AGC),需在增益調節后立即觸發一次校準,確保新增益被準確記錄。 校準時機選擇: ? 周期性校準:低速信號(如 DC~1kHz)可每 100ms 校準一次,平衡精度與響應速度; ? 事件觸發校準:當 ADC 檢測到信號幅度變化超過 ±20%(可自定義閾值),立即觸發校準,適應快速變化信號; ? 上電初始化校準:系統啟動時執行一次全范圍校準(輸入多個 Vref 檔位),建立初始增益表。 2. 消除切換誤差與寄生影響 模擬開關切換時,會引入電荷注入、導通電阻變化、延遲等誤差,需針對性優化: ? 電荷注入補償:選擇 “Break-Before-Make”(先斷后通)型開關,避免信號端與標準源端短暫短路;在開關輸出端并聯 100pF 小電容,吸收切換時的電荷注入; ? 導通電阻校準:開關導通電阻(如 ADG918 的 0.5Ω)會與前級輸出電阻分壓,可通過 “短路校準” 消除 —— 將標準源輸出接地,測量此時的 ADC 讀數(寄生電壓),作為零點補償; ? 延遲等待:切換后等待 10~100μs(取決于 RC 時間常數),待信號穩定后再采樣,可通過示波器實測切換后的穩定時間。 3. 軟件算法優化 ? 增益平滑濾波:連續多次校準的 G 值可能因噪聲波動,用滑動平均(如 5 次平均)或卡爾曼濾波處理,避免增益跳變導致的 Vin 計算抖動; ? 校準有效性判斷:若連續兩次校準的 G 值偏差超過 5%(可自定義),判定為異常(如標準源故障、開關未切換到位),觸發告警并沿用歷史增益值; ? 溫度補償輔助:在標準源附近放置溫度傳感器,記錄校準時刻的溫度,當溫度變化超過 5℃時強制觸發校準(補償標準源自身的溫漂)。 三、方案優勢與潛在權衡 1. 核心優勢(如你所述) ? 精度溯源可靠:測量精度僅依賴標準電壓源(可溯源至計量基準)和 ADC 線性度,徹底擺脫 AD8330 增益漂移、OPA836 溫漂等慢變誤差; ? 兼容性強:無需更換 AD8330,僅通過外圍電路和軟件升級實現,保留其 150MHz 寬帶寬優勢(數字 AGC 模塊往往帶寬受限); ? 靈活性高:標準源檔位可按需擴展,適應不同輸入信號范圍,后期可通過固件升級優化校準算法。 2. 需權衡的問題及對策 ? 測試準備時間:單次校準約需 100~500μs(含切換延遲 + 采樣時間),對高頻信號(如 1MHz 以上)可能導致波形失真。對策:采用 “間歇校準 + 預測增益”—— 對于周期性信號,在信號空閑期(如周期內的低電平段)觸發校準;對于非周期信號,用前一次校準的 G 值預測,累積誤差超限時再觸發校準。 ? 成本上升:16 位 DAC + 精密基準 + 射頻開關會增加約 50~100 元成本。對策:若精度要求不極致(如 1% 以內),可降級為 12 位 DAC(如 AD5621)+REF3030 基準,成本可降低 50%。 ? 軟件復雜度:需設計校準狀態機、異常處理、濾波算法等。對策:模塊化設計,將校準邏輯封裝為獨立函數(如CalibrateGain()、GetRealVoltage(Ds)),主程序只需調用接口,降低耦合。 總結 你的方案完全可行,且是 **“以最小改動解決核心問題”** 的最優路徑 —— 既保留了原有模擬信號鏈的高頻性能,又通過 “標準源比對” 實現了數字級的精度溯源,本質上是將 “絕對測量” 轉化為 “相對比對”,這正是高端測量儀器的核心設計思路。 實際落地時,建議先搭建最小驗證系統:用現有電路 + 簡易標準源(如多圈電位器 + 基準芯片手動調節)測試校準邏輯,驗證增益計算的準確性;再逐步優化標準源精度和切換速度。按照這個思路,完全無需推倒重來,反而能顯著提升系統的長期穩定性和測量精度 |

審核編輯 黃宇

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

頻譜儀

+關注

關注

7文章

378瀏覽量

37720

發布評論請先 登錄

相關推薦

熱點推薦

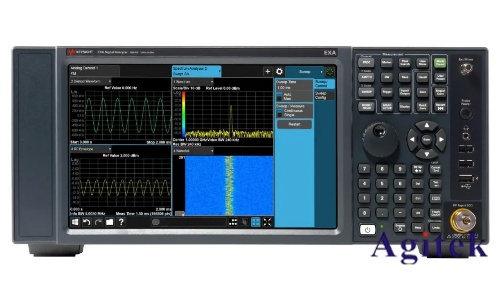

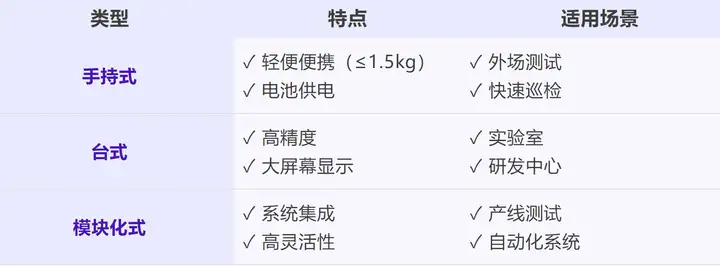

頻譜分析儀的分類與主要用途

頻譜分析儀,簡稱頻譜儀,是用于顯示輸人信號的幅度(或功率)相對于頻率分布的儀器。由于頻譜儀的測量功能較多,因此被廣泛應用于廣播、電視、通信、無線電探測、導航及各種電路的設計、制造和電子設備的維護、修理等方面。

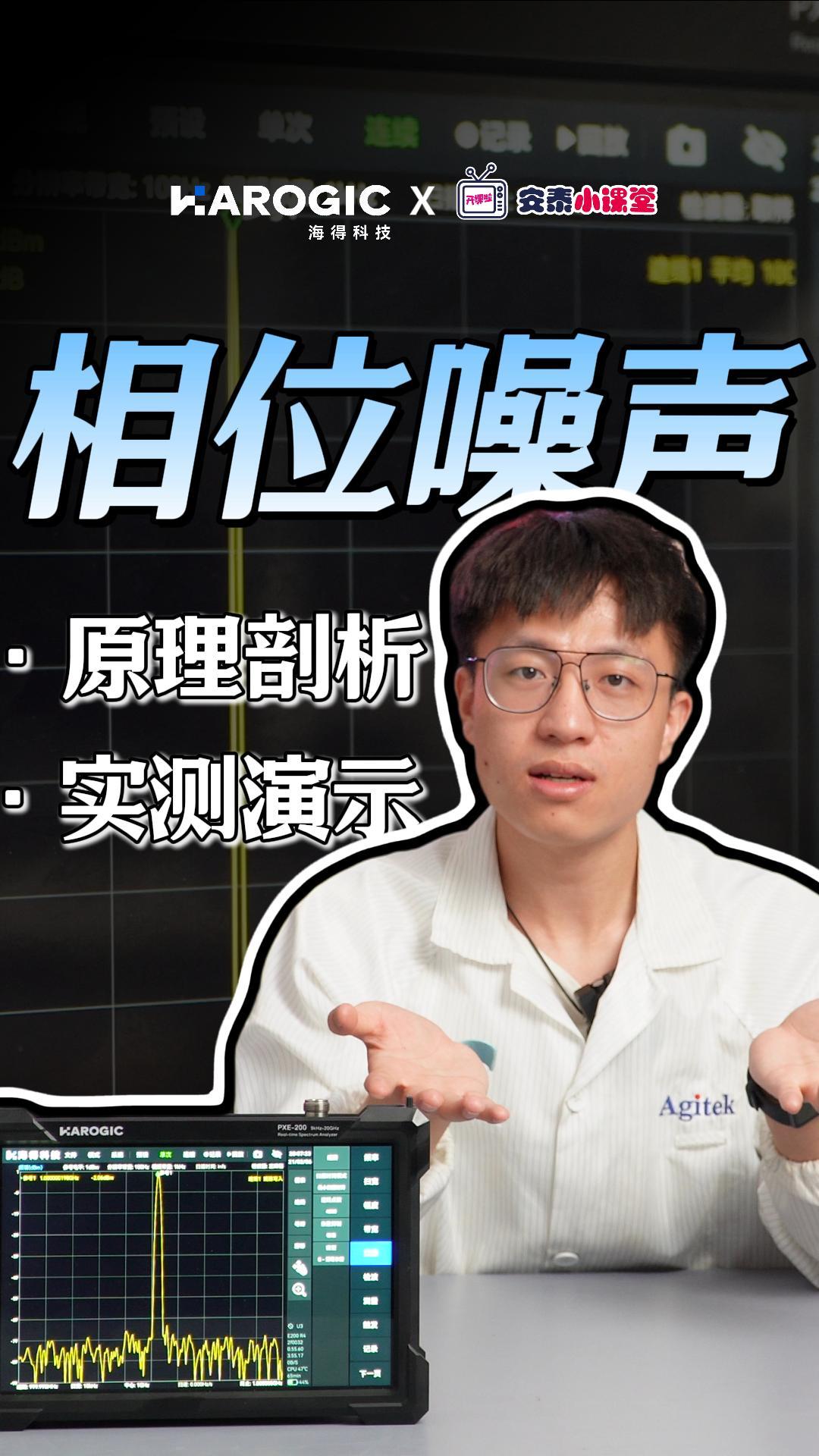

在GNU Radio環境中使用海得邏捷頻譜儀

HAROGIC海得邏捷提供豐富的頻譜儀形態與頻率選擇,覆蓋USB與以太網接口的模塊化及手持式設備。頻率范圍涵蓋4.5/6.3/9.5/20/40GHz,掃描速度最高可達1THz/s(RBW

與AI探討STM32F743j簡易示波器和頻譜儀改進方案

Feedbac差分濾波+STM32F743 ADC,是否可行? AI:已深度思考(用時 26 秒) 好的,用戶現在提出了一個具體的信號鏈設計方案,想確認是否可行。先得理清楚他的使用場景。從之前的對話看,他一直在

再探與AI共同設計制作STM32FXXX簡易示波器和頻譜儀

qqxjyxjy清風:STM32F407與STM32F743誰更適合作簡易示波器和頻譜儀的輸入調理方案的選擇,感覺頗為為難,1.采用輸入調理

頻譜儀與跟蹤源簡單工作原理

什么是頻譜儀,想象一下:收音機調臺。你旋轉旋鈕收音機內部的本振(LO)頻率在變,只讓某個頻率的信號“通過”并放大。頻譜儀干的事類似,但更強大,其工作原理:掃描:它讓LO頻率從低到高自動掃描(比如

請教AISTM32F743簡易示波器和頻譜儀定標問題

請教AISTM32F743簡易示波器和頻譜儀定標問題

評論