AM654x 和 AM652x Sitara? 處理器是 Arm 應用處理器,旨在滿足現代工業 4.0 嵌入式產品的復雜處理需求。

AM654x 和 AM652x 器件將四個或兩個 Arm Cortex-A53 內核與雙 Arm Cortex-R5F MCU 子系統相結合,該子系統包括旨在幫助客戶實現其最終產品功能安全目標的功能,以及三個千兆工業通信子系統 (PRU_ICSSG),以創建能夠為功能安全應用提供工業連接和處理的高性能工業控制的 SoC。AM65xx目前正在接受TüV南德意志集團根據IEC 61508認證的評估。

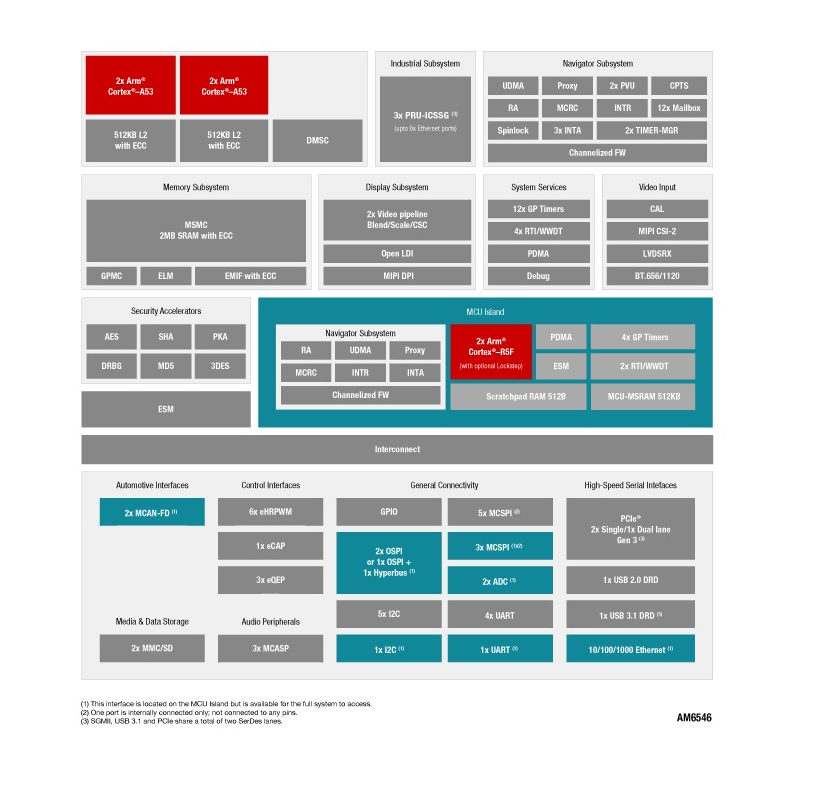

*附件:am6546.pdf

AM654x 中的四個 Arm Cortex-A53 內核排列在兩個具有共享 L2 內存的雙核集群中,以創建兩個處理通道。AM652x 中的兩個 Arm Cortex-A53 內核提供單個雙核集群和兩個單核集群選項。片上存儲器、外設和互連上包含廣泛的 ECC,以確保可靠性。整個 SoC 包括旨在幫助客戶設計能夠實現其功能安全目標的系統的功能(有待 TüV SüD 評估)。除了由 DMSC 管理的粒度防火墻外,某些 AM654x 和 AM652x 設備還提供加密加速和安全啟動。

具有 Arm Neon? 擴展的 Arm Cortex-A53 RISC CPU 提供了可編程性,雙 Arm Cortex-R5F MCU 子系統可作為兩個內核用于通用用途,也可以同步使用,以幫助滿足功能安全應用的需求。PRU_ICSSG子系統可用于提供多達六個工業以太網端口,例如 Profinet IRT、TSN、Ethernet/IP 或 EtherCAT(以及許多其他端口),也可用于標準千兆以太網連接。

TI 為 Arm 內核提供了一套完整的軟件和開發工具,包括處理器 SDK Linux、Linux-RT、RTOS 和 Android,以及 C 編譯器以及用于查看源代碼執行的調試接口。將提供適用的功能安全和安保文檔,以協助客戶開發其功能安全或安保相關系統。

特性

處理器內核:

雙核或四核 Arm Cortex-A53 微處理器子系統,頻率高達 1.1 GHz

雙核 Arm Cortex-R5F,頻率高達 400 MHz

- 支持鎖步模式

- 每個 R5F 內核 16KB ICache、16KB DCache 和 64KB RAM

工業子系統:

三個千兆工業通信子系統 (PRU_ICSSG)

- 每個PRU_ICSSG最多兩個 10/100/1000 以太網端口

- 支持兩個 SGMII 端口 (2)

- 與 10/100Mb PRU-ICSS 兼容

- 每PRU_ICSSG 24× PWM

- 逐周期控制

- 增強的跳閘控制

- 每PRU_ICSSG 18× 個 Σ-δ 濾波器

- 短路邏輯

- 過流邏輯

- 6× 每個PRU_ICSSG的多協議位置編碼器接口

內存子系統:

高達 2MB 的片上 L3 RAM,帶 SECDED

多核共享內存控制器 (MSMC)

- 高達 2MB(2 組 × 1MB)帶 SECDED 的 SRAM

- 共享相干2級或3級內存映射SRAM

- 共享相干的 3 級緩存

- 256 位處理器端口總線和 40 位物理地址總線

- 用于連接到處理器或設備主站的一致統一雙向接口

- L2、L3 緩存預熱和后刷新

- 具有饑餓限制的帶寬管理

- 一個基礎設施主界面

- 單個外部存儲器主接口

- 支持分布式虛擬系統

- 支持內部 DMA 引擎 – 數據路由單元 (DRU)

- ECC 錯誤保護

- 高達 2MB(2 組 × 1MB)帶 SECDED 的 SRAM

DDR 子系統 (DDRSS)

- 支持高達 DDR-1600 的 DDR4 內存類型

- 32位數據總線和7位SECDED總線

- 8 GB 的總可尋址空間

通用內存控制器 (GPMC)功能安全:

符合功能安全標準 [工業]

- 專為功能安全應用而開發

- 可用于幫助 IEC 61508 功能安全系統設計的文檔

- 系統能力高達 SIL 3

- 硬件完整性高達 SIL 2

- 安全相關認證

功能安全特性:

MCU島

- 雙核 Arm Cortex-R5F 微處理器子系統的隔離

- 獨立的電壓、時鐘、復位和專用外設

- 與 SoC 其余部分的內部 MCSPI 連接

安全:

支持安全啟動

- 硬件強制實施的信任根

- 支持通過備份密鑰切換信任根

- 支持接管保護、IP 保護和防回滾保護

支持加密加速

- 會話感知加密引擎,能夠根據傳入數據流自動切換密鑰材料

- 支持加密核心

- AES – 128/192/256 位密鑰大小

- 3DES – 56/112/168 位密鑰大小

- MD5、SHA1

- SHA2 – 224/256/384/512

- DRBG 與真隨機數生成器

- PKA(公鑰加速器)輔助 RSA/ECC 處理

- DMA 支持

調試安全性

- 安全的軟件控制調試訪問

- 安全感知調試

支持可信執行環境 (TEE)

- 基于 Arm TrustZone 的 TEE

- 廣泛的防火墻支持隔離

- 安全的 DMA 路徑和互連

- 安全看門狗/定時器/IPC

安全存儲支持

對 OSPI 接口的動態加密和身份驗證支持

通過基于數據包的硬件加密引擎對數據(有效負載)加密/身份驗證的網絡安全支持

用于密鑰和安全管理的安全協處理器 (DMSC),具有用于安全軟件的專用設備級互連SoC 服務:

設備管理安全控制器 (DMSC)

16 個 32 位通用定時器

兩個數據移動和控制導航子系統 (NAVSS)

- 環形加速器 (RA)

- 統一 DMA (UDMA)

- 多達 2 個定時器管理器 (TM)(每個定時器 1024 個)

多媒體:

顯示子系統

- 兩個完全輸入映射的疊加管理器與兩個顯示輸出相關聯

- 單端口 MIPI DPI 并行接口

- 一個端口 OLDI

PowerVR SGX544-MP1 3D 圖形處理單元 (GPU)

單攝像頭串行接口-2 (MIPI CSI-2)

單端口視頻捕獲:BT.656/1120(無嵌入式同步)高速接口:

一個千兆以太網 (CPSW) 接口支持

- RMII (10/100) 或 RGMII (10/100/1000)

- IEEE1588(2008 年附件 D、附件 E、附件 F)和 802.1AS PTP

- 音頻/視頻橋接 (P802.1Qav/D6.0)

- 節能以太網 (802.3az)

- 巨型幀(2024 字節)

- 第 45 條 MDIO PHY 管理

兩個 PCI-Express (PCIe) 修訂版 3.1 子系統 (2)

- 支持 Gen2 (5.0GT/s)作

- 兩個獨立的 1 通道端口或一個 2 通道端口

- 支持并發根復合體和端點作

USB 3.1 雙角色設備 (DRD) 子系統 (2)

- 一個增強型 SuperSpeed Gen1 端口

- 一個 USB 2.0 端口

- 每個端口可獨立配置為 USB 主機、USB 外設或 USB DRD

一般連接:

5×可配置的UART/IrDA/CIR模塊

兩個同時閃存接口配置為

- 兩個 OSPI 閃存接口

- 或 HyperBus? 和 OSPI1 閃存接口

- 高達 4 Msamples/s

- 八個多路復用模擬輸入

8× 多通道串行外設接口 (MCSPI) 控制器

- 兩個帶內部連接

- 六個帶外部接口

通用 I/O (GPIO) 引腳控制接口:

6×增強型高分辨率脈寬調制器(EHRPWM)模塊

一個增強型捕獲 (ECAP) 模塊

3×增強型正交編碼器脈沖(EQEP)模塊汽車接口:

3× 多通道音頻串行端口 (MCASP) 模塊媒體和數據存儲:

2× 多媒體卡?/安全數字(MMC?/SD)接口簡化的電源管理:

簡化的電源序列,完全支持雙電壓 I/O

集成LDO降低了電源解決方案的復雜性

集成SDIO LDO,用于處理SD接口的自動電壓轉換

集成上電復位 (POR) 生成,降低電源解決方案的復雜性

用于功能安全監控的集成電壓監控器

集成電源毛刺檢測器,用于檢測快速電源瞬變模擬/系統集成:

集成 USB VBUS 檢測

用于 DDR RESET 的故障安全 I/O

所有 I/O 引腳驅動器在復位期間禁用以避免總線沖突

重置期間禁用默認 I/O 拉取以避免系統沖突

支持動態 I/O pinmux 配置更改片上系統 (SoC) 架構:

支持從 UART、I2C、OSPI、HyperBus、并行 NOR 閃存、SD 或 eMMC?、USB、PCIe 和以太網接口進行主啟動

28納米CMOS技術

23 mm × 23 mm、0.8 mm 間距、784 引腳 FCBGA (ACD)

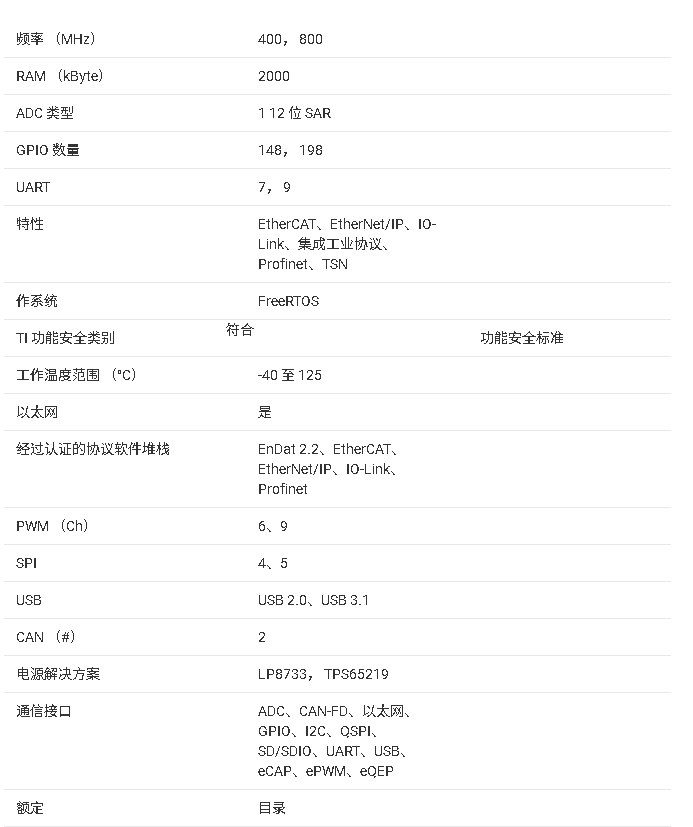

參數

方框圖

?1. 產品概述?

- ?型號系列?:AM6548/AM6528/AM6546/AM6526,基于Arm? Cortex?架構,面向工業4.0應用設計。

- ?核心配置?:

- ?AM654x?:四核Cortex-A53(雙集群)+ 雙核Cortex-R5F(支持鎖步模式)。

- ?AM652x?:雙核Cortex-A53(單集群)+ 雙核Cortex-R5F。

- ?工藝技術?:28nm CMOS,784引腳FCBGA封裝(23mm×23mm)。

?2. 關鍵特性?

- ?工業通信?:集成3個PRU_ICSSG子系統,支持多協議工業以太網(如Profinet IRT、EtherCAT?)。

- ?功能安全?:通過IEC 61508認證(SIL 3系統性能力/SIL 2硬件完整性),支持ECC、防火墻、BIST等安全特性。

- ?高性能接口?:

- DDR4控制器(最高8GB,32位總線)。

- PCIe? 3.1、USB 3.1、千兆以太網(CPSW)。

- 多媒體加速:PowerVR? SGX544-MP1 GPU、雙顯示輸出(MIPI DPI/OLDI)。

?3. 應用場景?

?4. 文檔結構?

- ?功能描述?:詳細說明處理器子系統、內存架構(2MB L3 RAM)、外設(如MCASP、EQEP)。

- ?電氣特性?:涵蓋工作溫度、電壓范圍、功耗及ESD等級。

- ?引腳配置?:784-ball FCBGA封裝引腳定義及復用功能表(如GPIO、UART、SPI等)。

?5. 開發支持?

- 提供Linux/RTOS/Android SDK,配套功能安全與安全認證文檔。

?注?:本文檔為德州儀器(TI)發布的修訂版(SPRSP52C,2023年9月),包含完整的規格參數、設計指南及參考電路。

-

處理器

+關注

關注

68文章

20131瀏覽量

245933 -

mcu

+關注

關注

147文章

18547瀏覽量

384495 -

以太網

+關注

關注

41文章

5901瀏覽量

179344 -

存儲器

+關注

關注

39文章

7710瀏覽量

170723

發布評論請先 登錄

AM1810 Sitara ARM 微處理器

TI推出Sitara微處理器單元Sitara微處理器單元AM

AM6546 Sitara 處理器:四核 Arm Cortex-A53 和雙核 Arm Cortex-R5F,千兆位 PRU-ICSS

AM3874 AM3872 AM3871 Sitara ARM微處理器數據表

AM3715、AM3703 Sitara ARM微處理器數據表

AM335x和AM43xx Sitara處理器USB布局指南

AM335x和AMIC110 Sitara?處理器技術參考手冊

AM6546 Sitara?處理器技術文檔總結

AM6546 Sitara?處理器技術文檔總結

評論