在電子開發(fā)領(lǐng)域,數(shù)字音頻的處理與傳輸是音頻類項(xiàng)目開發(fā)的核心環(huán)節(jié)。I2S(Inter-IC Sound)協(xié)議作為業(yè)界通用的數(shù)字音頻串行接口標(biāo)準(zhǔn),憑借簡潔穩(wěn)定的設(shè)計(jì),為音頻數(shù)據(jù)在集成電路之間的高效傳輸提供了可靠方案。

一、I2S的誕生與應(yīng)用場景

I2S協(xié)議由飛利浦公司率先推出,其核心目標(biāo)是解決不同廠商音頻芯片(IC)間數(shù)據(jù)傳輸?shù)?兼容性難題"——避免因時(shí)序、格式不統(tǒng)一導(dǎo)致的音質(zhì)失真或傳輸失敗。如今,I2S已成為消費(fèi)電子與專業(yè)音頻領(lǐng)域的標(biāo)配接口,典型應(yīng)用場景覆蓋:手機(jī)、平板、筆記本電腦的音頻模塊、藍(lán)牙耳機(jī)、智能音箱、音頻采集卡、數(shù)字調(diào)音臺、Hi-Fi播放器及其他嵌入式音頻開發(fā)項(xiàng)目。

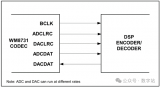

以典型的音頻采集-輸出鏈路為例:麥克風(fēng)將聲音信號轉(zhuǎn)為模擬電壓,經(jīng)運(yùn)放放大后送入ADC(模數(shù)轉(zhuǎn)換器),ADC將模擬信號采樣為數(shù)字信號,此時(shí)ADC與后端DSP/MCU通過I2S協(xié)議傳輸數(shù)字音頻數(shù)據(jù);數(shù)據(jù)經(jīng)DSP處理(如降噪、音效增強(qiáng))后,再通過I2S協(xié)議發(fā)送至DAC(數(shù)模轉(zhuǎn)換器),由DAC還原為模擬信號驅(qū)動喇叭發(fā)聲——I2S協(xié)議貫穿了數(shù)字音頻處理的核心環(huán)節(jié)。

二、I2S的基本信號

I2S協(xié)議通常使用三根或四根信號線。

1. 時(shí)鐘線(SCK/BCLK)

SCK(Serial Clock,串行時(shí)鐘)也常被稱為BCLK(Bit Clock,位時(shí)鐘),是整個I2S傳輸?shù)摹肮?jié)奏控制器”,用于同步每一位數(shù)據(jù)的傳輸時(shí)機(jī)。其頻率直接由音頻的采樣頻率和數(shù)據(jù)位寬決定,計(jì)算公式為:

SCK頻率 = 通道數(shù) × 采樣頻率 × 數(shù)據(jù)位寬

示例:若音頻采樣率為44.1kHz(CD級標(biāo)準(zhǔn)),數(shù)據(jù)位寬為16位,雙聲道,則SCK頻率 = 2 × 44.1kHz × 16 = 1.4112MHz;

2. 左/右聲道選擇線(LRCK/WS)

LRCK(Left-Right Clock,左右聲道時(shí)鐘)又稱WS(Word Select,字選擇線),作用是“標(biāo)記當(dāng)前傳輸?shù)囊纛l數(shù)據(jù)歸屬左聲道還是右聲道”,本質(zhì)是幀同步信號。其核心特性:

- 頻率:與音頻采樣頻率完全一致(如采樣率48kHz時(shí),LRCK頻率也為48kHz);

- 時(shí)序邏輯:通過電平變化區(qū)分聲道——通常低電平時(shí)傳輸左聲道數(shù)據(jù),高電平時(shí)傳輸右聲道數(shù)據(jù)(部分設(shè)備可能反向定義)。

3. 數(shù)據(jù)線(SD/SDATA)

SD(Serial Data,串行數(shù)據(jù)線)是音頻數(shù)據(jù)的“傳輸載體”,根據(jù)數(shù)據(jù)流向分為兩種:

- SDOUT:數(shù)據(jù)發(fā)送端(如ADC、DSP)的串行輸出引腳;

- SDIN:數(shù)據(jù)接收端(如DAC、MCU)的串行輸入引腳。

數(shù)據(jù)傳輸遵循兩大規(guī)則:

- 格式:音頻數(shù)據(jù)以二進(jìn)制補(bǔ)碼形式傳輸,常見位寬為16位(標(biāo)準(zhǔn)音質(zhì))或32位(高解析音質(zhì));

- 傳輸順序:先發(fā)送最高有效位(MSB)——這是I2S協(xié)議的關(guān)鍵設(shè)計(jì):由于不同設(shè)備的數(shù)據(jù)位寬可能不一致(如發(fā)送端16位、接收端24位),先傳輸MSB可確保音頻信號的核心動態(tài)范圍不丟失,避免音質(zhì)劣化。

4. 主時(shí)鐘(MCLK)

主時(shí)鐘MCLK(主時(shí)鐘/系統(tǒng)時(shí)鐘-可選):也稱系統(tǒng)時(shí)鐘。這根線是可選的,用于提供系統(tǒng)級的時(shí)鐘,通常是SCK的整數(shù)倍。如果存在,它可以用于生成SCK和WS。

三、主從工作模式

I2S系統(tǒng)中,設(shè)備需明確主設(shè)備(Master)與從設(shè)備(Slave)角色,核心區(qū)別在于“誰負(fù)責(zé)生成時(shí)鐘信號(SCK)和幀同步信號(LRCK)”。主設(shè)備的核心職責(zé)是提供時(shí)序基準(zhǔn),從設(shè)備則被動跟隨主設(shè)備的時(shí)序傳輸數(shù)據(jù)。實(shí)際開發(fā)中常見三種組合模式:

1. 發(fā)射器為Master,接收器為Slave

- 典型場景:ADC(音頻采集端)作為主設(shè)備,生成SCK和LRCK,DAC(音頻輸出端)作為從設(shè)備,根據(jù)時(shí)序接收數(shù)據(jù);

- 優(yōu)勢:采集端主導(dǎo)時(shí)序,適合"實(shí)時(shí)錄音"類項(xiàng)目(如錄音筆),避免因接收端時(shí)序波動導(dǎo)致的數(shù)據(jù)丟失。

2. 接收器為Master,發(fā)射器為Slave

- 典型場景:D AC(如Hi-Fi播放器的解碼芯片)作為主設(shè)備,生成時(shí)序信號,DSP(音效處理芯片)作為從設(shè)備,按節(jié)奏發(fā)送處理后的音頻數(shù)據(jù);

- 優(yōu)勢:輸出端主導(dǎo)時(shí)序,適合"高保真播放"場景,確保音質(zhì)穩(wěn)定。

3. 發(fā)射器與接收器均為Slave

- 典型場景:系統(tǒng)中存在獨(dú)立的“時(shí)鐘生成模塊”(如專用晶振、FPGA),作為主設(shè)備提供SCK和LRCK,ADC(發(fā)射器)與DAC(接收器)均作為從設(shè)備,協(xié)同完成數(shù)據(jù)傳輸;

- 優(yōu)勢:時(shí)序由獨(dú)立模塊控制,適合多設(shè)備協(xié)同的復(fù)雜音頻系統(tǒng)(如數(shù)字調(diào)音臺),減少設(shè)備間的時(shí)序干擾。

四、數(shù)據(jù)傳輸模式

I2S協(xié)議定義了三種主流數(shù)據(jù)傳輸模式,核心差異在于“LRCK與數(shù)據(jù)的時(shí)序?qū)R方式”,開發(fā)時(shí)需確保發(fā)送端與接收端采用完全一致的模式,否則會出現(xiàn)聲道錯亂或數(shù)據(jù)錯誤。

1. 飛利浦標(biāo)準(zhǔn)(I2S)模式(最常用)

這是業(yè)界默認(rèn)的標(biāo)準(zhǔn)模式,時(shí)序規(guī)則明確:

- 聲道區(qū)分:LRCK低電平 = 左聲道,高電平 = 右聲道;

- 數(shù)據(jù)采樣/發(fā)送沿:數(shù)據(jù)在SCK的下降沿發(fā)送,上升沿采樣(確保數(shù)據(jù)穩(wěn)定后再讀取);

- 時(shí)序延遲:有效數(shù)據(jù)相對于LRCK的跳變沿延遲1個SCK時(shí)鐘周期;

- 對齊方式:數(shù)據(jù)的MSB與LRCK跳變沿延遲1個SCK邊沿對齊。

該模式兼容性最強(qiáng),適合絕大多數(shù)通用音頻芯片(如PCM1808、PCM5102等常用Codec芯片默認(rèn)支持)。

2. 左對齊(左對齊)模式

又稱“MSB對齊模式”,時(shí)序特點(diǎn)與飛利浦標(biāo)準(zhǔn)模式的核心區(qū)別在于“無延遲”:

- 聲道區(qū)分:LRCK高電平 = 左聲道,低電平 = 右聲道(與飛利浦標(biāo)準(zhǔn)反向);

- 采樣/發(fā)送沿:與飛利浦標(biāo)準(zhǔn)一致(SCK下降沿發(fā)送、上升沿采樣);

- 關(guān)鍵差異:有效數(shù)據(jù)相對于LRCK跳變沿?zé)o延遲,且數(shù)據(jù)的MSB與LRCK跳變沿直接對齊。

該模式常見于專業(yè)音頻設(shè)備(如錄音棚設(shè)備),適合對時(shí)序同步精度要求極高的場景。

3. 右對齊(Right Justified)模式

又稱“LSB對齊模式”,時(shí)序邏輯與左對齊模式對稱:

- 聲道區(qū)分:LRCK高電平 = 右聲道,低電平 = 左聲道;

- 采樣/發(fā)送沿:與前兩種模式一致;

- 關(guān)鍵差異:有效數(shù)據(jù)相對于LRCK跳變沿?zé)o延遲,但數(shù)據(jù)的最低有效位(LSB)與LRCK跳變沿對齊。

該模式應(yīng)用場景較少,主要用于部分特定廠商的專用音頻芯片(如某些汽車音響IC),開發(fā)時(shí)需嚴(yán)格對照芯片手冊確認(rèn)模式支持情況。

五、數(shù)據(jù)位寬與位深

位寬與位深是影響音頻音質(zhì)的核心參數(shù),也是I2S協(xié)議配置的關(guān)鍵環(huán)節(jié),二者既相關(guān)又有明確區(qū)別。

1. 位寬(Bit Width)

- 定義:指I2S總線上每一次傳輸?shù)囊纛l數(shù)據(jù)位數(shù)(即SD線上連續(xù)傳輸?shù)亩M(jìn)制位數(shù));

- 常見規(guī)格:16位(主流消費(fèi)電子)、24位(高保真設(shè)備)、32位(專業(yè)級設(shè)備);

- 與時(shí)序的關(guān)聯(lián):直接決定SCK頻率,開發(fā)時(shí)需根據(jù)目標(biāo)音質(zhì)需求設(shè)定,避免位寬過大導(dǎo)致傳輸速率過高,增加系統(tǒng)負(fù)擔(dān)。

2. 位深(位深度)

- 定義:指音頻信號量化時(shí)的精度(即每個采樣點(diǎn)能表示的動態(tài)范圍大小);

- 核心影響:位深越高,音質(zhì)越細(xì)膩(如16位位深可表示65536個音量等級,24位可表示1677萬個等級),但同時(shí)數(shù)據(jù)量也會成倍增加;

- 配置原則:位寬需大于或等于位深(如位深24位時(shí),位寬至少設(shè)為24位),否則會導(dǎo)致數(shù)據(jù)截?cái)啵霈F(xiàn)音質(zhì)失真。

I2S系統(tǒng)的位寬和位深通常由主設(shè)備決定(從設(shè)備被動適配),因此需優(yōu)先配置主設(shè)備的參數(shù),再同步從設(shè)備的設(shè)置。

六、總結(jié)

I2S協(xié)議憑借簡潔的設(shè)計(jì)、靈活的主從模式和穩(wěn)定的時(shí)序邏輯,成為數(shù)字音頻傳輸領(lǐng)域的“標(biāo)桿協(xié)議”。對于開發(fā)者,掌握其核心要點(diǎn)(信號定義、主從模式、傳輸時(shí)序、初始化配置),不僅能解決音頻項(xiàng)目中的"數(shù)據(jù)傳輸兼容性"問題,更能為后續(xù)優(yōu)化音質(zhì)(如提升位深、調(diào)整采樣率)打下基礎(chǔ)。

從實(shí)際開發(fā)場景來看,I2S協(xié)議的應(yīng)用遠(yuǎn)不止“簡單的音頻傳輸”——結(jié)合DSP的音效算法(如EQ調(diào)節(jié)、降噪)、MCU的中斷/DMA機(jī)制(實(shí)現(xiàn)低延遲傳輸),還能打造出更具競爭力的音頻產(chǎn)品(如便攜式Hi-Fi播放器、智能語音交互設(shè)備)。只要理解協(xié)議底層邏輯,并結(jié)合芯片數(shù)據(jù)表細(xì)致調(diào)試,就能讓I2S協(xié)議成為音頻開發(fā)路上的“得力助手”。

-

數(shù)字音頻

+關(guān)注

關(guān)注

9文章

227瀏覽量

68255 -

數(shù)據(jù)傳輸

+關(guān)注

關(guān)注

9文章

2216瀏覽量

67655 -

I2S

+關(guān)注

關(guān)注

1文章

81瀏覽量

44183

發(fā)布評論請先 登錄

音頻總線I2S協(xié)議:I2S收發(fā)模塊FPGA的仿真設(shè)計(jì)

全面解析I2S、TDM、PCM音頻總線

請教PCM1800作為從模式,STM32:I2S 作為主接收模式(帶系統(tǒng)時(shí)鐘輸出)時(shí)DOUT輸出的問題

嵌入式接口通識知識之I2S接口

請問I2S中這四個IC中是依據(jù)什么來設(shè)置主從關(guān)系的?

一文搞懂I2S錄音與播音回環(huán)播放

ADAU1701的I2S主從機(jī)的問題求解

基于FPGA和AD1836的I2S接口設(shè)計(jì)

I2S設(shè)備和MSP430器件的連接指南

I2S、TDM、PCM音頻總線

詳解I2S時(shí)序

從藍(lán)牙音頻模塊中了解I2S的主端和從端功能應(yīng)用

【干貨】一文帶你徹底搞懂數(shù)字音頻PCM接口:從通信基石到多聲道TDM應(yīng)用

【干貨】一文帶你徹底搞懂I2S協(xié)議:從基礎(chǔ)信號到主從模式的深度解析

【干貨】一文帶你徹底搞懂I2S協(xié)議:從基礎(chǔ)信號到主從模式的深度解析

評論