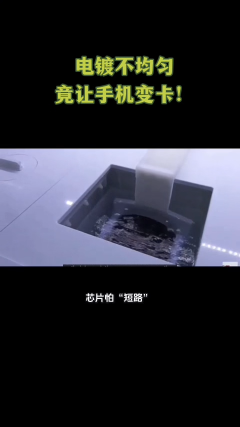

半導體電鍍工藝面臨多重技術挑戰,這些難點源于微觀尺度下的物理化學效應與宏觀工藝控制的相互制約。以下是關鍵難點的深度剖析:

一、均勻性控制困境

在晶圓級制造中,電流密度分布的自然梯度導致邊緣效應顯著。當特征尺寸進入亞微米范疇時,即便微小的電場畸變也會引發沉積速率差異——中心區域因路徑較短可能過早鈍化,而邊緣則因局部高電流過載產生燒蝕現象。這種非理想沉積形態會破壞器件的電學對稱性,尤其對高精度模擬電路的性能匹配造成致命影響。先進封裝中的凸點電鍍進一步放大了該問題,不同直徑焊球需同步實現一致的合金成分與結晶取向,這對電解液傳質效率提出近乎極限的要求。

二、界面結合強度瓶頸

異質材料間的熱膨脹系數失配是嵌入式結構的主要障礙。例如銅互連層與低介電常數介質膜之間的應力積累,可能導致層間剝離或裂紋擴展。更棘手的是,后續高溫工藝(如釬焊回流)會加劇晶格失配引發的位錯滑移,使得初始看似牢固的界面在熱循環載荷下逐漸退化。此外,阻擋層的孔隙率直接決定擴散屏障效能,傳統PVD制備的Ta/Ni薄膜常存在納米級針孔,為金屬離子遷移提供通道。

三、化學穩定性動態失衡

鍍液組分隨時間衰變的不可控性嚴重威脅工藝窗口穩定性。主鹽濃度下降不僅改變溶液電導率,還會移位析出電位;有機添加劑分解產物可能吸附在陰極表面形成絕緣膜;而雜質離子累積則會導致結晶擇優取向改變。實時監控雖能捕捉參數偏移趨勢,但補償機制往往滯后于突變速率——如氯離子突發性超標引發的枝晶突長,可能在數秒內造成短路失效。這種化學體系的混沌特性使得批量生產的一致性成為永恒課題。

四、缺陷檢測與溯源難題

微米級空洞或縫隙類缺陷具有隱蔽性強、分布隨機的特點。傳統光學檢測受限于衍射極限難以識別亞波長尺寸異常,而SEM抽樣檢查又無法覆蓋全域。更復雜的是復合型缺陷:既有可能出現表層完好但內部空心的“蘑菇狀”結構,也可能遇到沿晶界滲透的樹枝狀突起。這類缺陷的形成機理涉及電化學反應動力學、流體力學擾動和晶體生長動力學的耦合作用,單一學科手段難以完成根因分析。

五、設備兼容性矛盾

不同代際工具機的工藝遷移成本高昂。舊型直流電源缺乏脈沖調制功能,無法滿足深寬比結構的底部填充需求;新型矢量控制電源雖能實現波形編輯,卻可能因阻抗匹配問題導致能量傳遞效率下降。反應腔室的材料選擇同樣充滿權衡——不銹鋼耐腐性不足,氟塑料內襯又存在靜電吸附顆粒的風險。當產線引入新設備時,往往需要重新驗證整個工藝鏈的兼容性。

六、環保合規壓力劇增

含氰化物廢液處理已從單純的技術問題演變為法規符合性挑戰。某些地區實施的排水標準要求總氰含量低于0.1ppm,這意味傳統堿性氯化破氰法必須升級為催化加氫深度凈化系統。更嚴峻的是資源回收的經濟可行性困境:從稀薄廢水中萃取貴金屬的成本遠超原材料采購價,迫使企業不得不投入巨資建設閉環回收設施。這種環保投入與經濟效益的矛盾在中小型代工廠尤為突出。

七、先進節點的特殊制約

進入7nm以下制程后,經典電沉積理論開始失效。電子隧穿效應使超薄籽晶層的成核概率驟降,量子尺寸效應導致沉積原子呈現反常擴散行為。此時常規DC電源已無法有效調控沉積過程,必須采用射頻疊加脈沖等特殊波形來突破能壘限制。同時,原子層沉積(ALD)與傳統電鍍的技術融合成為必然趨勢,但兩種機理迥異的工藝如何實現無縫銜接仍是待解之謎。

面對上述挑戰,行業正在探索多維度解決方案:開發具有自修復功能的智能鍍液體系、基于機器學習的實時工藝優化算法、原子級精度的原位監測技術等前沿方向。然而每個突破都需要巨額研發投入與跨學科協作,這恰恰體現了半導體制造作為現代工業皇冠明珠的獨特魅力與殘酷現實。

審核編輯 黃宇

-

半導體

+關注

關注

339文章

30725瀏覽量

264020 -

電鍍

+關注

關注

16文章

477瀏覽量

25725

發布評論請先 登錄

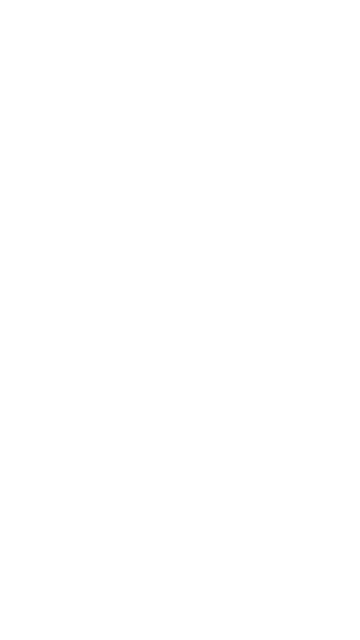

電鍍電源拓撲架構演進與SiC功率模塊及驅動技術的深度價值分析報告

半導體“基礎FMEA和家族?FMEA”分析的詳解;

是德科技Keysight B1500A 半導體器件參數分析儀/半導體表征系統主機

BW-4022A半導體分立器件綜合測試平臺---精準洞察,卓越測量

現代集成電路半導體器件

功率半導體器件——理論及應用

大模型在半導體行業的應用可行性分析

揭秘半導體電鍍工藝

半導體電鍍的難點分析

半導體電鍍的難點分析

評論