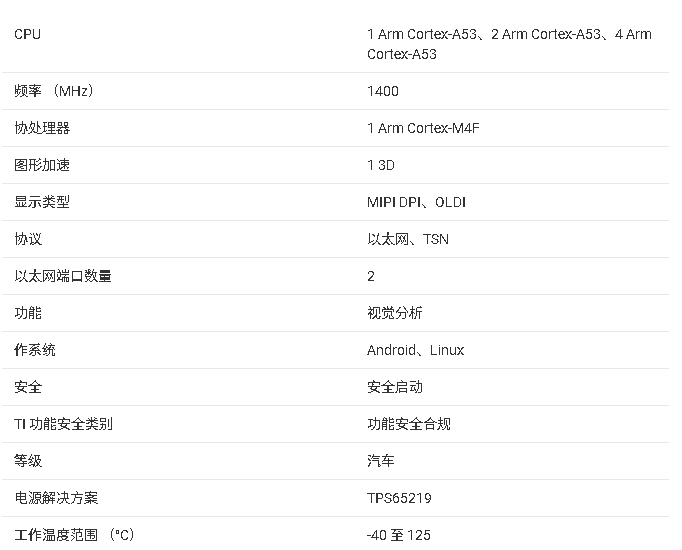

低成本的 AM62x Sitara? MPU 系列應用處理器專為 Linux? 應用開發(fā)而構(gòu)建。憑借可擴展的 Arm? Cortex-A53? 性能和嵌入式功能,例如:雙顯示器支持和 3D 圖形加速,以及廣泛的外設集,使 AM62x 器件非常適合廣泛的工業(yè)和汽車應用,同時提供智能功能和優(yōu)化的電源架構(gòu)。

*附件:am620-q1.pdf

其中一些應用程序包括:

- 工業(yè)人機界面

- 電動汽車充電站

- 非接觸式建筑物訪問

- 駕駛員監(jiān)控系統(tǒng)

AM62x Sitara? 處理器采用 13 x 13 mm 封裝 (ALW) 的工業(yè)級處理器,采用 17.2 x 17.2 mm 封裝 (AMC) 可滿足 AEC - Q100 汽車標準。工業(yè)和汽車功能安全要求可以使用集成的 Cortex-M4F 內(nèi)核和專用外設來滿足,這些外設都可以與 AM62x 處理器的其余部分隔離。

3 端口千兆以太網(wǎng)交換機有一個內(nèi)部端口和兩個支持時間敏感網(wǎng)絡 (TSN) 的外部端口。設備上的附加 PRU 模塊可為客戶自己的用例提供實時 I/O 功能。此外,AM62x 中包含的大量外設可實現(xiàn)系統(tǒng)級連接,例如:USB、MMC/SD、攝像頭接口、OSPI、CAN-FD 和 GPMC,用于與外部 ASIC/FPGA 的并行主機接口。AM62x 器件還支持通過內(nèi)置硬件安全模塊 (HSM) 進行 IP 保護的安全啟動,并為便攜式和功耗敏感型應用采用高級電源管理支持

AM62x 處理器系列產(chǎn)品:

- AM625 – 采用基于 Arm? Cortex-A53? 的邊緣 AI 和全高清雙顯示器的人機交互 SoC

- AM625-Q1 – 用于數(shù)字集群的具有嵌入式安全的汽車顯示 SoC

- AM623 – 思維互聯(lián)網(wǎng) (IoT) 和網(wǎng)關 SoC,具有基于 Arm? Cortex-A53? 的物體和手勢識別功能

- AM620-Q1 – 具有嵌入式安全性的汽車計算 SoC,適用于駕駛員監(jiān)控、網(wǎng)絡和 V2X 系統(tǒng)

特性

處理器內(nèi)核:

- 高達 1.4 GHz 的四通道 64 位 Arm Cortex-A53 微處理器子系統(tǒng)

- 單核 Arm? Cortex-M4F? MCU,頻率高達 400 MHz

- 256KB SRAM,帶 SECDED ECC

- 專用設備/電源管理器

多媒體:

- 顯示子系統(tǒng)

- 3D 圖形處理單元

- 每個時鐘 1 個像素或更高

- 填充率大于 500 Mpixels/sec

500 MTexels/s,>8 GFLOPs

- 支持至少 2 個合成層

- 支持高達 2048x1080 @60fps

- 支持 ARGB32、RGB565 和 YUV 格式

- 支持 2D 圖形

- OpenGL ES 3.1、Vulkan 1.2

- 單攝像頭串行接口 (CSI-Rx) - 帶 DPHY 的 4 通道

內(nèi)存子系統(tǒng):

- 高達 816KB 的片內(nèi) RAM

- DDR 子系統(tǒng) (DDRSS)

- 支持 LPDDR4、DDR4 內(nèi)存類型

- 帶內(nèi)聯(lián) ECC 的 16 位數(shù)據(jù)總線

- 支持高達 1600 MT/s 的速度

- 最大可尋址范圍

- 8GB DDR4

- 4GB 型號,帶 LPDDR4

功能安全:

- 符合功能安全標準 [工業(yè)]

- 專為功能安全應用而開發(fā)

- 將提供文檔以幫助 IEC 61508 功能安全系統(tǒng)設計

- 系統(tǒng)能力高達 SIL 3 目標

- 硬件完整性高達 SIL 2 目標

- 安全相關認證

- TüV SüD計劃通過IEC 61508

- 符合功能安全標準的目標 [汽車]

- 專為功能安全應用而開發(fā)

- 將提供文檔以幫助 ISO 26262 功能安全系統(tǒng)設計

- 系統(tǒng)能力高達 ASIL D 目標

- 硬件完整性達到 ASIL B 目標

- 安全相關認證

- TüV SüD計劃通過ISO 26262

- 符合 AEC - Q100 標準

安全:

- 支持安全啟動

- 硬件強制實施的信任根 (RoT)

- 支持通過備份密鑰切換 RoT

- 支持接管保護、IP 保護和防回滾保護

- 支持可信執(zhí)行環(huán)境 (TEE)

- 專用安全控制器,具有用戶可編程的 HSM 內(nèi)核和專用安全 DMA 和 IPC 子系統(tǒng),用于隔離處理

- 支持加密加速

- 會話感知加密引擎,能夠根據(jù)傳入數(shù)據(jù)流自動切換密鑰材料

- 支持加密核心

- AES – 128/192/256 位密鑰大小

- SHA2 – 224/256/384/512 位密鑰大小

- DRBG 與真隨機數(shù)生成器

- PKA(公鑰加速器)協(xié)助 RSA/ECC 處理以實現(xiàn)安全啟動

- 會話感知加密引擎,能夠根據(jù)傳入數(shù)據(jù)流自動切換密鑰材料

- 調(diào)試安全性

- 安全的軟件控制調(diào)試訪問

- 安全感知調(diào)試

PRU 子系統(tǒng):

- 雙核可編程實時單元子系統(tǒng) (PRUSS),運行頻率高達 333 MHz

- 用于驅(qū)動 GPIO 以實現(xiàn)周期精確協(xié)議,例如其他:

- 每個 PRU 16KB 程序存儲器,帶 SECDED ECC

- 每個 PRU 8KB 數(shù)據(jù)存儲器,帶 SECDED ECC

- 32KB 通用內(nèi)存,帶 SECDED ECC

- CRC32/16 硬件加速器

- 具有 3 組 30 x 32 位寄存器的暫存 PAD 存儲器

- 1 個工業(yè) 64 位定時器,具有 9 個捕獲事件和 16 個比較事件,以及慢速和快速補償

- 1 個中斷控制器 (INTC),至少支持 64 個輸入事件

高速接口:

- 集成以太網(wǎng)交換機支持(總共 2 個外部端口)

- RMII(10/100)或RGMII(10/100/1000)

- IEEE1588(附錄 D、附錄 E、附錄 F,附有 802.1AS PTP)

- 第 45 條 MDIO PHY 管理

- 基于 ALE 引擎的數(shù)據(jù)包分類器,具有 512 個分類器

- 基于優(yōu)先級的流量控制

- 時間敏感型網(wǎng)絡 (TSN) 支持

- 四個 CPU H/W 中斷起搏

- 硬件中的 IP/UDP/TCP 校驗和卸載

- 兩個 USB2.0 端口

- 端口可配置為 USB 主機、USB 外設或 USB 雙角色設備(DRD 模式)

- 集成 USB VBUS 檢測

- 支持通過 USB 進行跟蹤

一般連接:

- 9 個通用異步接收器-發(fā)射器 (UART)

- 5 個串行外設接口 (SPI) 控制器

- 6 個集成電路間 (I 2C) 端口

- 3 個多通道音頻串行端口 (MCASP)

- 發(fā)射和接收時鐘頻率高達 50 MHz

- 3 個 MCASP 上多達 16/10/6 個串行數(shù)據(jù)引腳,具有獨立的 TX 和 RX 時鐘

- 支持時分復用 (TDM)、IC 間聲音 (I2S) 和類似格式

- 支持數(shù)字音頻接口傳輸(SPDIF、IEC60958-1 和 AES-3 格式)

- 用于發(fā)送和接收的FIFO緩沖區(qū)(256字節(jié))

- 支持音頻參考輸出時鐘

- 3 個增強型 PWM 模塊 (ePWM)

- 3 個增強型正交編碼器脈沖模塊 (eQEP)

- 3 個增強型捕獲模塊 (eCAP)

- 通用 I/O (GPIO),所有 LVCMOS I/O 均可配置為 GPIO

- 3 個支持 CAN-FD 的控制器局域網(wǎng) (CAN) 模塊

- 符合 CAN 協(xié)議 2.0 A、B 和 ISO 11898-1

- 完整的 CAN FD 支持(最多 64 個數(shù)據(jù)字節(jié))

- 消息 RAM 的奇偶校驗/ECC 檢查

- 速度高達 8Mbps

媒體和數(shù)據(jù)存儲:

- 3 個多媒體卡/安全數(shù)字 (MMC/SD) 接口

- 1 個 8 位 eMMC 接口,速度高達 HS200

- 2 個 4 位 SD/SDIO 接口,最高可達 UHS-I

- 符合 eMMC 5.1、SD 3.0 和 SDIO 3.0 版

- 1× 通用內(nèi)存控制器 (GPMC),頻率高達 133 MHz

- 靈活的 8 位和 16 位異步存儲器接口,具有多達四個芯片(22 位地址)選項(NAND、NOR、多路復用 NOR 和 SRAM)

- 使用 BCH 代碼支持 4 位、8 位或 16 位 ECC

- 使用漢明碼支持 1 位 ECC

- 錯誤定位器模塊 (ELM)

- 與 GPMC 一起使用,用于從使用 BCH 算法生成的綜合多項式中查找數(shù)據(jù)錯誤的地址

- 支持基于BCH算法的每512字節(jié)塊錯誤位置4位、8位和16位

- 支持 DDR / SDR 的 OSPI/QSPI

- 支持串行 NAND 和串行 NOR 閃存設備

- 4GBytes 內(nèi)存地址支持

- 具有可選動態(tài)加密的 XIP 模式

電源管理:

- 設備/電源管理器支持的低功耗模式

- 部分 IO 支持 CAN/GPIO/UART 喚醒

- 深度睡眠

- 僅MCU

- 待機

- Cortex-A53 的動態(tài)頻率縮放

最佳電源管理解決方案:

- 推薦TPS65219電源管理IC(PMIC)

- 專為滿足設備電源要求而設計的配套 PMIC

- 靈活的映射和工廠編程配置,以支持不同的用例

啟動選項:

- UART

- I 2C EEPROM

- OSPI/QSPI 閃存

- GPMC NOR/NAND 閃存

- 串行 NAND 閃存

- SD卡

- eMMC的

- USB(主機)從大容量存儲設備啟動

- USB(設備)從外部主機啟動(DFU 模式)

- 以太網(wǎng)

技術/封裝:

- 16 納米技術

- 13 mm x 13 mm,0.5 mm 間距,425 引腳 FCCSP BGA (ALW)

- 17.2 mm x 17.2 mm,0.8 mm 間距,441 引腳 FCBGA (AMC)

參數(shù)

方框圖

?1. 核心特性?

- ?處理器核心?:

- 四核/雙核/單核64位Arm? Cortex?-A53,主頻高達1.4 GHz,配備512KB共享L2緩存(帶SECDED ECC)。

- 單核Arm? Cortex?-M4F MCU,主頻400 MHz,256KB SRAM(帶SECDED ECC)。

- ?多媒體?:

- 雙顯示支持(最高1920x1080@60fps),3D圖形加速(OpenGL ES 3.1/Vulkan 1.2)。

- MIPI CSI-2攝像頭接口(4通道,支持1.5Gbps速率)。

- ?內(nèi)存子系統(tǒng)?:

- 支持LPDDR4/DDR4(16位數(shù)據(jù)總線,帶ECC),最大8GB(DDR4)或4GB(LPDDR4)。

- 片上RAM:816KB(多區(qū)域分布,均帶ECC保護)。

- ?功能安全?:

- 工業(yè)級:符合IEC 61508(目標SIL 3系統(tǒng)性能力/SIL 2硬件完整性)。

- 車規(guī)級:符合ISO 26262(目標ASIL D系統(tǒng)性能力/ASIL B硬件完整性),AEC-Q100認證。

?2. 關鍵外設與接口?

- ?高速接口?:

- 集成2端口千兆以太網(wǎng)交換機(支持TSN、IEEE1588)。

- USB 2.0雙端口(主機/設備/DRD模式)。

- ?通用連接?:

- ?安全與存儲?:

- 安全啟動(硬件強制信任根)、加密加速(AES/SHA2/DRBG/PKA)。

- OSPI/QSPI閃存接口(支持XIP模式加密)。

?3. 應用場景?

- ?工業(yè)與汽車?:

- 人機界面(HMI)、車載信息娛樂(IVI)、駕駛員監(jiān)控系統(tǒng)(DMS)、V2X通信。

- ?消費與物聯(lián)網(wǎng)?:

- 零售自動化、醫(yī)療設備、智能家居網(wǎng)關。

?4. 封裝與電源?

- ?封裝選項?:

- 13x13mm FCCSP BGA(425球,工業(yè)級)。

- 17.2x17.2mm FCBGA(441球,車規(guī)級)。

- ?電源管理?:

- 支持低功耗模式(DeepSleep/Standby),推薦配套PMIC TPS65219。

?5. 文檔與支持?

-

處理器

+關注

關注

68文章

20300瀏覽量

253740 -

嵌入式

+關注

關注

5204文章

20560瀏覽量

335904 -

soc

+關注

關注

40文章

4601瀏覽量

229677 -

主機接口

+關注

關注

0文章

18瀏覽量

9511

發(fā)布評論請先 登錄

如何保證汽車遠程信息系統(tǒng)的安全性

如何利用嵌入式雷達技術提升汽車主動安全性?

嵌入式視覺中要考慮哪些安全性與保密性?

如何提升嵌入式系統(tǒng)的VxWorks安全性?

嵌入式實時多任務操作系統(tǒng)的安全性怎么樣?

嵌入式設備如何提高安全性

嵌入式機載軟件安全性的相關資料分享

嵌入式系統(tǒng)的安全性

汽車嵌入式SoC系統(tǒng)的應用與發(fā)展

基于SCADE模型的高安全性嵌入式軟件解決方案設計

針對嵌入式設備安全實現(xiàn)更強大IoT設備安全性

InBOX620工業(yè)級嵌入式計算平臺

AM625/AM623/AM625SIP/AM625-Q1/AM620-Q1系列處理器硬件設計指南

AM625-Q1用于數(shù)字集群的嵌入式安全的汽車顯示 SoC技術手冊

AM620-Q1 具有嵌入式安全性的汽車計算 SoC技術文檔總結(jié)

AM620-Q1 具有嵌入式安全性的汽車計算 SoC技術文檔總結(jié)

評論