CDC208包含雙時鐘驅動器電路,可將一個輸入信號扇出到四個輸出,時鐘分配的偏斜最小(見圖2)。該器件還為每個電路提供兩個輸出使能(OE1和OE2)輸入,可以強制將輸出禁用到高阻抗狀態或高或低邏輯電平,而與相應A輸入上的信號無關。

偏斜參數是針對許多應用中常見的降低溫度和電壓范圍指定的。

CDC208 的工作溫度為 -40°C 至 85°C。

*附件:cdc208.pdf

特性

- 時鐘驅動器應用的低偏斜傳播延遲規范

- TTL兼容輸入和CMOS兼容輸出

- 流通架構優化了

PCB布局 - 中心引腳 V

CCGND 引腳配置可最大限度地降低高速開關噪聲 - 史詩 ^TM的^ (增強型植入式CMOS)1-um工藝

- 125°C時典型閂鎖抗擾度為500 mA

- 封裝選項包括塑料小外形 (DW)

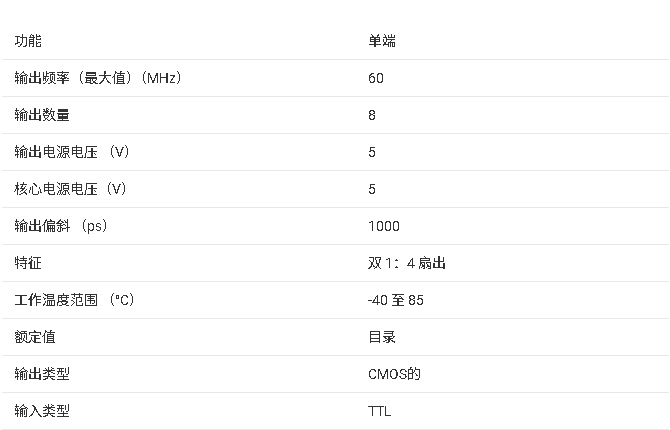

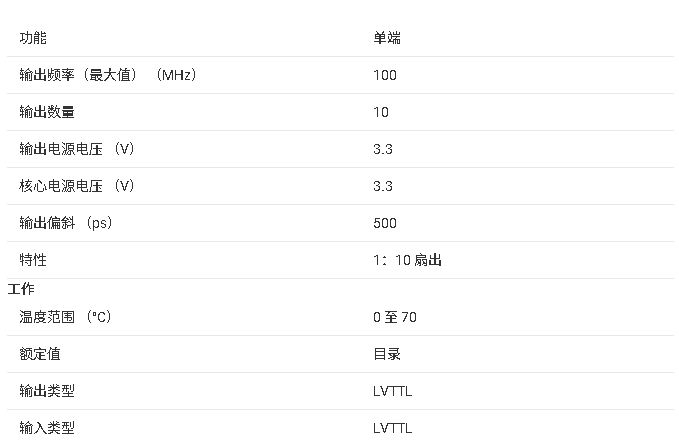

參數

?1. 產品概述?

CDC208是德州儀器(TI)設計的雙路1線轉4線時鐘驅動器,采用EPIC?(高性能植入CMOS)工藝,專為低偏移時鐘分配優化。核心功能包括:

- ?雙獨立驅動通道?:每路輸入(1A/2A)可驅動4路輸出(1Y1-1Y4/2Y1-2Y4),支持3態輸出控制(通過OE1/OE2使能)。

- ?低偏移設計?:輸出間最大偏移(tsk(o))僅 ?1ns?,適用于同步DRAM、微處理器等高速系統。

- ?工作溫度?:?**-40°C至85°C**?,工業級應用場景。

?2. 關鍵特性?

- ?電氣兼容性?:

- TTL兼容輸入,CMOS兼容輸出。

- 供電范圍 ?4.5V至5.5V?(典型5V),靜態功耗僅 ?8μA?。

- ?抗干擾設計?:

- 中心引腳VCC/GND布局減少高速開關噪聲。

- 典型鎖存免疫電流 ?500mA?(125°C)。

- ?封裝選項?:

- 20引腳SOIC(DW)或SOP(NS)封裝,符合RoHS標準。

?3. 功能邏輯?

?使能控制真值表?:

?OE1? ?OE2? ?A輸入? ?輸出狀態? L L L/H 反相輸出(低/高) H X X 高阻態(Z) X H X 固定高電平(H) ?引腳配置?:

- ?輸入?:1A(19腳)、2A(14腳)。

- ?使能端?:1OE1/1OE2(18/17腳)、2OE1/2OE2(13/12腳)。

- ?電源?:VCC(16/15腳)、GND(4-7腳)。

?4. 電氣參數?

| ?參數? | ?條件? | ?最小值? | ?最大值? | ?單位? |

|---|---|---|---|---|

| ?**高電平輸出(VOH)**? | IOH = -24mA, VCC=5V | 3.94 | 4.68 | V |

| ?**低電平輸出(VOL)**? | IOL = 24mA, VCC=5V | - | 0.44 | V |

| ?**傳播延遲(tPLH/tPHL)**? | CL=50pF, VCC=5V | 3.6 | 11.7 | ns |

| ?**輸出使能時間(tPZH)**? | - | 4.2 | 10.2 | ns |

?5. 應用注意事項?

- ?布局建議?:

- 使用短且等長的PCB走線以減少偏移。

- 避免輸入信號過渡時間超過 ?10ns/V?。

- ?絕對最大額定值?:

- 輸入電壓范圍:?**-0.5V至VCC+0.5V**?。

- 最大功耗:?1.6W?(55°C靜止空氣)。

?總結?:CDC208是一款高精度時鐘分配器件,適用于需嚴格同步的5V系統設計,其低偏移和靈活使能控制使其成為高速數字電路的理想選擇。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

電路

+關注

關注

173文章

6076瀏覽量

178390 -

輸入信號

+關注

關注

0文章

559瀏覽量

13179 -

時鐘驅動器

+關注

關注

0文章

122瀏覽量

14387 -

低邏輯電平

+關注

關注

0文章

2瀏覽量

1691

發布評論請先 登錄

相關推薦

熱點推薦

CDC319帶I2C控制接口的1線至10線時鐘驅動器數據表

電子發燒友網站提供《CDC319帶I2C控制接口的1線至10線時鐘驅動器數據表.pdf》資料免費

發表于 08-22 11:51

?0次下載

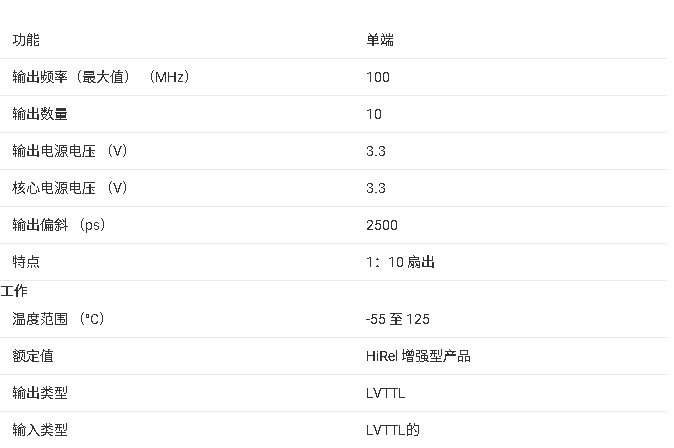

?CDC2351-EP 1線至10線時鐘驅動器技術文檔總結

CDC2351是一種高性能時鐘驅動器電路,可將一個輸入 (A) 分配到 10 個輸出 (Y),時鐘分配的偏斜最小。輸出使能 (OE)\ 輸入將輸出禁用到高阻抗狀態。每個輸出都有一個內部串聯阻尼電阻,以提高負載的信號完整性。該

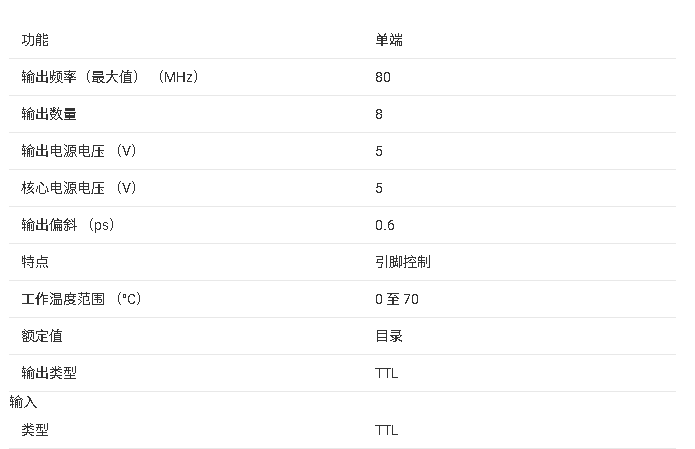

?CDC341 1線至8線時鐘驅動器技術文檔總結

CDC341 是一款高性能時鐘驅動器電路,可將一 (A) 輸入信號分配到八 (Y) 輸出,時鐘分配偏移最小。通過使用控制引腳(1G 和 2G),無論 A 輸入如何,輸出都可以置于低電平

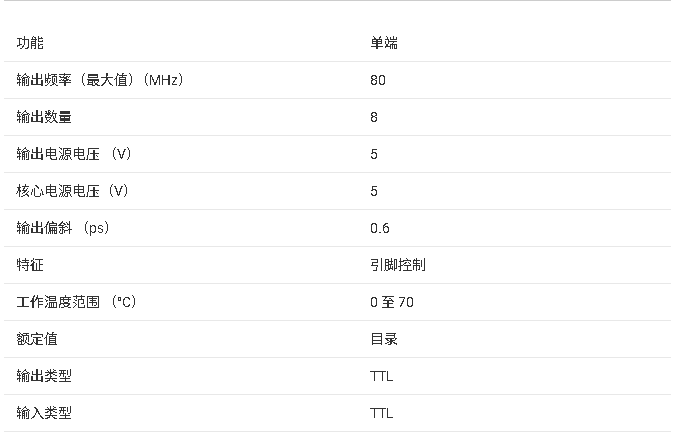

?CDC340 1線至8線時鐘驅動器技術文檔總結

CDC340 是一款高性能時鐘驅動器電路,可將一 (A) 輸入信號分配給八 (Y) 輸出,時鐘分配偏斜最小。通過使用控制引腳(1G 和 2G),無論 A 輸入如何,輸出都可以置于高電平

?CDC329A 時鐘驅動器技術文檔總結

該CDC329A包含一個時鐘驅動器電路,該電路將一個輸入信號分配到六個輸出,時鐘分配的偏斜最小。通過使用極性控制輸入(T\/C),可以獲得真輸出和互補輸出的各種組合。

該CDC3

?CDC2536 鎖相環時鐘驅動器技術文檔總結?

CDC2536是一款高性能、低偏斜、低抖動的時鐘驅動器。它使用鎖相環 (PLL) 將時鐘輸出信號在頻率和相位上精確對齊到時鐘輸入 (CLKIN) 信號。它專門設計用于同步 DRAM 和

?CDC2351 1線轉10線時鐘驅動器技術文檔總結

該CDC2351是一種高性能時鐘驅動器電路,可將一個輸入 (A) 分配到十個輸出 (Y),時鐘分配的偏斜最小。輸出使能 (OE\) 輸入將輸出禁用為高阻抗狀態。每個輸出都有一個內部串聯阻尼電阻,以提高負載的信號完整性。該

CDC328A:高性能時鐘驅動器的技術剖析

CDC328A:高性能時鐘驅動器的技術剖析 在電子設計領域,時鐘驅動器對于確保時鐘信號的精確分配和穩定傳輸至關重要。

CDC391時鐘驅動器:特性、參數與應用解析

391 1 - 線到 6 - 線時鐘驅動器,探討它的特性、參數以及應用場景。 文件下載: cdc391.pdf 一、

?CDC208 雙路1線至4線時鐘驅動器技術文檔總結

?CDC208 雙路1線至4線時鐘驅動器技術文檔總結

評論