AMD 器件上的典型時鐘電路結(jié)構(gòu)如下所示:

如果使用 MMCM 或 PLL 修改了時鐘,那么其結(jié)構(gòu)如下所示:

輸入端口 (IBUF) → BUFG → MMCM/PLL → BUFG → FDCE/C

對于 GT 時鐘,其結(jié)構(gòu)如下所示:

GT_QUAD → BUFG_GT → FDCE/C

在 I/O 時鐘布局器階段可能會發(fā)生錯誤,指出該工具無法對該時鐘結(jié)構(gòu)進(jìn)行布局,直至最后 BUFG 仍然無法完成布局。

發(fā)生這種問題的原因可能如下:

1. 時鐘結(jié)構(gòu)中的各單元上所選的 LOC 或 CLOCK_REGION。

2. 時鐘結(jié)構(gòu)紛繁復(fù)雜,若無手動約束則無法完成其布局。

3. 工具中存在 I/O 時鐘布局器算法漏洞。

該工具遇到這種情況時會打印詳細(xì)的錯誤消息,其中包括以下信息:

可解決此錯誤的 CLOCK_DEDICATED_ROUTE 約束

來自時鐘結(jié)構(gòu)的單元

由工具決定的時鐘緩沖器與 MMCM 的臨時布局

所有 I/O 時鐘架構(gòu)規(guī)則,以及臨時布局所違反的規(guī)則

雖然 CLOCK_DEDICATED_ROUTE 可以解決該錯誤,但在將其納入工作流程之前,用戶必須知曉以下內(nèi)容:

使用 CDR 對設(shè)計(jì) QoR 所帶來的影響

引發(fā)錯誤的原因是用戶約束、LOC、CLOCK_REGION 還是 P-BLOCK

時鐘結(jié)構(gòu)是否復(fù)雜,是否可以通過手動約束來解決

是否真的是 I/O 時鐘布局器算法的問題

本篇博客探討了如何理解 I/O 時鐘布局器錯誤、如何評估 CDR 約束必要性,以及如何判定該工具是否可以通過額外添加的約束來完成結(jié)構(gòu)布局。

在下列用戶指南中提供了 CLOCK_DEDICATED_ROUTE 的各種值:

AMD Versal 自適應(yīng) SoC《Versal 自適應(yīng) SoC 硬件、IP 和平臺開發(fā)方法指南》(UG1387):

https://docs.amd.com/access/sources/dita/topic?isLatest=true&url=ug1387-acap-hardware-ip-platform-dev-methodology&resourceid=uwc1571265539541.html&ft:locale=en-US

AMD UltraScale FPGA《適用于 FPGA 和 SoC 的 UltraFast 設(shè)計(jì)方法指南》(UG949):

https://docs.amd.com/access/sources/dita/topic?isLatest=true&url=ug949-vivado-design-methodology&resourceid=using-clock_dedicated_route-constraint-aa661636.html&ft:locale=en-US

對于復(fù)雜的時鐘結(jié)構(gòu),可以通過混用多個單元和信號線的 CDR、LOC 與 CLOCK_REGION 約束來解決 I/O 時鐘布局器錯誤。

在進(jìn)行深入調(diào)試之前,應(yīng)該熟悉以下前提條件:

1. 使用的器件的 I/O 架構(gòu):

對于 UltraScale,請參閱《UltraScale 架構(gòu) SelectIO 資源用戶指南》(UG571)

https://docs.amd.com/go/en-US/ug571-ultrascale-selectio

對于 Versal,請參閱《Versal 自適應(yīng) SoC SelectIO 資源架構(gòu)手冊》(AM010)

https://docs.amd.com/go/en-US/am010-versal-selectio

2. 使用的器件的時鐘架構(gòu):

對于 UltraScale,請參閱《UltraScale 架構(gòu)時鐘資源用戶指南》(UG572):

https://docs.amd.com/go/en-US/ug572-ultrascale-clocking

對于 Versal,請參閱《Versal 自適應(yīng) SoC 時鐘資源架構(gòu)手冊》(AM003):

https://docs.amd.com/go/en-US/am003-versal-clocking-resources

3. 使用“Find”(查找)窗口即可列出器件中可用的各 site 位置(BUFG 和 MMCM/PLL)。

4. 在網(wǎng)表中使用“Find”窗口即可列出錯誤中提及的單元和信號線。

5. AMD Vivado Design Suite 的基本 Tcl 腳本編制。

調(diào)試

I/O 時鐘布局器算法是一種基于規(guī)則的算法,可將網(wǎng)表中的時鐘結(jié)構(gòu)映射到具體規(guī)則。這些規(guī)則用于為設(shè)計(jì)中的 MMCM/PLL 和 BUFG 分配臨時布局。但請務(wù)必注意,這些臨時布局對某些單元可能是正確的,但對其他單元則不正確。以下提供的規(guī)則可用于理解與評估該算法所做的布局:

Versal:《Versal 自適應(yīng) SoC 硬件、IP 和平臺開發(fā)方法指南》(UG1387):

https://docs.amd.com/access/sources/dita/topic?isLatest=true&url=ug1387-acap-hardware-ip-platform-dev-methodology&resourceid=zuj1571259717978.html&ft:locale=en-US

UltraScale:《適用于 FPGA 和 SoC 的 UltraFast 設(shè)計(jì)方法指南》(UG949) :

https://docs.amd.com/access/sources/dita/topic?isLatest=true&url=ug949-vivado-design-methodology&resourceid=clock-tree-placement-and-routing-aa661458.html&ft:locale=en-US

由于這些規(guī)則均衍生自實(shí)際硅片,因此 I/O 時鐘布局器錯誤不太可能源自于工具中的真實(shí)漏洞。但本篇博客涵蓋了這種可能性,以防萬一。

遇到這些問題時,建議使用 .runs/impl_1 文件夾中找到的優(yōu)化后檢查點(diǎn)來開展工作。如果您是非工程模式用戶,則需要顯式在 opt_design 之后生成 dcp 文件。

1. open_checkpoint post_opt.dcp。

2. 使用 place_ports 命令代替 place_design。

當(dāng) place_design 運(yùn)行失敗時,并不會在存內(nèi)設(shè)計(jì)中留下可用的部分布局以供檢驗(yàn)。可以改為運(yùn)行 place_ports 命令,以便復(fù)現(xiàn)同樣的錯誤,同時提供產(chǎn)生的部分布局以供檢驗(yàn)。

3. 顯示提及的單元和信號線的原理圖。

您可以使用 Vivado 中的 Ctrl+F 選項(xiàng)返回錯誤中提及的單元,或者使用 Tcl 腳本將錯誤消息中的單元和信號線放入 Tcl 變量中。

4. 顯示時鐘區(qū)域中 BUFG 與 MMCM site 位置的對象,以檢查特定時鐘區(qū)域的使用率。

5. 對時鐘結(jié)構(gòu)進(jìn)行分段。

例如,如果時鐘結(jié)構(gòu)如下:

(IBUF) → BUFG → MMCM/PLL → BUFG → FDCE/C

第 1 段 = IBUF → BUFG

第 2 段 = BUFG → MMCM/PLL

第 3 段 = MMCM/PLL → BUFG

6. 將 Vivado 的臨時布局與文檔中提到的規(guī)則進(jìn)行交叉比對。

例如,如果這是個 Versal 器件,那么第 1 段顯然是被布局在同一個時鐘區(qū)域內(nèi)的,即第一行。

第 2 段屬于規(guī)則中提到的最后一行。為了解決這個問題,如果您將 LOC 放在 MMCM 上,那么第 3 段就歸屬于規(guī)則的第 2 行。

檢查提及的單元上是否有任何用戶約束,如果有,那么請檢查這些約束是否對任何規(guī)則產(chǎn)生影響。

如果進(jìn)行迭代分析:您需要驗(yàn)證布局是否遵守上述規(guī)則。如不遵守這些規(guī)則,請檢查其他單元是否影響該布局。

注釋:以上鏈接中提到了這些規(guī)則。

7. 判定一個約束,用于強(qiáng)制 Vivado 遵循這些規(guī)則。

8. 使用新約束重新運(yùn)行優(yōu)化后的步驟。

9. 重復(fù)上述步驟,以識別錯誤中是否會報告任何新單元。通過迭代方式執(zhí)行這些步驟,即可獲得一組約束,用于繼續(xù)執(zhí)行設(shè)計(jì)實(shí)現(xiàn)。

注釋:在某些情況下,CDR = false 是不可避免的,例如,為輸入時鐘使用非 CCIO 管腳時就是如此。在此情況下,必須在 IBUF 的輸出上設(shè)置 CDR = False 約束。

以下提供了在 Versal 架構(gòu)和 UltraScale 架構(gòu)中調(diào)試這些問題的一些示例。

1. CLOCK_DEDICATED_ROUTE 異常示例:

https://adaptivesupport.amd.com/s/article/Vivado-Implementation-Resolving-IO-Clock-Placer?language=zh_CN

2. UltraScale 示例:

https://adaptivesupport.amd.com/s/article/Vivado-Implementation-Resolving-IO-Clock-Placer-Errors-Example-Ultrascale?language=zh_CN

3. Versal 示例:

https://adaptivesupport.amd.com/s/article/Vivado-Implementation-Resolving-IO-Clock-Placer-Errors-Example-Versal?language=zh_CN

-

amd

+關(guān)注

關(guān)注

25文章

5695瀏覽量

140213 -

時鐘

+關(guān)注

關(guān)注

11文章

1993瀏覽量

135128 -

Vivado

+關(guān)注

關(guān)注

19文章

859瀏覽量

71270

原文標(biāo)題:開發(fā)者分享|AMD Vivado? Design Suite 實(shí)現(xiàn) - 解決 I/O 時鐘布局器錯誤

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發(fā)者社區(qū)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

SGM4593:低電壓16位I2C和SMBus低功耗I/O擴(kuò)展器的深度解析

SGM4594:低電壓16位I2C和SMBus低功耗I/O擴(kuò)展器的全面解析

SGM4591:低電壓16位I2C和SMBus低功耗I/O擴(kuò)展器的深度解析

SCH5127 Super I/O 控制器:功能特性與設(shè)計(jì)應(yīng)用解析

PCA9554:8位I2C和SMBus I/O擴(kuò)展器的深度解析

TCA6408A:低電壓8位I2C和SMBus I/O擴(kuò)展器的深度解析

TCA9555:低電壓16位I2C和SMBus I/O擴(kuò)展器的全面解析

TCA6424A:低電壓24位I2C和SMBus I/O擴(kuò)展器的深度解析

深入解析TCA9554:8位I2C和SMBus低功耗I/O擴(kuò)展器

淺談光學(xué)I/O模塊的熱挑戰(zhàn)

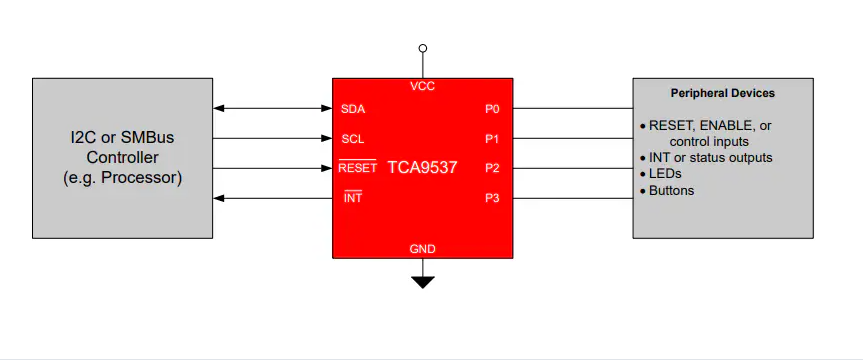

TCA9537遠(yuǎn)程4位I2C/SMBus I/O擴(kuò)展器技術(shù)解析與應(yīng)用指南

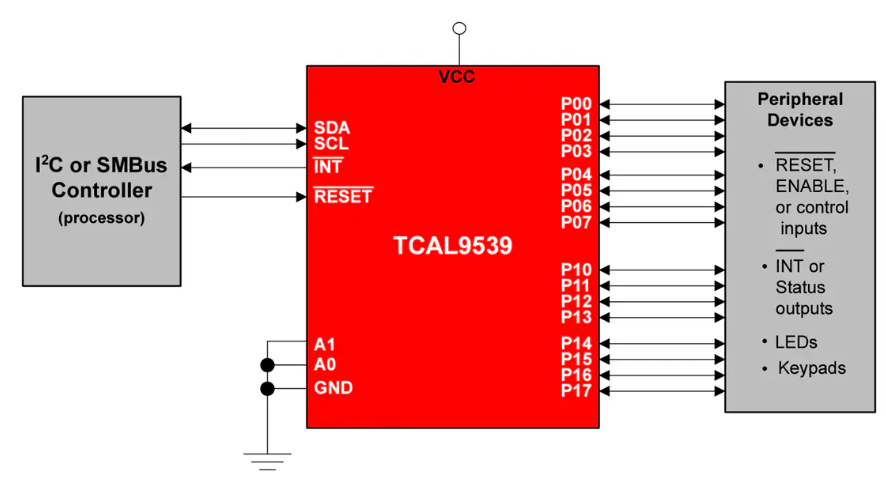

TCAL9539 I2C總線I/O擴(kuò)展器技術(shù)解析與應(yīng)用指南

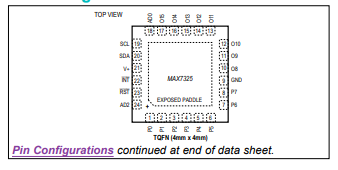

MAX7325 I2C端口擴(kuò)展器,提供8路推挽式I/O和8個漏極開路I/O技術(shù)手冊

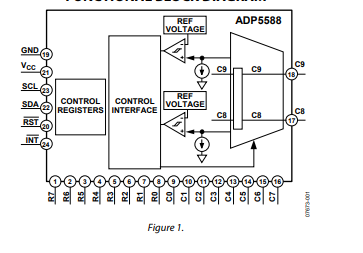

ADP5588移動I/O擴(kuò)展器和QWERTY鍵盤控制器技術(shù)手冊

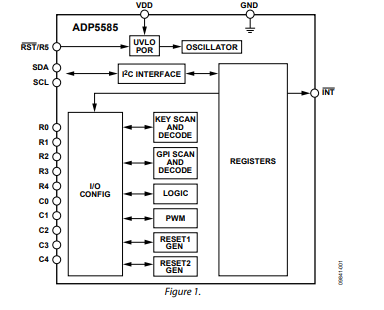

ADP5585鍵盤解碼器和I/O擴(kuò)展器技術(shù)手冊

如何解決I/O時鐘布局器錯誤

如何解決I/O時鐘布局器錯誤

評論