該DP8573A旨在用于基于微處理器的系統,其中需要信息來進行多任務處理、數據記錄或一般時間/日期信息。該器件采用低壓硅柵 microCMOS 技術實現,可在備用電池環境中提供低待機功耗。該電路的架構看起來像一個連續的內存塊或 I/O 端口,組織為一個 32 字節的塊。這包括控制寄存器、時鐘計數器、報警比較 RAM 和省時 RAM。

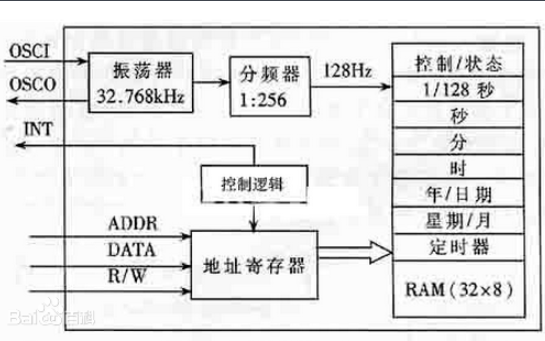

時間和日期以 BCD 格式、12 或 24 小時模式從 1/100 秒到年和閏年保持。提供星期幾和月份中的某一天計數器。時間由片內晶體振蕩器控制,只需添加32.768 kHz晶體和兩個電容器。

*附件:dp8573a.pdf

斷電邏輯和控制功能已集成在片上。RTC使用此邏輯發出電源故障中斷,并鎖定μP接口。當 V 時,電源故障時間可能會自動登錄到 RAM 中 BB型 > V CC .此外,還提供了兩個電源引腳。當 V BB型 > V CC ,內部電路會自動從主電源切換到電池電源。

DP8573A的中斷結構提供三種基本類型的中斷:定期中斷、警報/比較中斷和電源故障。中斷掩模和狀態寄存器支持掩蔽并輕松確定每個中斷。

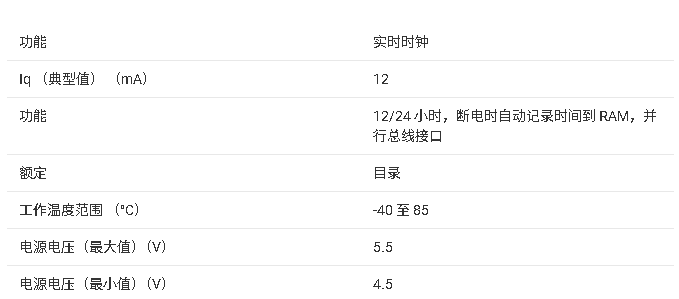

特性

參數

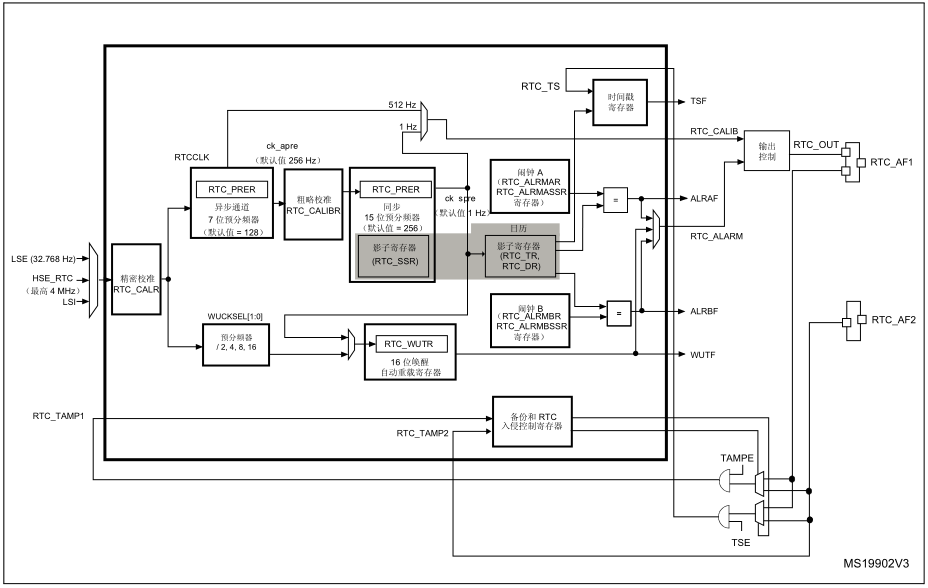

?一、核心功能概述?

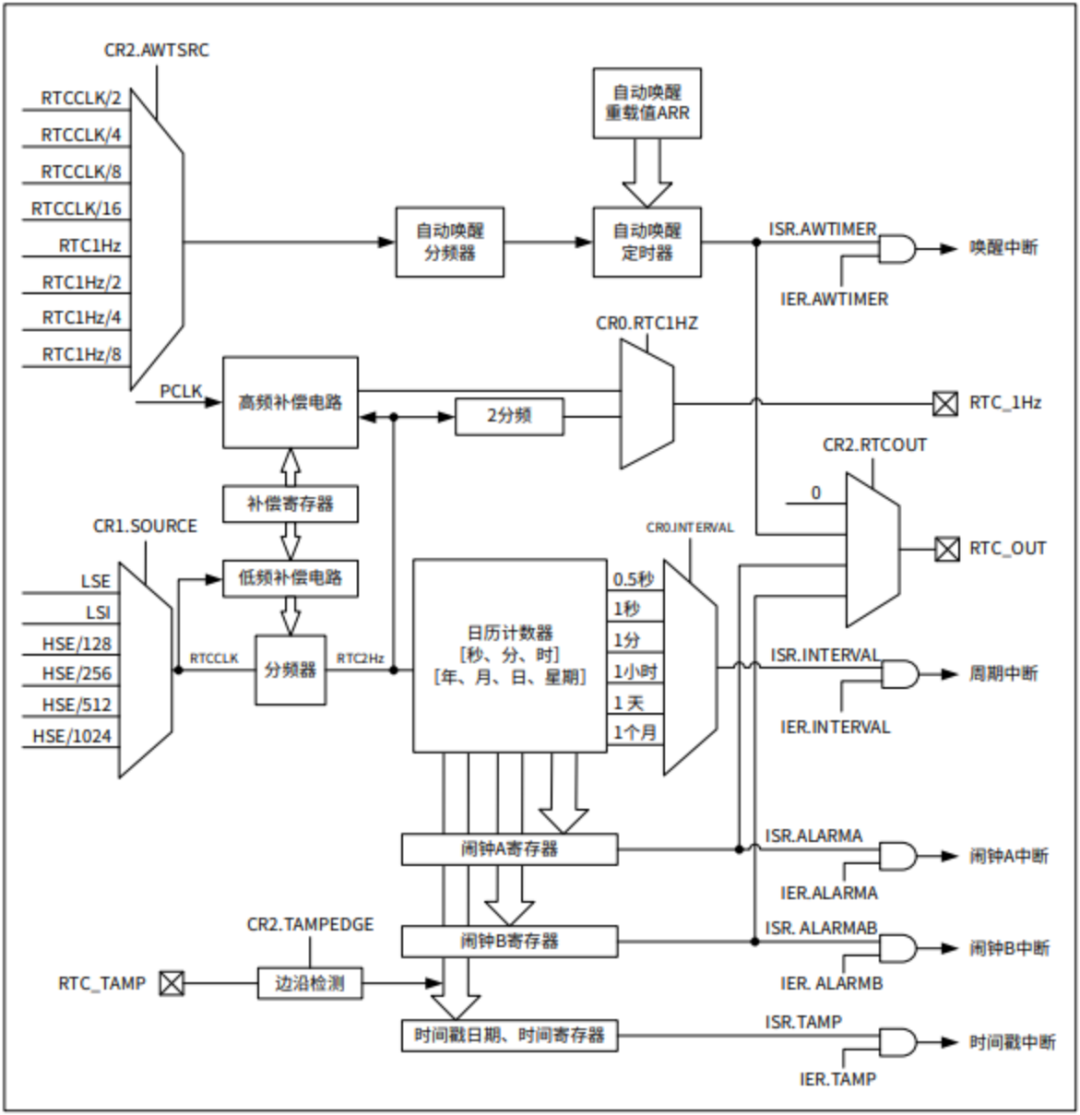

DP8573A是一款專為微處理器系統設計的實時時鐘芯片,采用低電壓硅柵微CMOS技術,具備以下核心特性:

- ?時間管理?:支持1/100秒至年的BCD格式計時,提供12/24小時模式、星期/日期計數器,內置32.768kHz晶體振蕩器(僅需外接晶體和電容)。

- ?電源冗余?:集成VCC/VBB雙電源切換邏輯,主電源失效時自動切換至備份電池(2.2V≤VBB≤VCC-0.4V),支持電源失效中斷及時間日志記錄。

- ?中斷系統?:支持周期性、鬧鐘比較、電源失效三類中斷,可通過掩碼寄存器靈活配置。

?二、關鍵模塊詳解?

- ?時鐘與日歷?

- 8字節BCD計數器鏈,覆蓋1/100秒、秒、分、時、日、月、年及星期。

- 支持閏年計算(可編程4年周期)和12/24小時模式切換。

- 提供“驗證讀取”機制防止計數器滾動時讀取錯誤。

- ?中斷控制?

- ?周期性中斷?:基于計數器溢出觸發(如每分鐘/秒),狀態標志需手動清除。

- ?鬧鐘中斷?:6組比較寄存器可編程未來觸發時間,支持多條件組合(如每日3:15 AM)。

- ?電源失效中斷?:通過PFAIL引腳檢測,30-63ms去抖后觸發,強制鎖定接口。

- ?電源管理?

- 自動切換至VBB供電,主電源恢復后需PFAIL引腳置高解鎖。

- 單電源模式(VBB接地)需禁用振蕩器參考電路以降低功耗。

- ?時間保存功能?

- 通過Time Save RAM實現時鐘快照,避免讀取時計數器滾動沖突。

- 電源失效時可自動保存當前時間至RAM。

?三、寄存器架構?

- ? 主狀態寄存器(00H) ?:全局中斷狀態、寄存器塊選擇(D6位)。

- ?控制寄存器組?:包括實時模式(12/24小時設置)、中斷使能、輸出模式配置等。

- ?計數器與RAM?:32字節地址空間,含時鐘值、比較RAM及通用存儲區。

?四、電氣特性?

- 工作電壓:4.5V~5.5V(VCC),備份模式下VBB≥2.2V。

- 功耗:典型待機電流10μA(電池模式),工作電流250μA(5V供電)。

- 溫度范圍:-40℃~+85℃。

?五、應用設計要點?

- ?初始化?:上電后需配置振蕩器、時鐘模式及中斷參數,清除隨機數據。

- ?抗干擾?:電源失效檢測需硬件去抖,VCC/VBB電壓差需保持以避免切換沖突。

- ?PCB布局?:晶體負載電容(典型11pF)需匹配廠商要求,寄生電容影響需補償。

?六、封裝與引腳?

- 提供DIP-24和PLCC-28封裝,關鍵引腳包括:

- ?OSC IN/OUT?:外接晶體。

- ?PFAIL?:電源失效檢測輸入。

- ?INTR/MFO?:開漏中斷輸出(支持雙中斷配置)。

-

寄存器

+關注

關注

31文章

5615瀏覽量

130318 -

實時時鐘

+關注

關注

4文章

362瀏覽量

68468 -

內存

+關注

關注

9文章

3223瀏覽量

76468 -

微處理器

+關注

關注

11文章

2438瀏覽量

86084 -

計數器

+關注

關注

32文章

2320瀏覽量

98452

發布評論請先 登錄

RTC是什么?RTC實時時鐘實驗

DP8573A日歷時鐘芯片的應用

淺談RTC實時時鐘特征與原理

stm32f4 RTC實時時鐘解析

?DP8573A實時時鐘(RTC)芯片技術文檔總結

?DP8573A實時時鐘(RTC)芯片技術文檔總結

評論