CDC319 是一款高性能時鐘緩沖器,可將一個輸入 (A) 分配到 10 個輸出 (Y),最小 時鐘分布的傾斜。CDC319采用3.3 V電源供電,其工作特性 從 0°C 到 70°C。

該器件提供標準模式(100K-bits/s)I^2^用于設備控制的 C 串行接口。執(zhí)行 是作為從屬/接收器。設備地址在 I^2^C 設備地址表。兩個我^2^C 輸入 (SDATA和SCLOCK)提供集成上拉電阻(典型值為140 k),并且具有5 V容差。

*附件:cdc319.pdf

三個 8 位 I^2^C 寄存器為每個輸出提供單獨的使能控制。所有輸出默認為啟用 在通電時。當低電平控制位時,每個輸出都可以置于低電平輸出的禁用模式 寫入控制寄存器。寄存器是僅寫的,必須按順序訪問(即 不支持寄存器的隨機訪問)。

CDC319 提供 3 態(tài)輸出,用于測試和調試目的。輸出可以放置在 通過輸出使能 (OE) 輸入實現高阻抗狀態(tài)。當OE為高電平時,所有輸出都處于工作狀態(tài)。 當OE為低電平時,輸出處于高阻抗狀態(tài)。OE 提供集成上拉電阻器。

特性

- 用于SDRAM(同步DRAM)時鐘緩沖應用的高速、低偏斜1-10時鐘緩沖器

- 輸出傾斜,t

SK(O),小于 250 ps - 脈沖偏斜,t

SK(p),小于 500 ps - 支持多達兩個無緩沖 SDRAM DIMM(雙列直插式內存模塊)

- 我^2^C 串行接口為每個輸出提供單獨的使能控制

- 工作電壓為 3.3 V

- 分布式V

CC接地引腳可降低開關噪聲 - ESD 保護超過 2000 V,符合 MIL-STD-883,方法 3015

- 采用 28 引腳熱縮小外形 (DB) 封裝

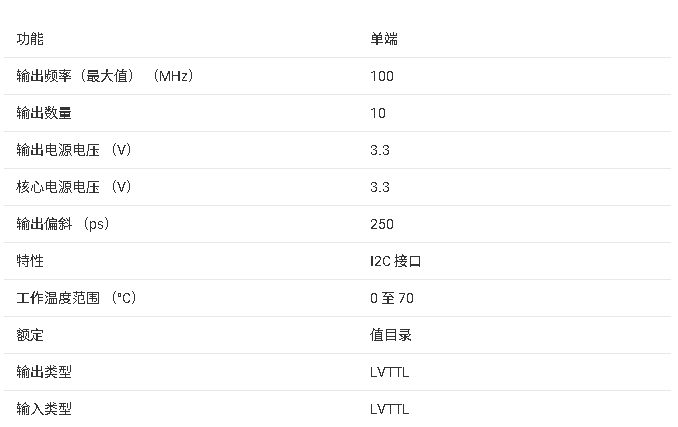

參數

?1. 產品概述?

CDC319是德州儀器(TI)設計的高性能時鐘緩沖器,專為SDRAM時鐘分配應用優(yōu)化。核心功能包括:

- ?1輸入轉10輸出?:單時鐘輸入(A)分配至10路低偏移輸出(Y0-Y9)

- ?關鍵性能指標?:輸出偏移(tsk(o))<250ps,脈沖偏移(tsk(p))<500ps

- ?工作電壓?:3.3V,溫度范圍0°C至70°C

?2. 核心特性?

- ?I2C控制接口?:

- 支持標準模式(100kbps)串行通信

- 3個8位寄存器獨立控制每路輸出使能(默認上電全啟用)

- 地址固定為0b1101000X(X為R/W位)

- ?輸出管理?:

- 輸出使能(OE)引腳可全局置高阻態(tài)(集成140kΩ上拉電阻)

- 通過I2C可單獨禁用輸出(強制拉低)

?3. 封裝與引腳?

- ? 28引腳SSOP封裝(DB) ?

- 分布式VCC/GND引腳設計降低開關噪聲

- 輸出分組:

- 1Y0-1Y3:SDRAM字節(jié)0時鐘

- 2Y0-2Y3:SDRAM字節(jié)1時鐘

- 3Y0-3Y1:外部PLL反饋時鐘

?4. 電氣特性?

- ?最大時鐘頻率?:

- 140MHz(CL=15pF @70°C)

- 125MHz(CL=20pF @70°C)

- ?ESD防護?:超過2000V(MIL-STD-883方法3015)

- ?功耗?:典型值0.5mA(靜態(tài))

?5. 應用設計要點?

- ?時序控制?:

- 傳播延遲1.2-3.6ns(輸入到輸出)

- 啟用/禁用時間4.7ns(OE控制)

- ?布局建議?:

- 每路輸出負載電容≤30pF以保證高頻穩(wěn)定性

- 需考慮傳輸線匹配(典型阻抗50Ω)

?6. 生產與認證?

- 符合TI標準質保條款

- 封裝選項包括管裝(50片/管)和卷帶(2000片/卷)

- RoHS兼容(無鉛工藝)

該器件適用于需要精確時鐘分配的高可靠性系統(tǒng),如服務器內存模塊、通信設備時鐘樹等關鍵應用場景。

-

接收器

+關注

關注

15文章

2644瀏覽量

77118 -

時鐘緩沖器

+關注

關注

2文章

270瀏覽量

51910 -

串行接口

+關注

關注

3文章

520瀏覽量

45216 -

電源供電

+關注

關注

0文章

216瀏覽量

22893

發(fā)布評論請先 登錄

什么是時鐘緩沖器(Buffer)?時鐘緩沖器(Buffer)參數解析

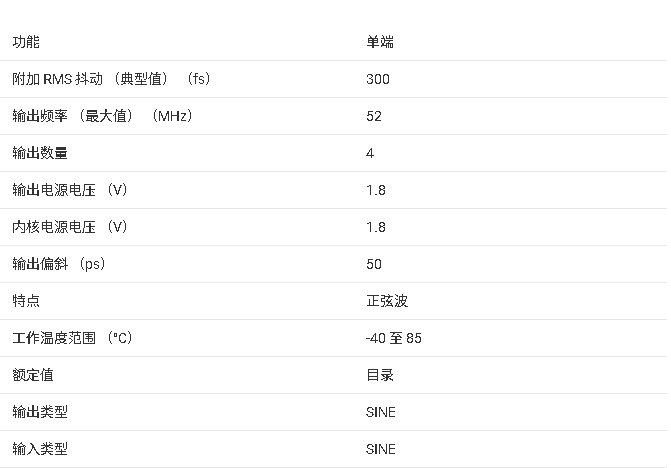

CDC3RL02低相位噪聲雙通道時鐘扇出緩沖器數據表

CDC319帶I2C控制接口的1線至10線時鐘驅動器數據表

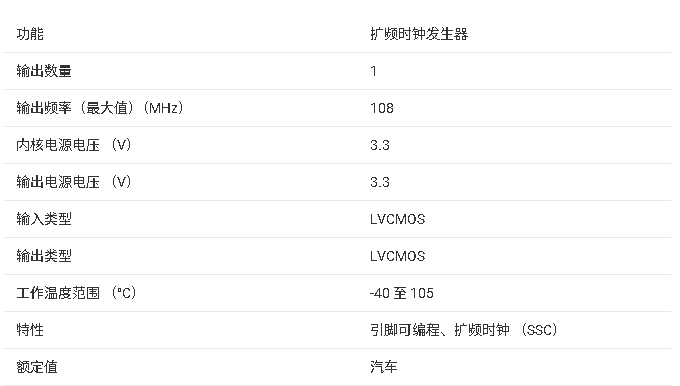

?CDCS503-Q1 時鐘緩沖器/時鐘倍頻器技術文檔總結

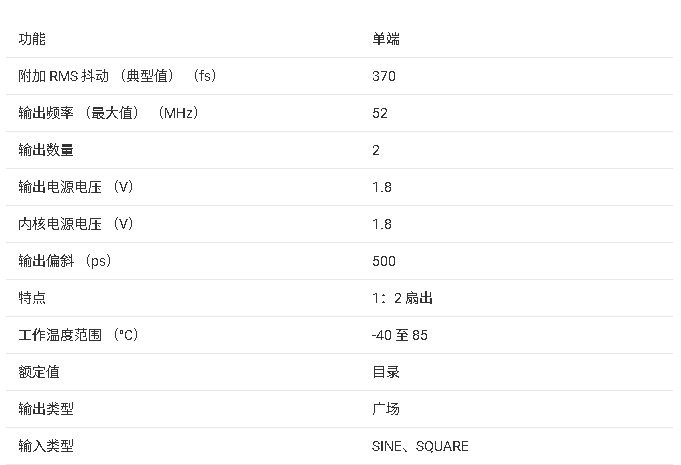

?LMH2180 75 MHz雙時鐘緩沖器技術文檔總結

?CDC319 1-to-10時鐘緩沖器技術文檔總結

?CDC319 1-to-10時鐘緩沖器技術文檔總結

評論