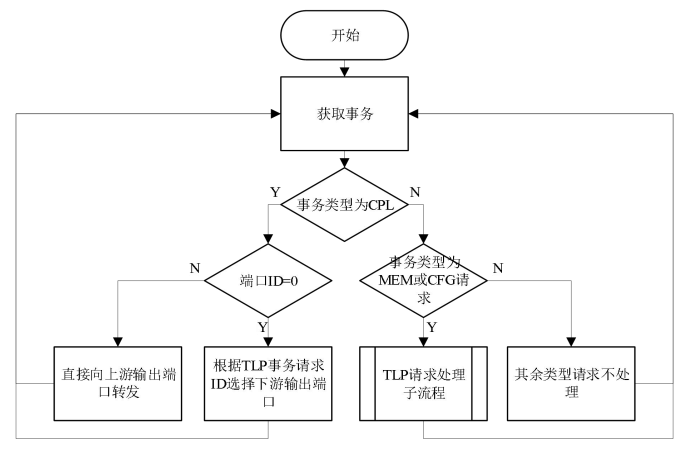

前面提到最小橋設備模型的每個端口的輸入端對接一個 TLP事務處理程序, 該程序負責將接收到的 TLP 事務進行解析和路由轉發。 TLP 事務處理程序的執行流程如圖 1 所示。

圖1 TLP 事務處理程序的執行流程圖

當對應任務接口的事務緩存中存在未處理事務時, 處理程序從緩存中獲取事務。首先檢查事務類型, 當事務類型為 Cpl 響應類型事務時, 如果當前程序對應接收端口號為 0, 即接收端口為唯一的上游端口時, 該響應類型事務需要根據事務中的請求 ID字段與配置空間封裝類中的相關字段進行比較, 實現基于 ID 的路由; 如果對應接收端口號不為 0, 表示該響應類型事務來自下游端口, 此時直接將該事務轉發到上游輸出端口。 當事務類型為 MEM 讀寫請求或 CFG 配置讀寫請求時, 進入 TLP 請求處理子程序, 對于其它類型的請求暫不支持。

B站已給出相關性能的視頻,如想進一步了解,請搜索B站用戶:專注與守望

鏈接:https://space.bilibili.com/585132944/dynamic?spm_id_from=333.1365.list.card_title.click

審核編輯 黃宇

-

TLP

+關注

關注

0文章

37瀏覽量

16392 -

高速傳輸

+關注

關注

0文章

39瀏覽量

9270 -

nvme

+關注

關注

0文章

289瀏覽量

23741

發布評論請先 登錄

NVMe高速傳輸之擺脫XDMA設計30: NVMe 設備模型設計

NVMe高速傳輸之擺脫XDMA設計28: TLP 事務處 理程序的執行流程

NVMe高速傳輸之擺脫XDMA設計27: 橋設備模型設計

NVMe高速傳輸之擺脫XDMA設計26: 驅動器設計

NVMe高速傳輸之擺脫XDMA設計24: UVM 驗證包設計

NVMe高速傳輸之擺脫XDMA設計22:PCIe的TLP讀優化處理

NVMe高速傳輸之擺脫XDMA設計21:PCIe的TLP讀處理

NVMe高速傳輸之擺脫XDMA設計20: PCIe應答模塊設計

NVMe高速傳輸之擺脫XDMA設計20: PCIe應答模塊設計

NVMe高速傳輸之擺脫XDMA設計17:PCIe加速模塊設計

NVMe高速傳輸之擺脫XDMA設計16:TLP優化

NVMe高速傳輸之擺脫XDMA設計15:PCIe的TLP讀處理

NVMe高速傳輸之擺脫XDMA設計14: PCIe應答模塊設計

NVMe高速傳輸之擺脫XDMA設計28: TLP 事務處理程序的執行流程

NVMe高速傳輸之擺脫XDMA設計28: TLP 事務處理程序的執行流程

評論