LMK01000系列提供了一種在整個系統中劃分和分配高性能時鐘信號的簡單方法。這些器件提供一流的噪聲性能,并設計為引腳對引腳和封裝與 LMK03000/LMK02000 系列精密時鐘調理器兼容。

*附件:lmk01020.pdf

LMK01000 系列具有兩個可編程時鐘輸入(CLKin0 和 CLKin1),允許用戶在不同的時鐘域之間動態切換。

每個器件具有 8 個時鐘輸出,具有獨立可編程的分頻器和延遲調整。器件的輸出可以通過外部引腳 (SYNC*) 輕松同步。

特性

- 30 fs 附加抖動(100 Hz 至 20 MHz)

- 雙時鐘輸入

- 可編程輸出通道(0 至 1600 MHz)

- 外部同步

- 引腳兼容系列時鐘設備

- 3.15 至 3.45 V 工作電壓

- 封裝:48 引腳 LLP (7.0 x 7.0 x 0.8 mm)

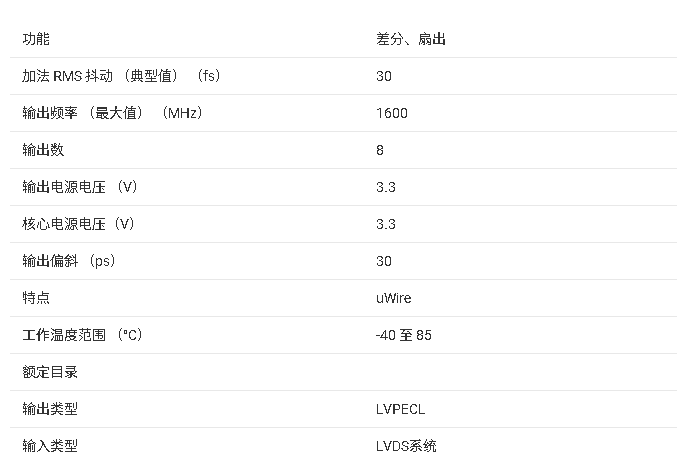

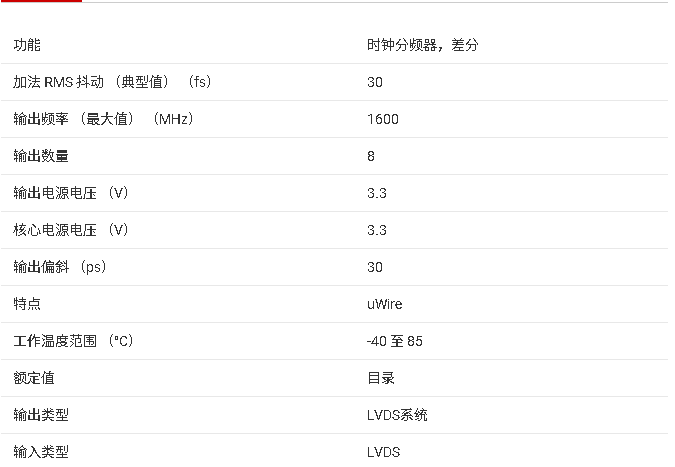

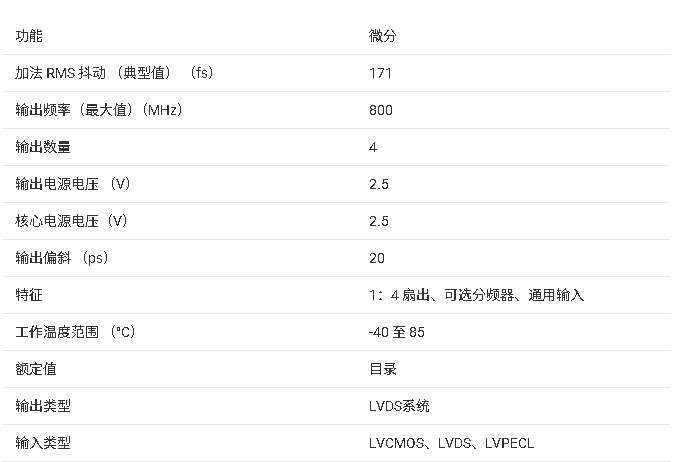

參數

方框圖

?1. 產品概述?

LMK01000系列是德州儀器(TI)推出的高性能時鐘管理芯片家族,包含LMK01000、LMK01010和LMK01020三款型號,專為1.6 GHz以下時鐘信號的分配、分頻和同步設計。核心特性包括:

- ?超低抖動?:30 fs(100 Hz至20 MHz頻段)

- ?雙時鐘輸入?:支持CLKin0和CLKin1動態切換

- ?8路可編程輸出?:每路獨立配置分頻比(1

510偶數分頻)、延遲調整(02250 ps,步進150 ps)及輸出格式(LVDS/LVPECL) - ?同步功能?:通過SYNC*引腳實現多路輸出相位對齊

- ?寬電壓范圍?:3.15~3.45 V工作電壓,48引腳LLP封裝(7×7×0.8 mm)

?2. 關鍵應用領域?

?3. 功能模塊詳解?

- ?時鐘輸入?:支持差分/單端AC耦合輸入,頻率范圍0.5~1600 MHz

- ?輸出通道?:

- ?LMK01000?:3路LVDS + 5路LVPECL

- ?LMK01010?:8路LVDS

- ?LMK01020?:8路LVPECL

- ?延遲與分頻?:每通道可選旁路、分頻、延遲或混合模式,固定路徑延遲100~500 ps

- ?控制接口?:通過MICROWIRE協議(CLKuWire/DATAuWire/LEuWire)配置寄存器

?4. 電氣特性?

- ?功耗?:典型值271 mA(LMK01000全輸出使能)

- ?抖動性能?:

- LVDS輸出:30 fs(800 MHz)

- LVPECL輸出:25 fs(800 MHz)

- ?噪聲基底?:<-148 dBc/Hz(1600 MHz)

?5. 設計注意事項?

- ?熱管理?:需通過裸露焊盤(DAP)連接PCB地平面,θJA=27.4°C/W

- ?布局建議?:

- 使用16個熱過孔優化散熱

- LVDS/LVPECL輸出需匹配100Ω差分阻抗

- 避免未使用的輸出引腳懸空

- ?電源去耦?:每個Vcc引腳需配置10 nF+470 nF電容

?6. 寄存器配置?

- ?關鍵寄存器?:R0~R7控制各通道功能,R14管理全局使能/功耗

- ?編程流程?:

- R0寫入復位(RESET=1)

- 配置各通道分頻/延遲/使能

- R14設置全局參數

?7. 典型應用電路?

- 與LMX2531 PLL配合實現時鐘樹分配

- 多片級聯擴展輸出通道(需注意同步時序)

?8. 封裝與訂購信息?

- 48引腳WQFN(RHS)封裝,支持-40°C至85°C工業溫度范圍

- 可選卷帶包裝(1000/250/2500片)

該系列以高集成度和低抖動特性,適用于對時鐘精度要求嚴苛的射頻與數字系統設計。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

時鐘緩沖器

+關注

關注

2文章

273瀏覽量

51952 -

分頻器

+關注

關注

43文章

537瀏覽量

53667 -

引腳

+關注

關注

16文章

2116瀏覽量

55956 -

時鐘信號

+關注

關注

4文章

508瀏覽量

30062

發布評論請先 登錄

相關推薦

熱點推薦

AD9512:1.2 GHz時鐘分配IC,1.6 GHz輸入,分頻器,延遲調整,五輸出數據表

AD9512:1.2 GHz時鐘分配IC,1.6 GHz輸入,分頻器,延遲調整,五輸出數據表

發表于 03-22 19:53

?13次下載

LMK01010 1.6 GHz 高性能時鐘緩沖器、分頻器和分配器技術手冊

LMK01000系列提供了一種在整個系統中劃分和分配高性能時鐘信號的簡單方法。這些器件提供一流的噪聲性能,并設計為引腳對引腳和封裝與

LMK1D1208I:高性能LVDS時鐘緩沖器的深度剖析與應用指南

LMK1D1208I:高性能LVDS時鐘緩沖器的深度剖析與應用指南 在電子設計的世界里,時鐘緩沖器

LMK1D120x低附加抖動LVDS緩沖器:高性能時鐘分配的理想選擇

LMK1D120x低附加抖動LVDS緩沖器:高性能時鐘分配的理想選擇 在電子設計領域,時鐘信號的

解析CDCL1810:高性能時鐘分配器的技術剖析與應用指南

電子系統設計中的理想選擇。下面將詳細解析CDCL1810的各項特性、應用場景及設計要點。 文件下載: cdcl1810.pdf 產品概述 CDCL1810是一款高性能的時鐘分配器,采用單1.8V電源供電,具備10個輸出通道,支持

LMK01020 1.6 GHz 高性能時鐘緩沖器、分頻器和分配器技術手冊

LMK01020 1.6 GHz 高性能時鐘緩沖器、分頻器和分配器技術手冊

評論