南京屹立芯創(chuàng)半導(dǎo)體科技有限公司

“堆”出萬億算力:先進(jìn)封裝如何驅(qū)動AI算力爆發(fā)

一塊小小的芯片,如何實現(xiàn)百倍增長的計算能力?答案不在縮小的晶體管,而在顛覆性的封裝技術(shù)。

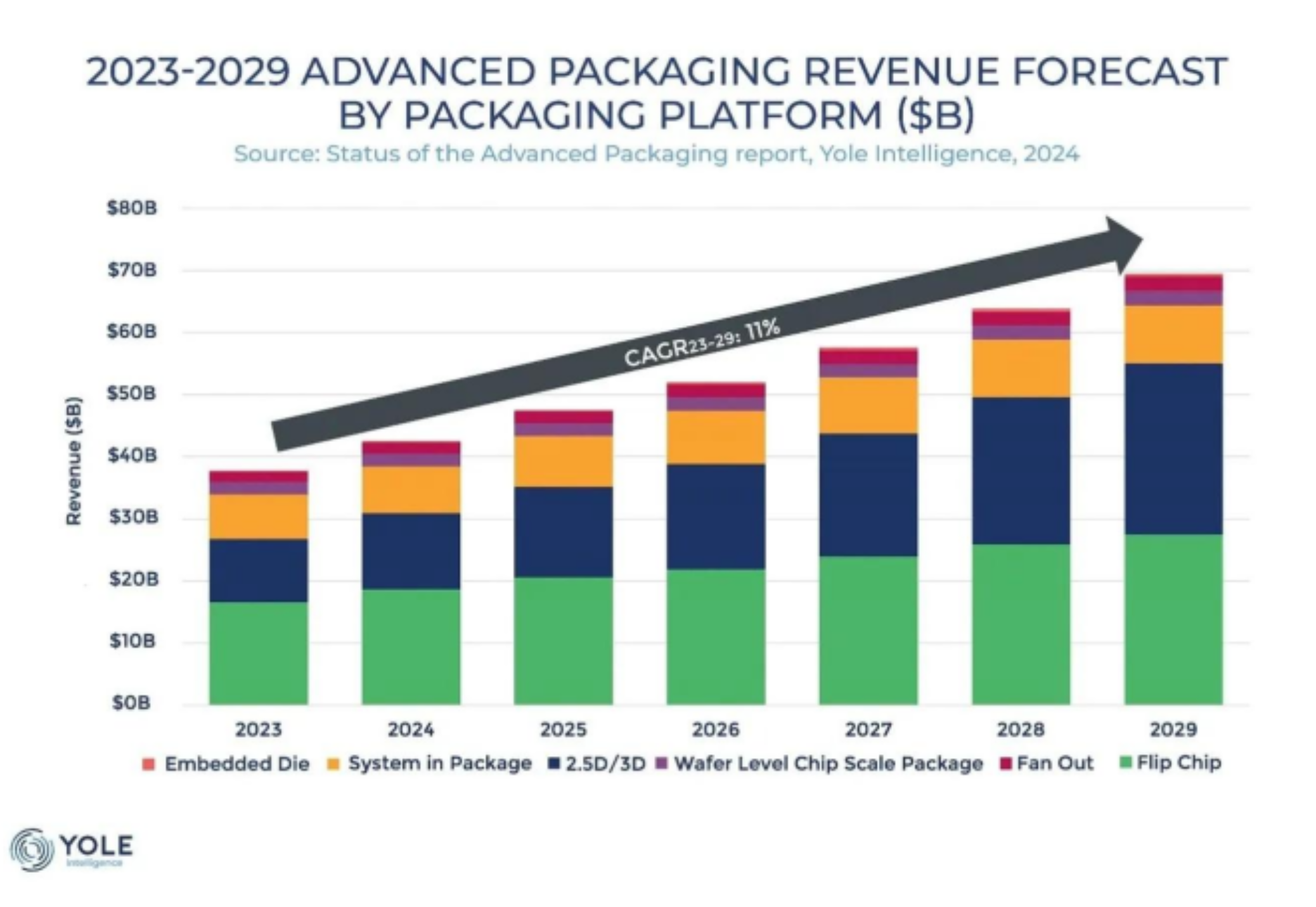

當(dāng) Yole Group 在《2025 先進(jìn)封裝產(chǎn)業(yè)報告》中拋出 460 億美元的 2024 年市場規(guī)模數(shù)據(jù)時,整個半導(dǎo)體行業(yè)都感受到了這場革命的烈度 ——19% 的同比增幅遠(yuǎn)超消費市場的狂歡節(jié)奏,而 2030 年 794 億美元的預(yù)測更意味著六年內(nèi)將誕生一個 “封裝界亞馬遜”。驅(qū)動這場爆發(fā)的核心,正是 AI 與高性能計算掀起的 “模塊化重構(gòu)浪潮”。

01 市場暴漲,AI與高性能計算驅(qū)動增長

曾經(jīng)僅應(yīng)用于特定高端產(chǎn)品的先進(jìn)封裝技術(shù),如今已成為消費電子大規(guī)模應(yīng)用的關(guān)鍵技術(shù),同時也為AR/VR、邊緣AI、航空航天及國防等新興市場提供關(guān)鍵支撐。

通信與基礎(chǔ)設(shè)施領(lǐng)域2024至2030年間增長率達(dá)到14.9%,成為所有細(xì)分市場中增速最快的領(lǐng)域。

其背后動力包括AI加速器、GPU、云數(shù)據(jù)中心大規(guī)模建設(shè),以及Chiplet架構(gòu)的普及。隨著系統(tǒng)復(fù)雜性提升,CoWoS、SoIC、EMIB、I-Cube及3D堆疊等先進(jìn)封裝技術(shù),正成為高性能芯片集成的核心技術(shù)方案。

02 技術(shù)革新,從制程上探到系統(tǒng)下沉

先進(jìn)封裝的技術(shù)發(fā)展方向主要朝兩個方向演進(jìn)。

一是制程上探,以單一功能芯片的高密度互聯(lián)和電氣性能優(yōu)化為核心的同構(gòu)集成結(jié)構(gòu)。這方面技術(shù)包括晶圓級封裝(WLP)、凸點工藝(Bumping)、硅通孔技術(shù)(TSV)和晶圓扇出技術(shù)(Fan-out)等。

二是系統(tǒng)下沉,以系統(tǒng)級封裝(SiP)為代表,將原本分散貼裝在PCB板上的多種功能芯片集成為一顆芯片,壓縮模塊體積、縮短電氣連接距離以提升芯片系統(tǒng)功能,代表了側(cè)重異構(gòu)集成的發(fā)展方向。

系統(tǒng)級封裝SiP的微小化優(yōu)勢顯而易見。通過改變模組及縮小尺寸,為終端產(chǎn)品提供更大的電池空間,集成更多的功能;通過異質(zhì)整合減少組裝廠的工序,加上更高度自動化的工藝在前端集成,降低產(chǎn)業(yè)鏈復(fù)雜度。

03 Chiplet引領(lǐng),顛覆傳統(tǒng)芯片設(shè)計范式

隨著芯片復(fù)雜性與制造成本提升,Chiplet架構(gòu)逐漸成為異構(gòu)集成和系統(tǒng)級平臺化發(fā)展的關(guān)鍵方向。

Chiplet是在多芯片模組(MCM)基礎(chǔ)上發(fā)展出的新型封裝架構(gòu),將單一復(fù)雜芯片拆分為多個小型、獨立且可復(fù)用的芯粒單元,并利用Flip-Chip、2.5D或3D等先進(jìn)封裝技術(shù)實現(xiàn)不同工藝、材料和功能芯片的靈活組合。

相比傳統(tǒng)單芯片SoC方案,Chiplet方案在良率、性能和成本方面優(yōu)勢明顯:小芯粒提升晶圓良率,降低生產(chǎn)風(fēng)險;多芯片分布式架構(gòu)滿足高效能計算和擴(kuò)展需求;異構(gòu)芯片的靈活集成提升設(shè)計靈活性,有效控制成本。

04 臺積電CoWoS,打造“性能巨無霸”

臺積電作為晶圓代工龍頭,正開發(fā)一種全新的CoWoS-L封裝技術(shù),預(yù)計最早于明年推出。

該技術(shù)支持面積高達(dá)4,719平方毫米的中介層(約為光罩極限的5.5倍),并需要100×100mm的基板。可集成多達(dá)12個HBM4高帶寬內(nèi)存堆棧,相比現(xiàn)在可實現(xiàn)跨越式提升。

臺積電預(yù)測,采用該技術(shù)制造的芯片將提供比當(dāng)今領(lǐng)先設(shè)計高出三倍半的計算性能,有可能滿足Nvidia Rubin GPU等即將推出的處理器的需求。

如此龐大的組件可以容納四個3D堆疊集成芯片系統(tǒng)、十二個HBM4內(nèi)存堆棧和多個I/O芯片,重新定義了高性能集成上限。

05 中國力量,國產(chǎn)先進(jìn)封裝加速突破

繁榮的背面往往藏著產(chǎn)業(yè)升級的“暗礁”——微米級的氣泡缺陷,正成為制約封裝良率和可靠性的“隱形殺手”。

屹立芯創(chuàng)致力于打造熱流與氣壓的研發(fā)與應(yīng)用平臺,公司專精于先進(jìn)封裝制程氣泡問題的解決,依托熱流和氣壓兩大核心技術(shù),持續(xù)研發(fā)以多領(lǐng)域除泡系統(tǒng)(De-Void System)和晶圓級真空貼壓膜系統(tǒng)(Wafer Vacuum Lamination System)為核心的兩大產(chǎn)品系統(tǒng)與應(yīng)用體系,提供多領(lǐng)域工藝制程中的氣泡和壓膜的整體解決方案。

目前,屹立芯創(chuàng)的智能除氣泡系統(tǒng)與晶圓級真空貼壓膜系統(tǒng),已在多家國內(nèi)封測龍頭企業(yè)實現(xiàn)規(guī)模化穩(wěn)定應(yīng)用,并成功通過半導(dǎo)體制造、電子組裝與汽車電子等領(lǐng)域頭部客戶的嚴(yán)格工藝驗證。該系統(tǒng)廣泛應(yīng)用于半導(dǎo)體封裝測試、人工智能芯片、機(jī)器人、新能源、汽車電子、5G通信及物聯(lián)網(wǎng)等多個關(guān)鍵領(lǐng)域。

06 先進(jìn)封裝,從“輔助工序”到“性能引擎”

當(dāng)全球先進(jìn)封裝市場向千億美元的目標(biāo)全速沖刺時,中國半導(dǎo)體裝備產(chǎn)業(yè)也正實現(xiàn)從“解決有無”到“技術(shù)引領(lǐng)”的關(guān)鍵轉(zhuǎn)變。這場圍繞“微米級氣泡”的工藝較量,看似是技術(shù)細(xì)節(jié)的優(yōu)化,實則是產(chǎn)業(yè)話語權(quán)的爭奪。

先進(jìn)封裝,已不再只是制造流程中的一環(huán),而是成為驅(qū)動AI算力持續(xù)飛躍的“性能引擎”。它重新定義了芯片的可能性,也正在重塑全球半導(dǎo)體競爭的新格局。

審核編輯 黃宇

-

先進(jìn)封裝

+關(guān)注

關(guān)注

2文章

533瀏覽量

1026

發(fā)布評論請先 登錄

“四算合一”算力平臺,芯片國產(chǎn)化率超九成,兼容8種國產(chǎn)AI芯片

智能算力為何必須先進(jìn)存力

什么是AI邊緣算力模組??

國產(chǎn)AI芯片真能扛住“算力內(nèi)卷”?海思昇騰的這波操作藏了多少細(xì)節(jié)?

什么是AI算力模組?

什么是AI算力模組?

借勢 RISC-V與 AI 浪潮,元石智算打造算力新范式

點動科技戰(zhàn)略聚焦AI智算,領(lǐng)航算力服務(wù)新征程

RAKsmart智能算力架構(gòu):異構(gòu)計算+低時延網(wǎng)絡(luò)驅(qū)動企業(yè)AI訓(xùn)練范式升級

大算力芯片的生態(tài)突圍與算力革命

智能算力最具潛力的行業(yè)領(lǐng)域

“堆”出萬億算力:先進(jìn)封裝如何驅(qū)動AI算力爆發(fā)

“堆”出萬億算力:先進(jìn)封裝如何驅(qū)動AI算力爆發(fā)

評論