該CDCUN1208LP是一個(gè)2:8扇出緩沖器,具有寬工作電源范圍、兩個(gè)通用差分/單端輸入以及帶邊沿速率控制的通用輸出(HCSL、LVDS或LVCMOS)。時(shí)鐘緩沖器支持 PCIe Gen1、Gen2 和 Gen3。其中一個(gè)器件輸入包括一個(gè)分頻器,提供 /1、/2、/4 或 /8 的分頻值。該CDCUN1208LP采用 32 引腳 QFN 封裝,可減少解決方案尺寸。該設(shè)備靈活且易于使用。某些引腳的狀態(tài)決定了上電時(shí)的設(shè)備配置。或者,CDCUN1208LP提供SPI/I^2^主機(jī)處理器控制設(shè)備設(shè)置的 C 端口。該CDCUN1208LP具有出色的附加抖動(dòng)性能和低功耗。輸出部分包括四個(gè)專(zhuān)用電源引腳,支持來(lái)自不同電源域的輸出端口運(yùn)行。這提供了在不同 LVCMOS 電平上切換的器件時(shí)鐘的能力,而無(wú)需外部邏輯電平轉(zhuǎn)換電路。

*附件:cdcun1208lp.pdf

特性

- 支持 PCIe Gen1、Gen2、Gen3

- 配置選項(xiàng)(通過(guò)引腳或SPI/I^2^C):

- 輸入類(lèi)型(HCSL、LVDS、LVCMOS)

- 輸出類(lèi)型(HCSL、LVDS、LVCMOS)

- 信號(hào)邊沿速率(慢、中、快)

- 時(shí)鐘輸入分頻值 (/1、/2、/4、/8) – 僅 IN2

- 低功耗和電源管理功能,包括1.8V工作和輸出使能控制

- 集成穩(wěn)壓器可改善 PSNR

- 優(yōu)異的加法抖動(dòng)性能

- 200 fs RMS(10 kHz 至 20 MHz),100 MHz 時(shí)的

LVDS - 160 fs RMS(10 kHz 至 20 MHz),100 MHz 時(shí)的

HCSL

- 200 fs RMS(10 kHz 至 20 MHz),100 MHz 時(shí)的

- 最大工作頻率:

- 差分模式:高達(dá) 400 MHz

- LVCMOS 模式:高達(dá) 250 MHz

- ESD 保護(hù)超過(guò) 2 kV HBM、500 V CDM

- 工業(yè)溫度范圍(–40°C 至 85°C)

- 寬電源范圍(1.8 V、2.5 V 或 3.3 V)

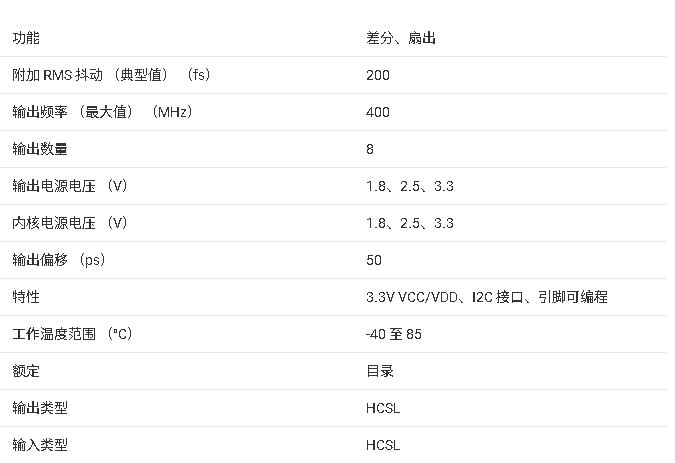

參數(shù)

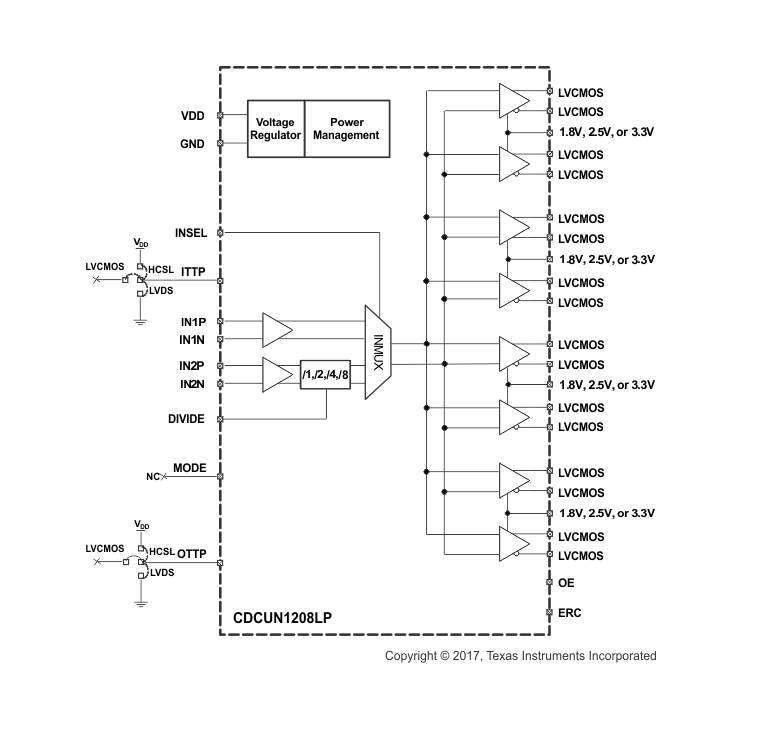

方框圖

?1. 產(chǎn)品概述?

CDCUN1208LP是德州儀器(TI)推出的一款低功耗2:8扇出緩沖器,支持PCIe Gen1/2/3協(xié)議,具有通用輸入(HCSL/LVDS/LVCMOS)和輸出配置。核心特性包括:

- ?輸入靈活性?:2個(gè)通用差分/單端輸入,支持HCSL、LVDS、LVCMOS信號(hào)類(lèi)型,輸入頻率范圍0.008-400 MHz(差分模式)或0.008-250 MHz(單端模式)。

- ?輸出配置?:8路輸出可獨(dú)立配置為HCSL、LVDS或LVCMOS,支持邊緣速率控制(慢/中/快),輸出頻率最高400 MHz(差分)或250 MHz(LVCMOS)。

- ?低功耗設(shè)計(jì)?:1.8V/2.5V/3.3V寬電源范圍,集成電壓調(diào)節(jié)器優(yōu)化電源噪聲抑制(PSNR)。

- ?低抖動(dòng)性能?:LVDS模式下100 MHz時(shí)附加抖動(dòng)僅200 fs RMS,HCSL模式下160 fs RMS。

?2. 關(guān)鍵特性?

- ?時(shí)鐘分頻?:IN2輸入支持/1、/2、/4、/8分頻(通過(guò)引腳或SPI/I2C配置)。

- ?智能輸入多路復(fù)用器?:支持自動(dòng)切換優(yōu)先級(jí)(IN1為默認(rèn)主輸入),切換時(shí)提供無(wú)毛刺過(guò)渡。

- ?輸出控制?:支持全局使能(OE引腳)或通過(guò)SPI/I2C獨(dú)立控制每路輸出。

- ?工業(yè)級(jí)溫度范圍?:-40°C至85°C。

?3. 應(yīng)用場(chǎng)景?

- 通信與計(jì)算系統(tǒng)

- 工業(yè)自動(dòng)化控制

- 醫(yī)療成像設(shè)備

- 專(zhuān)業(yè)音視頻及數(shù)字標(biāo)牌

- 電機(jī)驅(qū)動(dòng)

?4. 封裝與引腳?

- ?封裝?:32引腳VQFN(5mm×5mm),帶散熱焊盤(pán)。

- ?引腳功能?:

- 核心電源(VDD,引腳5)需優(yōu)先或與輸出電源(VDDOx)同步上電。

- 配置引腳(如MODE、ERC、OTTP)決定工作模式(引腳控制或SPI/I2C主機(jī)控制)。

?5. 技術(shù)參數(shù)?

- ?電源要求?:VDD與VDDOx可獨(dú)立供電(1.8V/2.5V/3.3V),支持混合電壓輸出。

- ?時(shí)序特性?:輸出使能至穩(wěn)定時(shí)鐘時(shí)間20 μs(LVDS),傳播延遲3.8-6.8 ns(取決于輸出模式)。

- ?ESD保護(hù)?:超過(guò)2 kV HBM、500 V CDM。

?6. 設(shè)計(jì)支持?

- ?布局建議?:縮短電源去耦電容走線,散熱焊盤(pán)需通過(guò)過(guò)孔陣列接地。

- ?參考設(shè)計(jì)?:提供PCIe時(shí)鐘分發(fā)方案(如搭配CDCM9102使用),包含終端電阻配置示例。

?7. 文檔與支持?

- 包含完整寄存器映射(SPI/I2C可編程)、時(shí)序圖及典型應(yīng)用曲線(如相位噪聲測(cè)試結(jié)果)。

- 支持通過(guò)TI官網(wǎng)獲取更新通知和技術(shù)社區(qū)(E2E)資源。

該文檔為硬件工程師提供從選型到布局的全流程設(shè)計(jì)指導(dǎo),適用于高精度時(shí)鐘分配需求場(chǎng)景。

-

緩沖器

+關(guān)注

關(guān)注

6文章

2227瀏覽量

48881 -

封裝

+關(guān)注

關(guān)注

128文章

9248瀏覽量

148614 -

端口

+關(guān)注

關(guān)注

4文章

1104瀏覽量

33962 -

PCIe

+關(guān)注

關(guān)注

16文章

1460瀏覽量

88400 -

LVCMOS

+關(guān)注

關(guān)注

1文章

142瀏覽量

11994

發(fā)布評(píng)論請(qǐng)先 登錄

ADH987S:3.3V低噪聲1:9扇出緩沖器DC-4.5 GHz數(shù)據(jù)表

SN65LVEP11 2.5 V/3.3V PECL/ECL 1:2扇出緩沖器數(shù)據(jù)表

SN65LVEL11 3.3V ECL 1:2扇出緩沖器數(shù)據(jù)表

SN65EL11 5v PECL/ECL 1:2扇出緩沖器數(shù)據(jù)表

具有通用輸入和輸出的CDCUN1208LP 400MHz低功耗2:8扇出緩沖器數(shù)據(jù)表

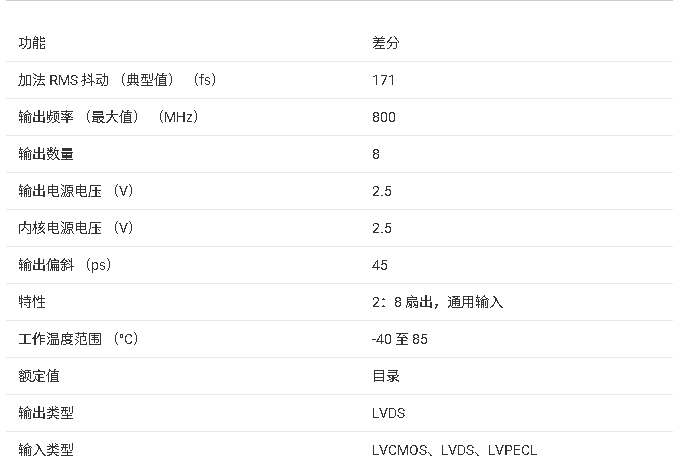

CDCLVD1208 2:8低加性抖動(dòng)LVDS緩沖器數(shù)據(jù)表

74AVC1T1004 1至4扇出緩沖器規(guī)格書(shū)

74AVC1T1022 1至4扇出緩沖器規(guī)格書(shū)

?CDCLVD1208 2:8低附加抖動(dòng)LVDS緩沖器技術(shù)文檔總結(jié)

?CDCUN1208LP 2:8扇出緩沖器技術(shù)文檔總結(jié)

?CDCUN1208LP 2:8扇出緩沖器技術(shù)文檔總結(jié)

評(píng)論