LMK61E2器件是一款超低抖動PLLatinum?可編程振蕩器,帶有一個小數N頻率合成器,集成了VCO,可生成常用的參考時鐘。輸出可配置為 LVPECL、LVDS 或 HCSL。

該器件具有通過片內EEPROM自啟動的功能,該EEPROM在工廠編程為產生156.25MHz LVPECL輸出。器件寄存器和EEPROM設置可通過I2C串行接口在系統內完全編程。內部電源調節提供出色的電源紋波抑制 (PSRR),從而降低供電網絡的成本和復雜性。該器件采用3.3V±5%單電源供電。

*附件:lmk61e2.pdf

該器件通過I2C串行接口提供精細和粗暴的頻率裕量選項,以支持系統設計驗證測試(DVT),例如標準合規性和系統時序裕量測試。

特性

- 超低噪音、高性能

- 抖動:90fs RMS,典型 fOUT > 100MHz

- PSRR:–70dBc,穩健的電源抗噪性

- 靈活的輸出格式;用戶可選擇

- LVPECL 高達 1GHz

- LVDS 高達 900MHz

- HCSL 高達 400MHz

- 總頻率容差為 ±50ppm

- 系統級功能

- 頻率裕度:精細和粗

- 內部EEPROM:用戶可配置的默認設置

- 其他功能

- 設備控制:I2C

- 3.3V 工作電壓

- 工業溫度范圍(–40°C 至 +85°C)

- 7mm × 5mm 8引腳封裝

- 使用 WEBENCH Power Designer 的LMK61E2創建自定義設計

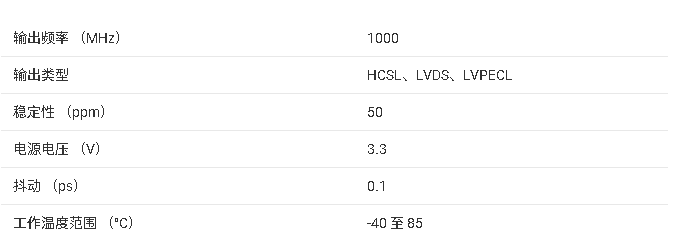

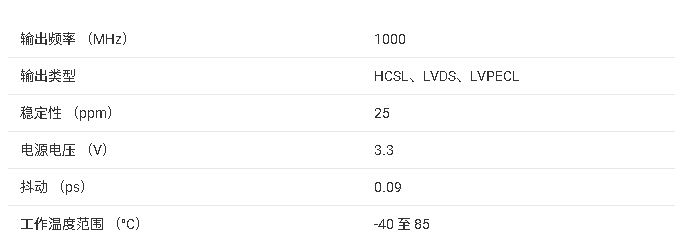

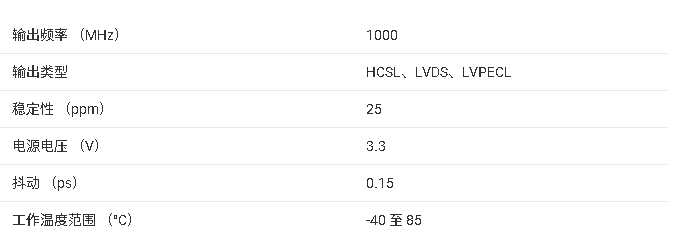

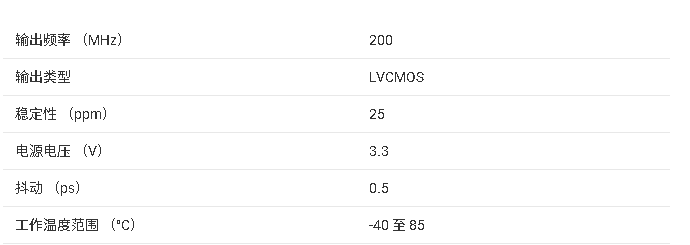

參數

?1. 產品概述?

LMK61E2是德州儀器(TI)推出的超低抖動可編程振蕩器,集成EEPROM和分數/整數型PLL,支持LVPECL、LVDS、HCSL輸出格式,適用于高速通信、網絡設備、醫療成像等高精度時鐘應用。核心特性包括:

- ?超低抖動?:典型值90fs RMS(輸出頻率>100MHz時)

- ?靈活輸出?:LVPECL(1GHz)、LVDS(900MHz)、HCSL(400MHz)

- ?高穩定性?:總頻率容差±50ppm,工業級溫度范圍(-40°C至85°C)

- ?可編程性?:通過I2C接口配置頻率、輸出格式及電源噪聲抑制(PSRR -70dBc)

?2. 關鍵特性?

- ?電源與封裝?:3.3V單電源供電,7mm×5mm 8引腳QFM封裝。

- ?系統功能?:支持頻率微調(Fine/Coarse Margining)、內部EEPROM存儲默認配置。

- ?應用場景?:替代晶體/SAW振蕩器,適用于交換機、路由器、FPGA時鐘、服務器存儲等。

?3. 技術細節?

- ?PLL架構?:集成4.6-5.6GHz VCO,支持分數/整數分頻,相位噪聲優化設計。

- ?輸出配置?:可通過寄存器編程選擇差分輸出類型(LVPECL需外部終端電阻)。

- ?抗干擾設計?:內置LDO電源調節,抑制電源噪聲。

?4. 編程與控制?

- ?I2C接口?:支持標準/快速模式(100/400kHz),7位目標地址可配置。

- ?寄存器映射?:38個8位寄存器,控制PLL分頻、環路濾波、輸出使能等。

- ?EEPROM存儲?:支持100次擦寫,上電自動加載配置。

?5. 典型應用設計?

- ?抖動優化?:建議使用WEBENCH? Clock Architect工具設計環路濾波器,最大化相位檢測頻率以降低噪聲。

- ?頻率微調?:通過調整晶振負載電容(精細)或輸出分頻器(粗調)實現。

- ?參考時鐘設計?:滿足高速SerDes系統對參考時鐘的嚴苛抖動要求(如10G以太網需<0.27ps RMS隨機抖動)。

?6. 文檔結構?

?總結?

LMK61E2憑借其低抖動、高集成度和可編程性,成為高性能時鐘系統的理想選擇,尤其適用于對時序精度要求苛刻的通信和計算設備。設計時需結合工具優化PLL參數,并注意電源和布局以發揮最佳性能。

-

合成器

+關注

關注

0文章

316瀏覽量

27972 -

串行接口

+關注

關注

3文章

520瀏覽量

45295 -

LVPECL

+關注

關注

2文章

75瀏覽量

18876 -

可編程振蕩器

+關注

關注

0文章

54瀏覽量

7979

發布評論請先 登錄

LMK61E2 可編程,25ppm,156.25 LVPECL 啟動

LMK61E07具有內部EEPROM的超低抖動可編程振蕩器數據表

具有內部EEPROM的LMK61E0M超低抖動可編程振蕩器數據表

?LMK61E2 超低抖動可編程振蕩器技術文檔總結

?LMK61E2 超低抖動可編程振蕩器技術文檔總結

評論