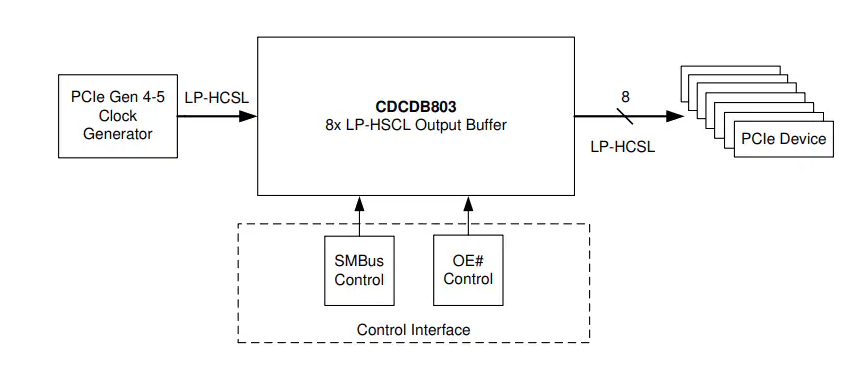

該CDCDB803是一款符合DB800ZL標(biāo)準(zhǔn)的 8 輸出 LP-HCSL 時(shí)鐘緩沖器,能夠?yàn)?PCIe Gen 1-6、QuickPath 互連 (QPI)、UPI、SAS 和 SATA 接口分配參考時(shí)鐘。SMBus 接口和八個(gè)輸出使能引腳允許單獨(dú)配置和控制所有八個(gè)輸出。該CDCDB803是一種DB800ZL導(dǎo)數(shù)緩沖液,達(dá)到或超過DB800ZL規(guī)范中的系統(tǒng)參數(shù)。它還達(dá)到或超過DB2000Q規(guī)范中的參數(shù)。該CDCDB803采用6mm×6mm、48引腳VQFN封裝。

*附件:cdcdb803.pdf

特性

- 8 個(gè) LP-HCSL 輸出,具有可編程集成 85 Ω(默認(rèn))或 100 Ω差分輸出端接

- 8 個(gè)硬件輸出使能 (OE#) 控件

- PCIE Gen 6濾波器后的附加相位抖動:20 fs,RMS(最大值)

- PCIE Gen 5濾波器后的附加相位抖動:25 fs,RMS(最大值)

- 濾波器DB2000Q后的附加相位抖動:38 fs,RMS(最大值)

- 支持通用時(shí)鐘 (CC) 和單獨(dú)基準(zhǔn) (IR) 架構(gòu)

- 擴(kuò)頻兼容

- 輸出到輸出偏斜:< 50 ps

- 輸入到輸出延遲:< 3 ns

- 故障安全輸入

- 可編程輸出壓擺率控制

- 9 個(gè)可選的 SMBus 地址

- 3.3V 內(nèi)核和 IO 電源電壓

- 硬件控制的低功耗模式 (PD#)

- 電流消耗:最大 72 mA

- 6mm × 6mm 48引腳VQFN封裝

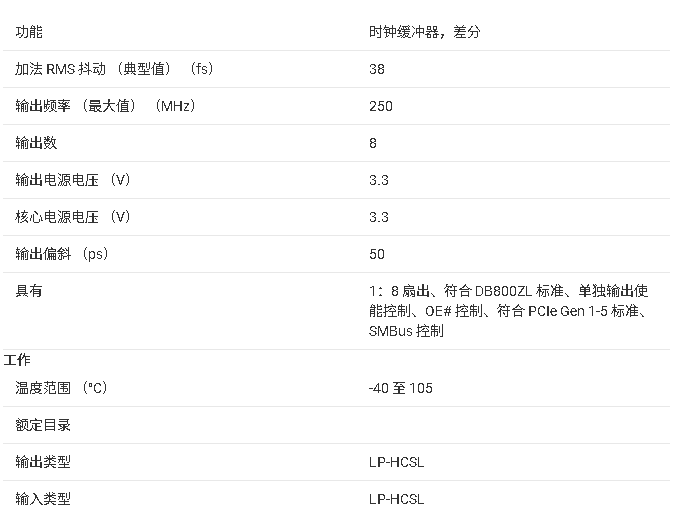

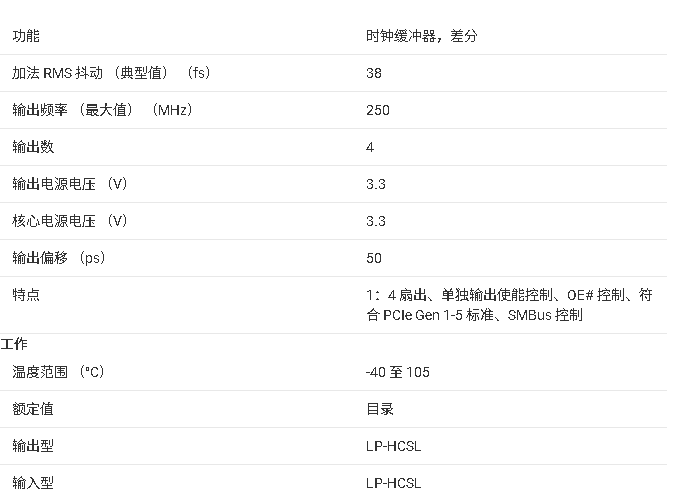

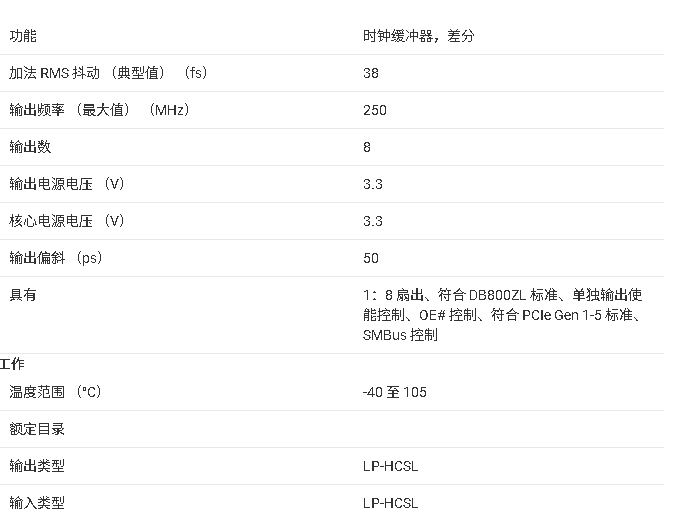

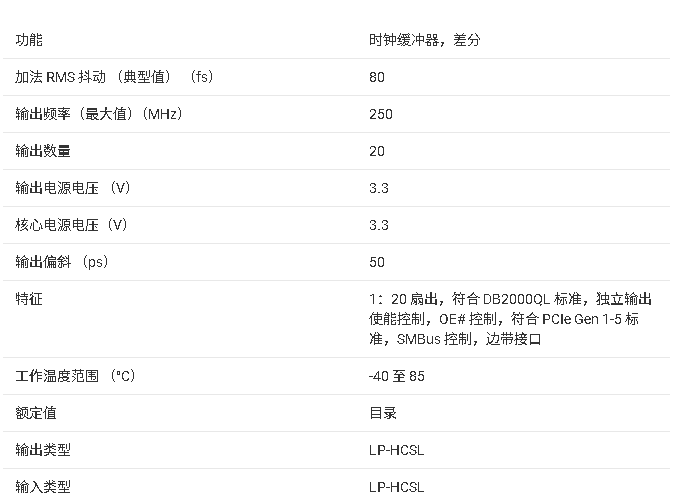

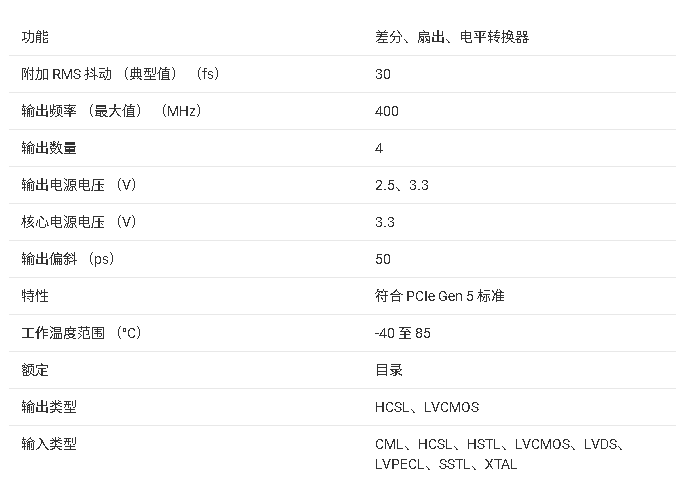

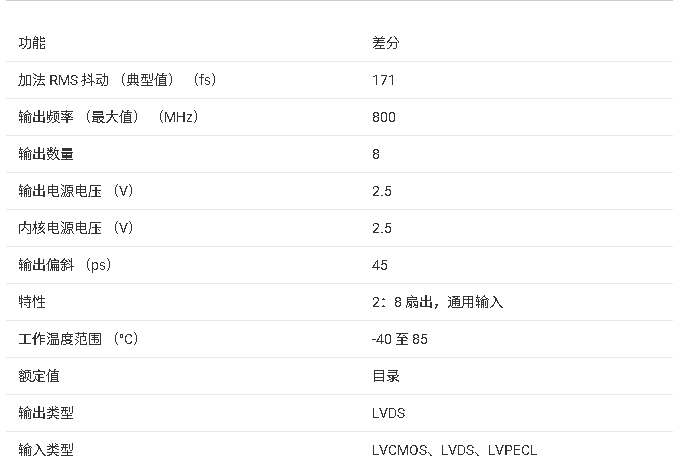

參數(shù)

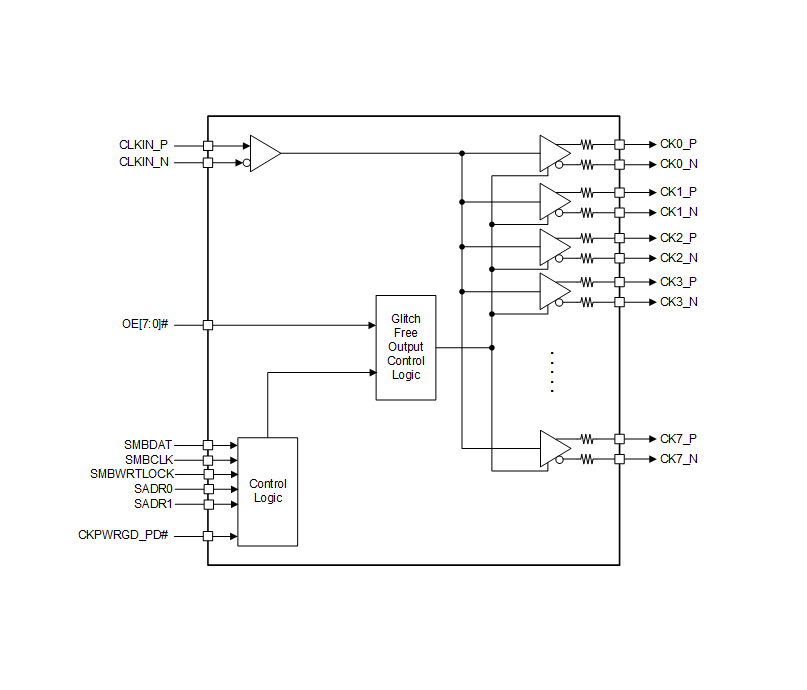

方框圖

?1. 產(chǎn)品概述?

CDCDB803是德州儀器(TI)推出的DB800ZL兼容型8通道LP-HCSL時(shí)鐘緩沖器,專為PCIe Gen 1至Gen 6、QPI、UPI、SAS和SATA接口設(shè)計(jì)。其核心特性包括:

- ?8路輸出?:支持可編程集成85Ω(默認(rèn))或100Ω差分終端阻抗。

- ?低抖動性能?:PCIe Gen 6濾波后加性相位抖動僅20 fs(RMS最大值),Gen 5為25 fs,DB2000Q濾波為38 fs。

- ?靈活控制?:8個(gè)硬件輸出使能(OE#)引腳,支持SMBus接口配置,9種可選SMBus地址。

- ?高效能?:3.3V供電,最大電流消耗72 mA,6mm×6mm 48引腳VQFN封裝。

?2. 關(guān)鍵特性?

- ?輸出配置?:每通道獨(dú)立使能,支持Common Clock(CC)和Individual Reference(IR)架構(gòu)。

- ?時(shí)序性能?:輸出間偏斜<50 ps,輸入至輸出延遲<3 ns。

- ?應(yīng)用場景?:微服務(wù)器、存儲區(qū)域網(wǎng)絡(luò)、硬件加速器、機(jī)架服務(wù)器等。

?3. 功能描述?

- ?輸入時(shí)鐘?:支持50-250 MHz LP-HCSL差分輸入,兼容擴(kuò)展頻譜。

- ?輸出控制?:通過SMBus寄存器或硬件OE#引腳實(shí)現(xiàn)通道開關(guān),支持低功耗模式(PD#)。

- ?集成設(shè)計(jì)?:內(nèi)置終端電阻和電源濾波,減少外部元件需求。

?4. 電氣參數(shù)?

- ?工作條件?:3.3V±5%供電,環(huán)境溫度-40°C至105°C。

- ?抖動指標(biāo)?:PCIe Gen 6/5/4加性抖動分別為20/25/60 fs(RMS)。

- ?SMBus接口?:兼容SMBus 2.0,支持400 kHz通信速率。

?5. 封裝與布局?

- ?封裝?:48引腳VQFN(6mm×6mm),帶裸露焊盤以優(yōu)化散熱。

- ?布局建議?:推薦85Ω(或100Ω)差分阻抗布線,縮短傳輸線長度以減少反射。

?6. 設(shè)計(jì)資源?

- ?開發(fā)支持?:提供TICS Pro軟件用于寄存器配置和EVM編程。

- ?文檔更新?:可通過TI官網(wǎng)訂閱產(chǎn)品變更通知。

?7. 典型應(yīng)用?

-

接口

+關(guān)注

關(guān)注

33文章

9572瀏覽量

157496 -

時(shí)鐘緩沖器

+關(guān)注

關(guān)注

2文章

273瀏覽量

51952 -

封裝

+關(guān)注

關(guān)注

128文章

9307瀏覽量

148951 -

引腳

+關(guān)注

關(guān)注

16文章

2116瀏覽量

55959

發(fā)布評論請先 登錄

CDCDB803適用于第1代到第6代PCIe、符合DB800ZL標(biāo)準(zhǔn)的8輸出時(shí)鐘緩沖器數(shù)據(jù)表

CDCDB800適用于第1代到第6代PCIe、符合DB800ZL標(biāo)準(zhǔn)的8輸出時(shí)鐘緩沖器數(shù)據(jù)表

CDCDB800/803超低附加抖動、8路輸出PCIe Gen1至Gen5時(shí)鐘緩沖器

?CDCDB400 4輸出時(shí)鐘緩沖器技術(shù)文檔總結(jié)

?CDCDB800 8輸出時(shí)鐘緩沖器技術(shù)文檔總結(jié)

?CDCDB2000 20輸出時(shí)鐘緩沖器技術(shù)文檔總結(jié)

?CDCS504-Q1 時(shí)鐘緩沖器和時(shí)鐘乘法器技術(shù)文檔總結(jié)

?LMK00334四輸出時(shí)鐘緩沖器與電平轉(zhuǎn)換器技術(shù)文檔總結(jié)

?CDCLVD1208 2:8低附加抖動LVDS緩沖器技術(shù)文檔總結(jié)

?PCIe Gen7時(shí)鐘緩沖技術(shù)解析:TI CDCDB400芯片深度剖析

Texas Instruments CDCDB803用于PCIe?第1代至第5代的8輸出時(shí)鐘緩沖器數(shù)據(jù)手冊

?CDCDB803 8輸出時(shí)鐘緩沖器技術(shù)文檔總結(jié)

?CDCDB803 8輸出時(shí)鐘緩沖器技術(shù)文檔總結(jié)

評論