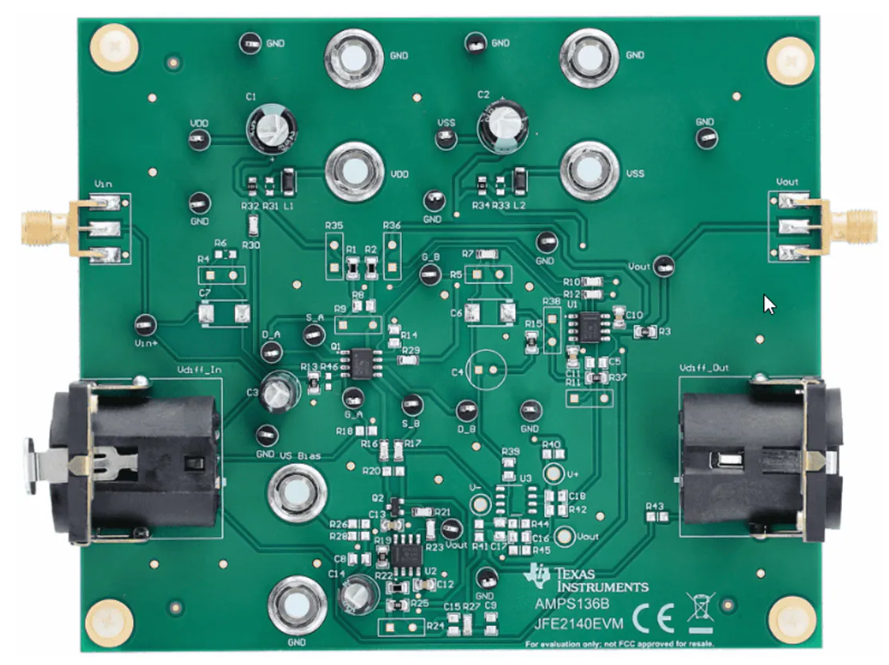

Texas Instruments JFE2140EVM JFET評估模塊 (EVM) 設計用于對JFE2140器件進行基本功能評估。JFE2140是一款雙通道超低噪聲低柵極電流音頻N通道JFET。Texas Instruments JFE2140EVM采用閉環前置放大器配置,在±5V分立式電源上提供60dB增益。可以針對各種電路配置對用戶進行修改。

數據手冊:*附件:Texas Instruments JFE2140EVM JFET評估模塊 (EVM)數據手冊.pdf

特性

板布局

JFE2140EVM評估模塊技術解析:超低噪聲JFET前置放大器的設計與應用

產品概述

JFE2140EVM評估模塊是德州儀器(TI)推出的一款專為高性能音頻和傳感器信號調理設計的評估平臺,基于JFE2140匹配對離散JFET器件。該模塊采用SOIC-8封裝,提供完整的超低噪聲前置放大器解決方案,特別適合需要極高信噪比的應用場景。

?核心特性?:

- ?超低噪聲性能?:0.9nV/√Hz輸入參考噪聲(5mA偏置時)

- ?靈活偏置調節?:工作電流可調范圍50μA至20mA

- ?專業級接口?:SMA和XLR雙輸入/輸出連接方式

- ?多功能測試點?:關鍵節點均設有測試點便于測量

- ?可擴展設計?:提供電阻/電容焊盤選項用于信號路徑優化

評估模塊硬件設計

1. 電源架構設計

?供電系統配置?:

- ?默認雙電源?:±5V供電(VDD=+5V, VSS=-5V)

- ?關鍵電源管理?:

- 100nF陶瓷電容(C1,C2)用于高頻去耦

- 10μF電解電容(C3,C14)用于低頻濾波

- 2.5kΩ電阻(R1,R2)建立偏置電壓

?熱管理要點?:

- 推薦環境溫度:15°C至35°C

- 高偏置電流時需監控Q1(JFE2140)溫升

2. 信號路徑設計

?輸入電路?:

- 交流耦合輸入通過10μF電容(C3)

- 1MΩ電阻(R13)設置柵極偏置電壓

- SMA接口(J1/J8)和測試點(Vin)并行接入

?輸出電路?:

- OPA202運放構成增益級

- 49.9Ω隔離電阻(R3)提升容性負載驅動能力

- 輸出電壓范圍:±2V(相對于中電源電壓)

關鍵電路分析

1. 超低噪聲前置放大器

評估模塊核心電路為閉環前置放大器:

- ?第一級?:JFE2140構成共源放大器

- ?第二級?:OPA202運放提供主增益

- ?反饋網絡?:R37(10kΩ)和R15(10Ω)設定1001V/V增益

- ?尾電流源?:典型值2mA(通過R19/R22設置)

?性能指標?:

- 中頻增益:60dB(1000V/V)

- 帶寬特性:-3dB帶寬約100kHz

- 輸入阻抗:1MΩ(由R13決定)

2. PCB布局要點

專業六層板設計:

- ?頂層?:

- 關鍵信號路徑最短化

- 對稱差分走線布局

- 電源去耦電容靠近器件引腳

- ?內層?:

- 完整地平面降低噪聲

- 電源層分割設計

- 多過孔連接降低阻抗

- ?測試點分布?:

- 20個多功能測試點覆蓋所有關鍵節點

- 黑色TH測試點便于示波器連接

典型應用場景

評估指南

1. 快速啟動步驟

- 連接雙電源:

- J1.3接+5V,J1.1接-5V

- 最大供電電壓±18V

- 信號輸入連接:

- 單端模式:J1(SMA IN+),J3接地

- 差分模式:J1/J3差分輸入

- 輸出測量:

- SMA接口J8或測試點Vout

- 典型輸出幅度1Vpp(對應1mVpp輸入)

2. 配置建議

- ?增益調整?:修改R37/R15比值

- ?帶寬優化?:調整C10-C13電容值

- ?偏置設置?:通過R19/R22調節尾電流

- ?ESD防護?:操作時佩戴防靜電手環

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

JFET

+關注

關注

3文章

202瀏覽量

23531 -

雙通道

+關注

關注

5文章

1206瀏覽量

35408 -

低噪聲

+關注

關注

0文章

509瀏覽量

24674 -

評估模塊

+關注

關注

0文章

1629瀏覽量

8381

發布評論請先 登錄

相關推薦

熱點推薦

放大器,低噪聲前置放大器參數,前置放大器廠家

低噪聲放大器是噪聲系數很低的放大器。一般用作各類無線電接收機的高頻或中頻前置放大器,以及高靈敏度電子探測設備的放大電路。ATA-5000系列

發表于 09-15 11:59

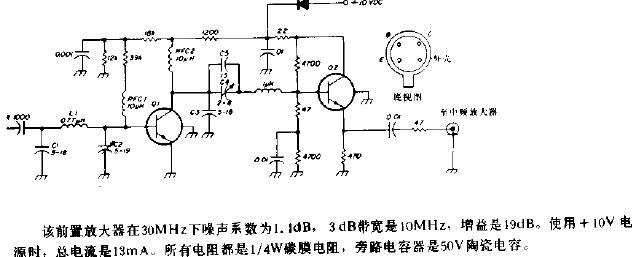

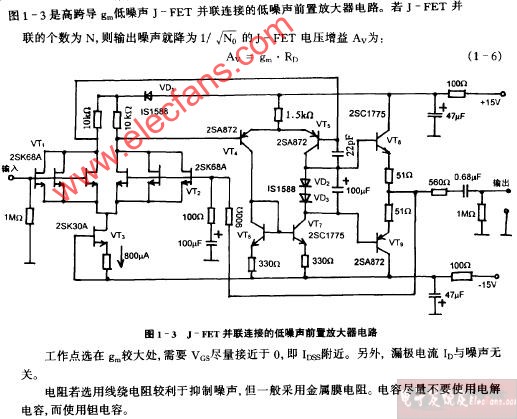

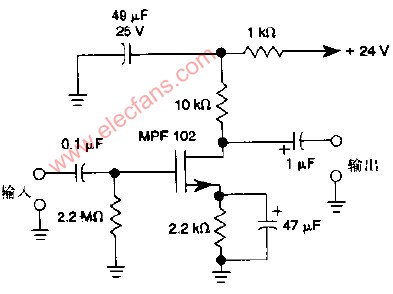

分立元件設計的低噪聲前置放大器實用電路

分立元件設計的低噪聲前置放大器實用電路::根據級聯網絡及噪聲理論,本文采用分立元件設計了一種低噪聲前置放大器實用電路.測試結果表明該電路比目

發表于 09-25 12:11

?318次下載

低噪聲前置放大器電路的設計方法

前置放大器在音頻系統中的作用至關重要。本文首先講解了在為家庭音響系統或PDA設計前置放大器時,工程師應如何恰當選取元件。隨后,詳盡分析了噪聲的來源,為設計低噪聲前

發表于 06-07 08:17

?133次下載

低噪聲前置放大器電路的設計步驟

低噪聲前置放大器電路的設計步驟

前置放大器在音頻系統中的作用至關重要。本文首先講解了在為家庭音響系統或PDA設計前置放大器時,工程師應如何恰當選取元件。

發表于 12-26 14:32

?6056次閱讀

前置放大器電路噪聲分析

前置放大器在音頻系統中的作用至關重要。本文首先講解了在為家庭音響系統或PDA設計前置放大器時,工程師應如何恰當選取元件。隨后,詳盡分析了噪聲的來源,為設計低噪聲

發表于 10-24 14:53

?3599次閱讀

AD8332-EVALZ:雙VGA、超低噪聲前置放大器和可編程RIN評估板數據表

AD8332-EVALZ:雙VGA、超低噪聲前置放大器和可編程RIN評估板數據表

發表于 05-18 15:53

?1次下載

JFE2140EVM評估模塊技術解析:超低噪聲JFET前置放大器的設計與應用

JFE2140EVM評估模塊技術解析:超低噪聲JFET前置放大器的設計與應用

評論