文章來源:老虎說芯

原文作者:老虎說芯

本文介紹了NAND Flash的原理、結構、工藝和應用。

NAND Flash的基本原理和結構

NAND Flash是什么?NAND Flash(閃存)是一種非易失性存儲器技術,主要用于數據存儲。與傳統的DRAM或SRAM不同,NAND Flash在斷電后仍能保存數據。它通過電荷的存儲與釋放來實現數據的存儲。

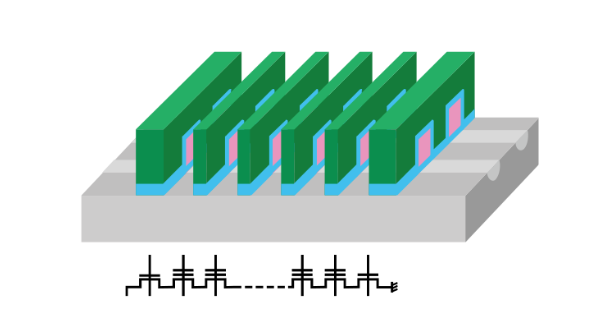

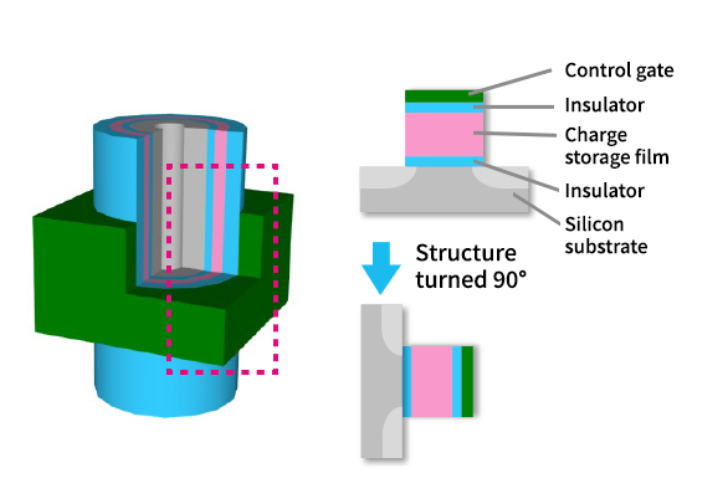

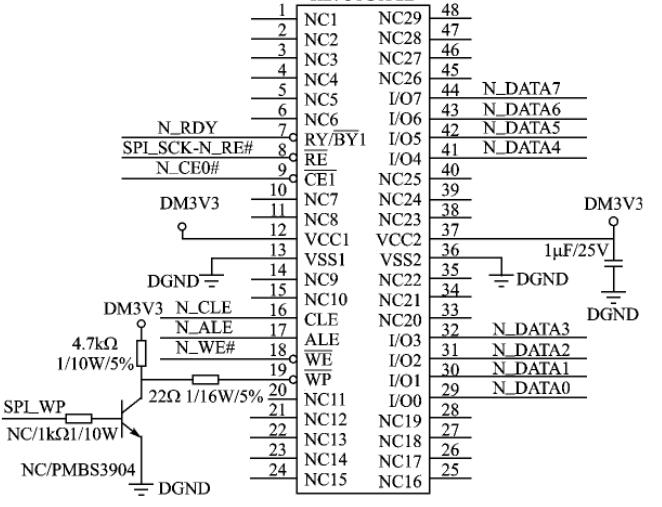

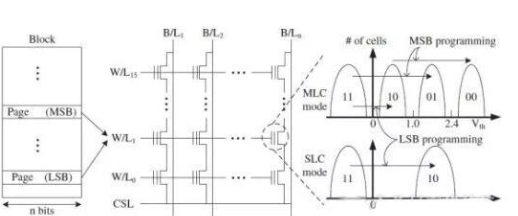

圖:NAND Flash的排列結構

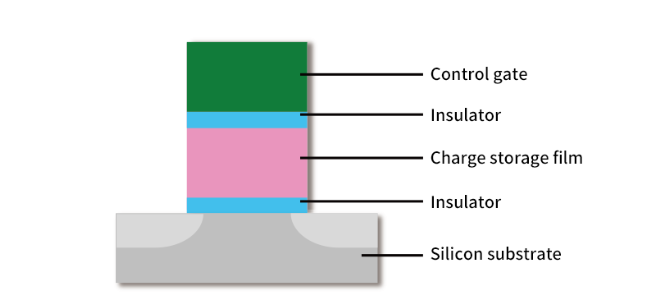

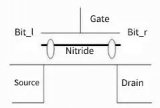

基本單元結構:NAND Flash的基本存儲單元是一個浮柵晶體管(Floating Gate Transistor)。每個晶體管對應一個存儲單元,存儲的信息是通過控制浮柵上的電荷實現的。多個存儲單元通過串聯方式形成一個NAND存儲單元(通常為8到32個單元串聯),以提高密度和降低成本。

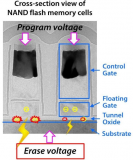

圖:存儲cell的器件結構

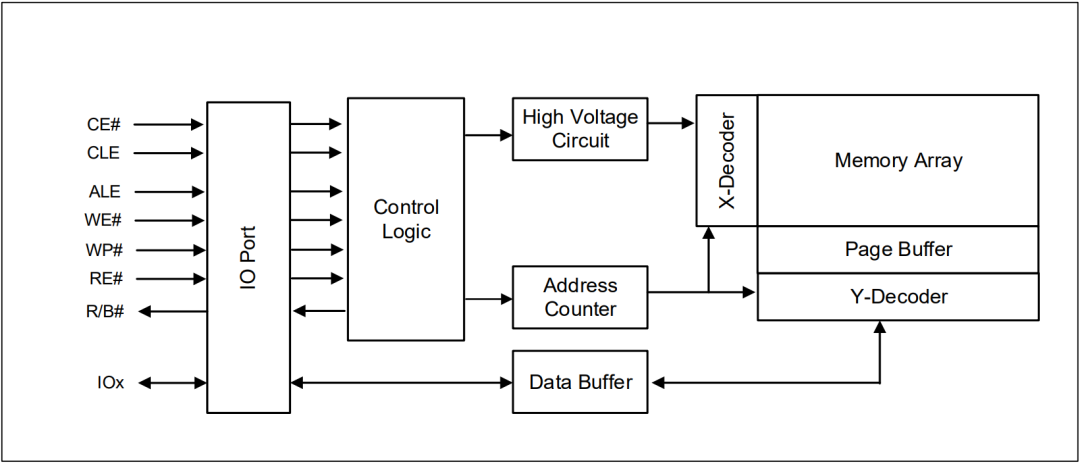

NAND Flash的工作原理

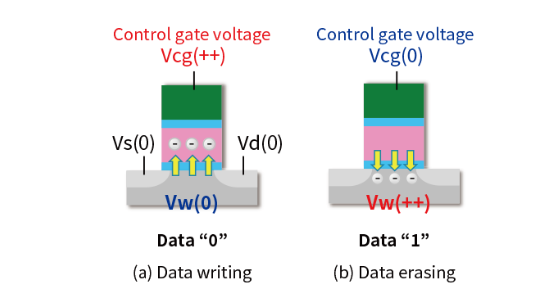

寫入過程(編程):在編程(寫入)過程中,通過施加高電壓,電子被注入浮柵,改變浮柵上的電荷,進而影響晶體管的導通狀態,從而表示不同的存儲信息(通常是‘0’或‘1’)。

圖:數據寫入和擦除操作

擦除過程:NAND Flash采用塊擦除的方式。通過施加反向電壓,浮柵上的電子被移除,恢復晶體管的原始狀態。擦除通常是對整個塊進行操作,而不是單個字節。

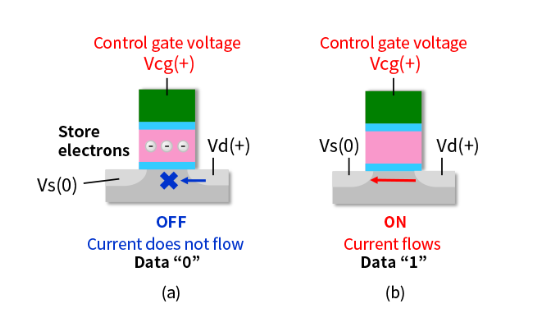

讀取過程:讀取過程中,通過檢測浮柵上的電荷狀態,可以確定存儲單元的導通狀態,從而讀取出存儲的信息。

圖:數據0和數據1的表示方式

NAND Flash的工藝與技術挑戰

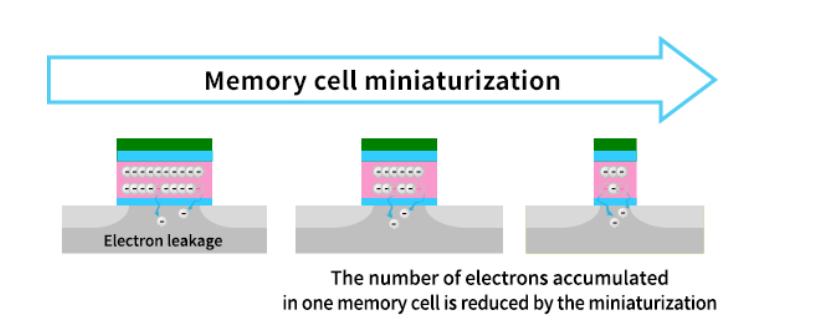

工藝節點縮減:隨著技術的發展,NAND Flash的工藝節點不斷縮減(如從38nm到19nm,再到更小的工藝節點),這帶來了更高的存儲密度和更低的成本,但也增加了制造的復雜性和良率的挑戰。

圖:存儲Cell小型化的趨勢

可靠性優化:隨著存儲單元尺寸的縮小,電荷存儲的穩定性下降,導致耐用性和數據保留時間減少。為了解決這一問題,工程師需要不斷優化工藝參數,增強可靠性。例如,通過增加擦寫周期數(如38nm工藝下的500K次循環)來提高耐用性。

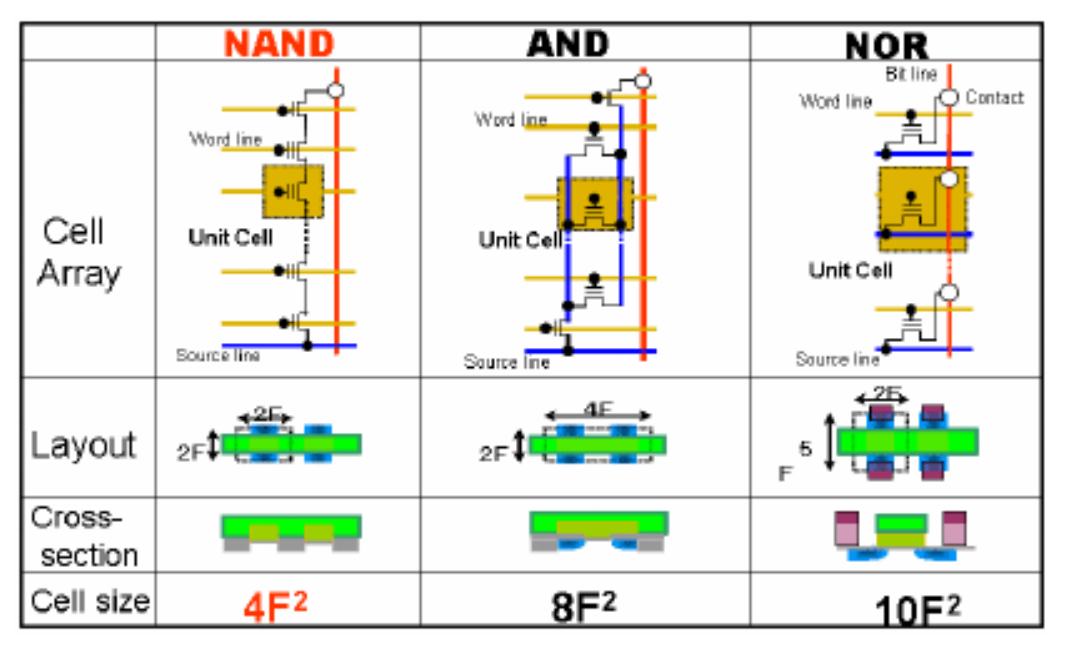

設計規則收縮與布局優化:在更小的工藝節點上,設計規則(Design Rule)需要不斷縮小,同時布局也需要優化,以在更小的空間內實現更多的存儲單元。Mask的減少和規則的優化是提高產量和降低成本的重要手段。

圖:NAND、AND、NOR的CELL陣列對比

NAND Flash的應用與發展趨勢

應用領域:NAND Flash廣泛應用于各種存儲設備,如固態硬盤(SSD)、USB閃存、存儲卡等。在智能手機、平板電腦和服務器中也得到了廣泛應用。

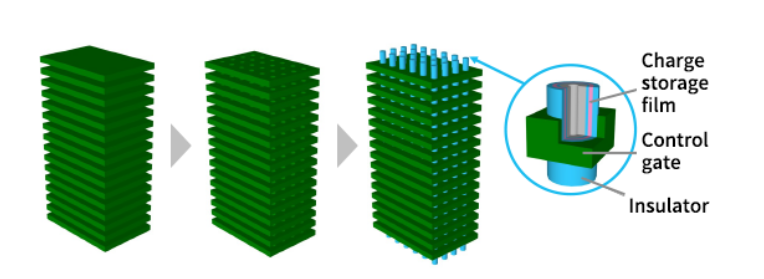

圖:3D NAND的結構細節

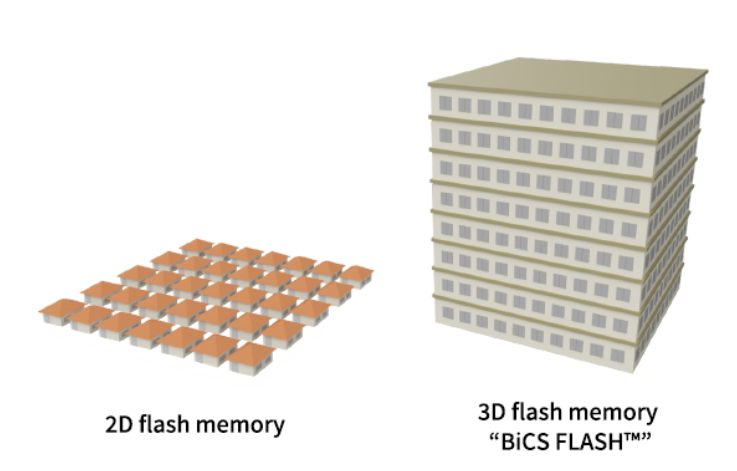

3D NAND技術:隨著二維平面縮小的困難逐漸增加,3D NAND技術應運而生。3D NAND通過將存儲單元垂直堆疊,大幅提高了存儲密度,成為目前NAND Flash發展的主要方向。

圖:2D Flash和3D Flash的概念示意對比

圖:2D Flash和3D Flash的器件結構對比

未來挑戰與展望

進一步的可靠性與耐久性提升:隨著存儲單元的進一步縮小,未來將面臨更多的可靠性挑戰。新的材料和結構創新可能是解決這一問題的關鍵。

新型存儲技術的競爭:隨著新型存儲技術(如ReRAM、MRAM等)的發展,NAND Flash將面臨新的競爭,持續的工藝創新和成本優化將是保持競爭力的關鍵。

-

DRAM

+關注

關注

40文章

2375瀏覽量

188412 -

NAND

+關注

關注

16文章

1749瀏覽量

140545 -

FlaSh

+關注

關注

10文章

1720瀏覽量

154831 -

存儲器

+關注

關注

39文章

7716瀏覽量

170998

原文標題:NAND Flash的原理、結構、工藝挑戰、應用及未來發展

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

并行Nand Flash的結構和基本工作過程

從NOR Flash到NAND Flash和SD NAND,從底層結構到應用差異

DDS基本原理及性能特點

STM32基本原理簡介

NAND Flash 的存儲結構以及NAND Flash的接口控制設計

NOR FLASH和NAND FLASH基本結構和特點介紹

NAND Flash的基本原理和結構

NAND Flash的基本原理和結構

評論