一前言

在當今高密度電子設計中,電磁兼容性(EMC)已成為決定產品成敗的關鍵指標。其中,輻射測試作為EMC評估的關鍵環節之一,其測試結果與PCB回路設計質量密切相關。優化回路設計不僅能有效抑制輻射干擾,更能將產品研發周期縮短30%以上,顯著降低后期整改成本。

本文將結合典型工程案例,揭示那些鮮為人知的設計細節與優化技巧。

二案例背景

客戶產品為一款車載顯示屏,客戶在進行CISPER 25-CLASS3等級傳導測試中出現在50MHz附近出現包絡超標情況,數據如下圖:

圖1 產品傳導測試數據

按照我們測試的經驗,出現包絡超標第一時間想到有可能是DC-DC電源導致,我們再仔細看數據中不是標準的“鼓包”,而是很多“細針”組成的包絡,把超標區域放大,我們可以看到數據是由有規律“細針”構成,對數據進行標點確認后,發現該“細針”頻率為500KHz,結合產品DC-DC電源的頻率,我們基本可以鎖定確認為該產品的一級電源的開關頻率。

圖2 放大后的測試數據

三整改過程

1.檢查原理圖

在知道問題點后,對客戶原理圖進行檢查,首先檢查客戶原理圖上一級電源的濾波電路,發現客戶無論是電源芯片電源輸入端的去耦電容以及芯片SW輸出的吸收電路以及高頻電容、BOOT引腳中串聯的RC電路等,都有設計在電路之中。電源濾波電路設計合理且全面,理論上以及不會出現數據超標情況,需要進一步分析。

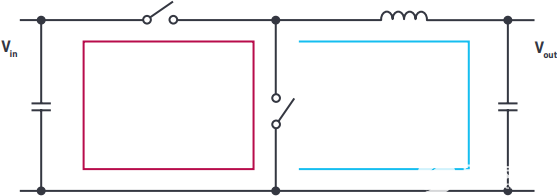

2.檢查PCB

原理圖沒有問題,那問題有可能和PCB有關。進一步檢查客戶的PCB,濾波電路的回路都是遵循高頻噪聲回路面積最小原則,也沒有太大問題。直到檢查客戶背面PCB,有一根電源長走線非常不合理,如下圖:

圖3 電源長走線設計不合理

這樣的長走線有兩個問題:

(2)長走線強行把PCB地分割,導致回路變大。

針對前面兩個問題進行整改:

(1)在電源長走線增加電容和磁珠濾波,減小天線效應,發現作用不大,說明問題更有可能是回路變大導致。

(2)用銅箔多點跨接被電源長走線分割的GND,優化回路,效果明顯改善,數據如下圖:

圖4 整改后數據

四總結

在EMC問題中,不僅要重視原理圖的濾波設計,更要注重PCB的布局布線,特別是控制好信號回路。這樣能有效降低噪聲能量,從而規避潛在問題,實現事半功倍的效果。

-

pcb

+關注

關注

4387文章

23711瀏覽量

420048 -

emc

+關注

關注

174文章

4307瀏覽量

190098 -

電磁兼容性

+關注

關注

7文章

481瀏覽量

34597

發布評論請先 登錄

EMC案例分享之回路

EMC案例分享之回路

評論