USB Type-C連接器于2014年底面世,一經推出便得到廣泛應用,并已成為連接各類電子設備與外圍設備的行業標準。除對稱結構帶來的明顯優勢外,相較于早期USB接口,它還具備其他優點,包括能夠實現非常高的數據傳輸速率(高達80 Gbps Tx和80 Gbps Rx),并可通過單個端口提供高達240 W的功率。在本白皮書中,Nexperia探討了在交流耦合超高速數據線中,將高電壓ESD保護二極管置于位置A,或將低電壓ESD保護二極管置于位置B,哪種布局可提供更有效的短路保護。

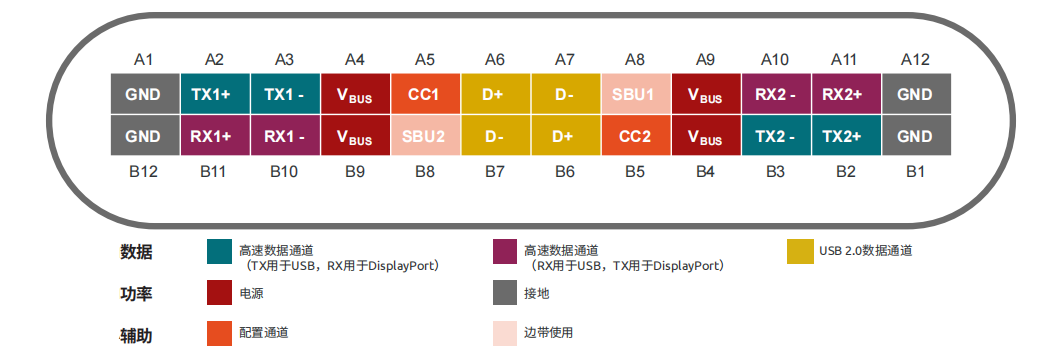

△ 圖1 USB Type-C接口的引腳分配

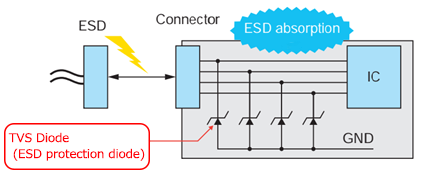

盡管USB PD規范包含多種安全機制1,但USB設計人員仍面臨一個關鍵問題:如何在VBUS電源線因使用不合規連接器或系統而與數據線發生電接觸時,確保接口得到有效保護。最新USB 4標準規定超高速線對必須采用交流耦合方式,增加了提供充分保護的設計復雜性。圖1所示為USB Type-C連接器的引腳排列。

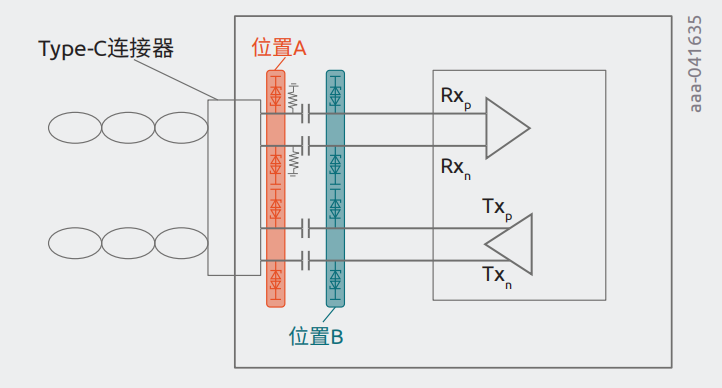

圖2顯示了在交流耦合的超高速線路中,ESD保護二極管的兩種放置位置:一種靠近連接器端(位置A),另一種位于交流耦合電容與受保護收發器IC之間(位置B)。

△ 圖2 超高速數據線中ESD保護二極管的兩種放置選項

研究ESD應力對交流耦合電容的影響

初步研究主要分析ESD應力對交流耦合電容的影響,因為在位置B放置保護二極管會導致這些電容在ESD事件中失去保護。

Nexperia設計中常用的多種0402’’交流耦合電容2在承受持續時間為100 ns、上升時間為1 ns (1/100 ns)的傳輸線脈沖(TLP)測試時,均展現出良好的ESD魯棒性。測試結果顯示,330 nF電容器在高達約60 A的TLP沖擊下未出現損壞跡象,而220 nF電容器在高達約55 A TLP下也未出現損壞(分別相當于IEC 61000-4-2標準約30 kV和27 kV的脈沖水平)。

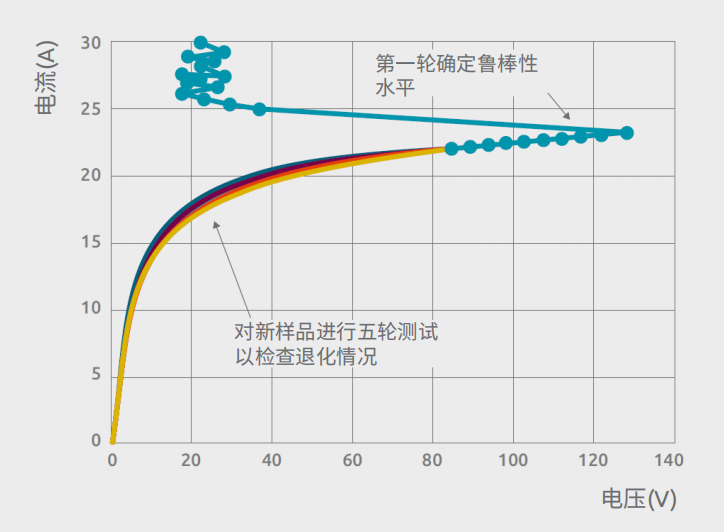

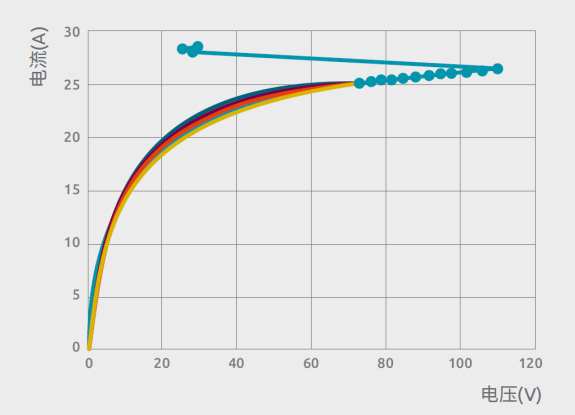

同時,還測試了兩家制造商提供的25 V額定電壓、220 nF 0201’’交流耦合電容。測試結果如圖4所示。首先,在對新器件進行五次1/100 ns TLP脈沖測試(最高22 A,低于其魯棒性閾值)之前,先測定了其魯棒性極限(藍色曲線)。此器件在這些測試過程中未顯示出任何退化。同樣,對于來自第二家制造商的魯棒性更強的電容器(圖4),在五次高達25 A的1/100 ns TLP脈沖下,也未觀察到任何器件退化跡象。

△ 圖3 魯棒性較低的0201’’耦合電容的測試結果

△ 圖4 魯棒性較高的0201’’耦合電容的測試結果

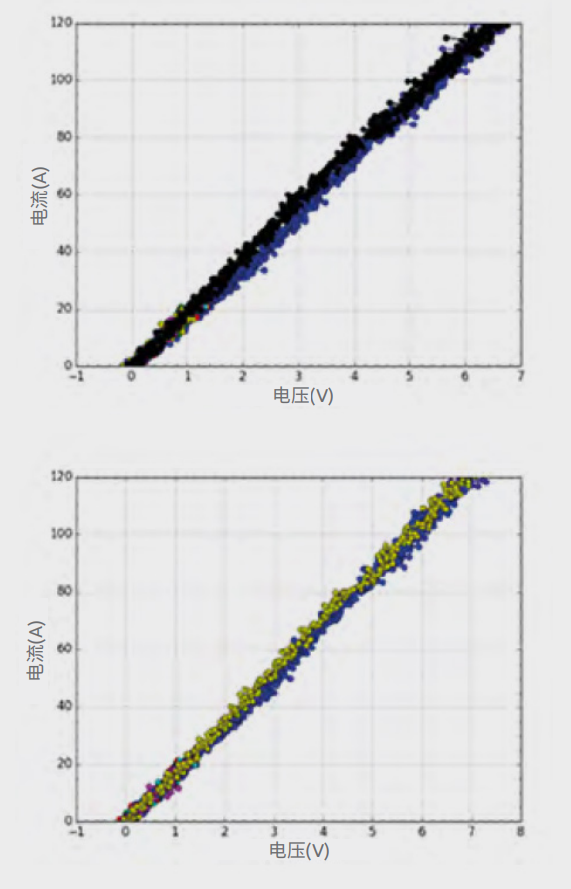

隨后,采用持續時間為5 ns、上升時間為600 ps (0.6/5 ns)且電流高達120 A的超快TLP (vfTLP)對兩家制造商提供的電容器樣品進行了進一步測試(圖5),結果同樣未發現任何器件退化跡象。

△ 圖5 采用0.6/5 ns且電流高達120 A的超快TLP對兩個額定電壓為25 V的220 nF 0201’’ 電容進行測試

研究表明,交流耦合電容在高達120 A、0.6/5 ns的超快TLP下仍具有良好的魯棒性,因此可以推斷:ESD脈沖引發的退化現象的 根源在于能量水平,而非峰值電壓。這使得22 A 1/100 ns的TLP 測試等同于11 kV的IEC 61000-4-2脈沖測試。換言之,所有被研究的交流耦合電容的魯棒性均超越了IEC 61000-4-2接觸放電的4級標準。

測試期間,通過使用下拉電阻,避免了可能出現的電荷積聚。

研究ESD應力對受保護IC的影響

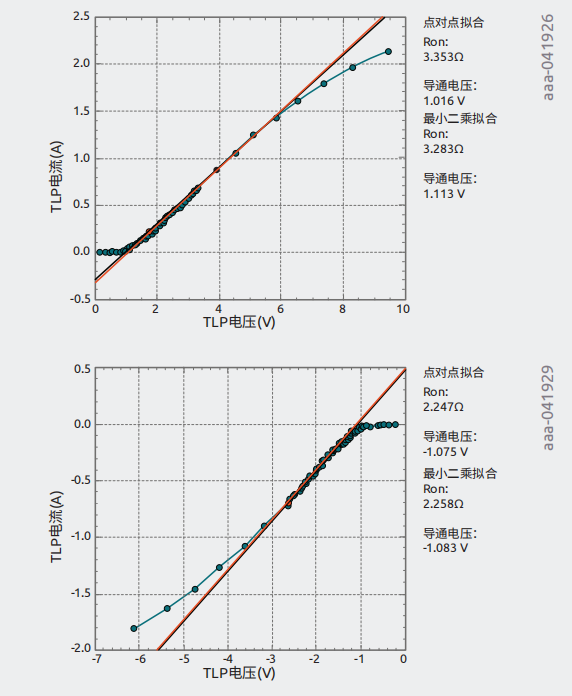

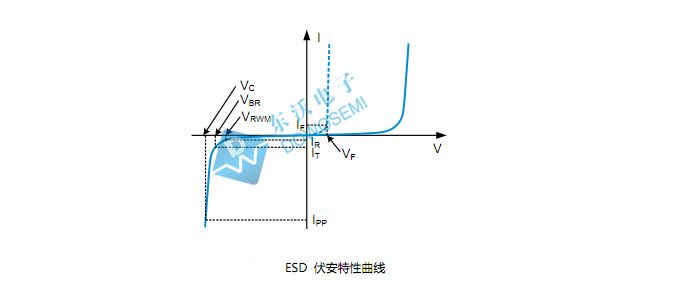

Nexperia對若干用于超高速數據線的收發器IC(重定時器和重驅動器器件)展開了研究,發現它們的TLP特性與一個串聯著電阻的正向偏置二極管極為相似(圖6)。這表明這些IC的芯片內部ESD保護電路在極低電壓(1 V至1.5 V之間)下就會導通。因此,所采用的外部ESD保護二極管必須具備較低的觸發電壓,以便在受保護IC受損前限制流入的ESD電流。

△ 圖6 典型USB超高速IC的1/100 TLP結果顯示,芯片內部ESD保護電路在約1 V時會導通

△ 圖7 通過漏電流測量評估芯片內部ESD保護電路是否受損

綜上所述,對多款超高速收發器IC的測試結果表明:

? 芯片內部ESD保護電路通常在約1 V時導通

? 以上示例的芯片內部ESD保護電路在2 A 1/100 ns TLP下受損

? 該IC的芯片內部ESD保護電路在約5 A 0.6/5 ns vf-TLP脈沖下受損

導致損壞的vfTLP電流水平提高,這表明該IC對脈沖能量的敏感度高于對峰值鉗位電壓的敏感度。

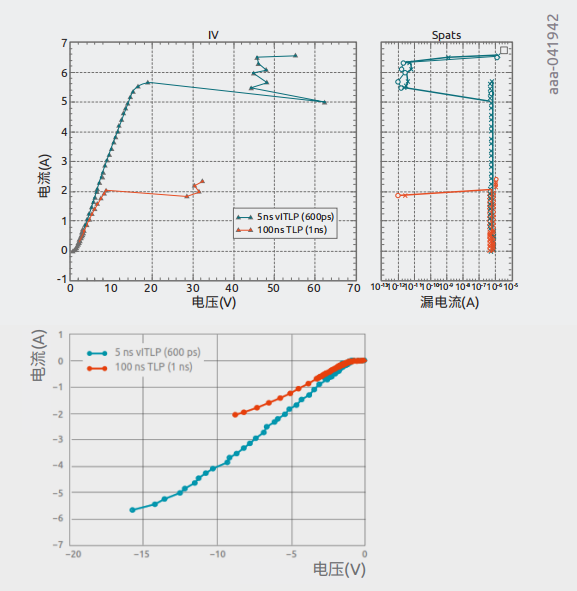

上述IC對ESD保護后的殘余鉗位電壓仍較為敏感。Nexperia也對可承受高達6 A TLP的系統進行了測試。但這些系統仍會在約1 V 電壓下開始導通,并對瞬變電流進行分流。為了評估此類系統在不同ESD保護策略下的表現,Nexperia采用高效的系統級ESD 設計(SEED)模擬結合測試板測量的方法,使用如下所示的測試裝置3,對比了將高電壓保護二極管置于位置A與將低電壓二極管置于位置B的效果。

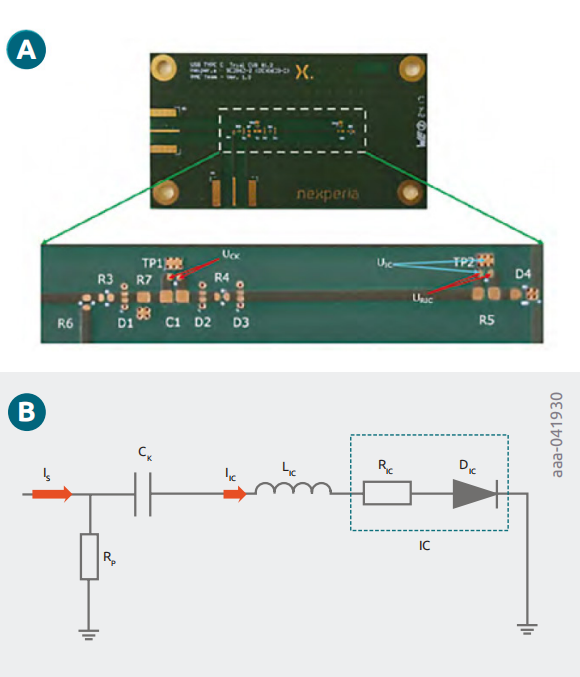

△ 圖8 交流耦合超高速數據線的測試接口,從左到右依次為:連接器(未顯示)、位置A的ESD保護元件位置、下拉電阻、交流耦合電容、位置B的ESD保護元件位置、IC替代電路(電阻加二極管)

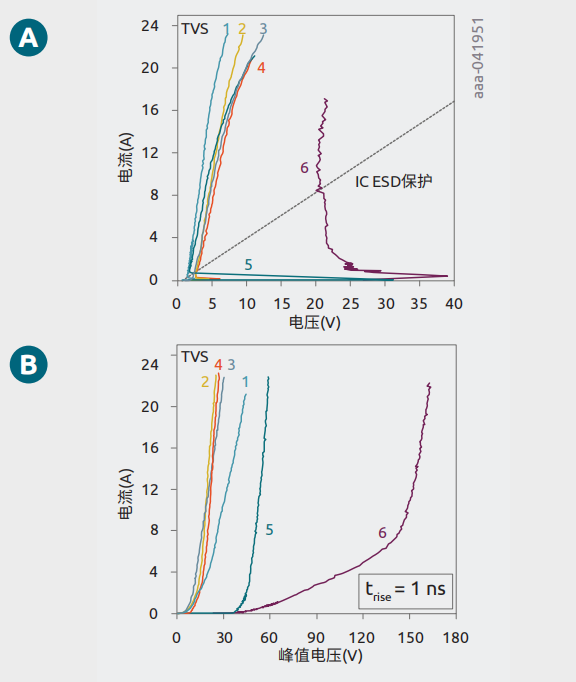

△ 圖9 額定電壓為1 V的ESD保護二極管(1-4)的TLP曲線比較(A)和峰值鉗位電壓比較(B)

四個額定電壓為1 V的不同ESD保護器件(1-4)放置在位置B處,兩個額定電壓為18-24 V的ESD保護器件(5-6)放置在位置A處。圖9為測試結果。虛線表示IC ESD保護模型的曲線。

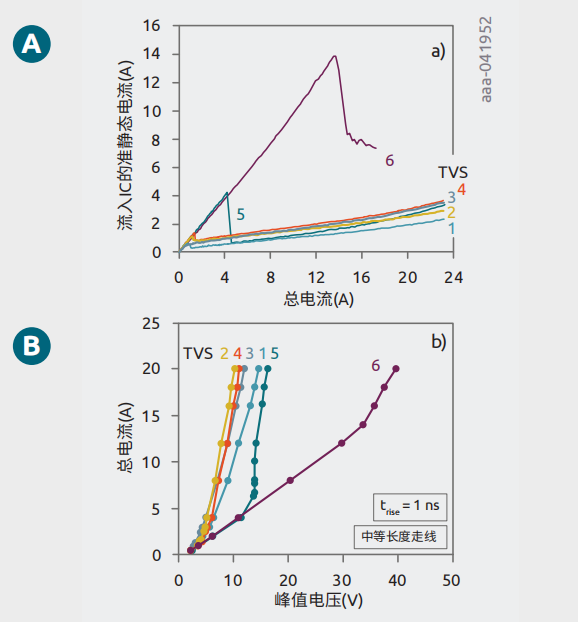

△ 圖10 收發器IC所經受的TLP電流(A)和峰值電壓(B)

器件5或許可以保護在器件觸發前能承受超過4 A TLP電流的收發器,但圖6和圖7中所示的IC則無法承受這種類型的脈沖。無論何種情況,與位置A相比,位置B處的所有四個保護器件對IC施加的總體瞬變電流應力都要低得多。

這些結果表明,在位置B處使用低電壓保護二極管可實現更出色的系統級ESD保護,因為保護器件在流經IC的瞬變電流較低時便開始對收發器實施保護。

交流耦合電容能否防范短路?

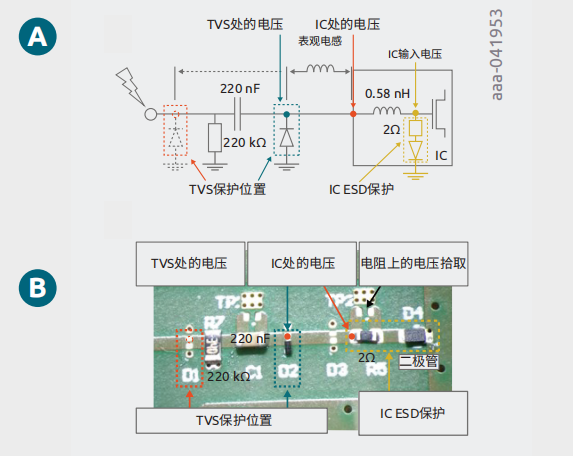

簡而言之,交流耦合電容不能有效防范VBUS與超高速數據線之間發生短路帶來的風險。詳細研究發現,在發生(或解除)短路時,瞬變電流能夠穿過交流耦合電容,使IC暴露于微秒級的浪涌脈沖之下。為開展評估4,使用了一塊測試板,上面配備了如上述ESD測試中所描述的IC等效電路。

△ 圖11 (A)使用超高速線路元件和測試點的測試PCB。(B)在位置A處設有高壓ESD或沒有ESD保護的測量設置

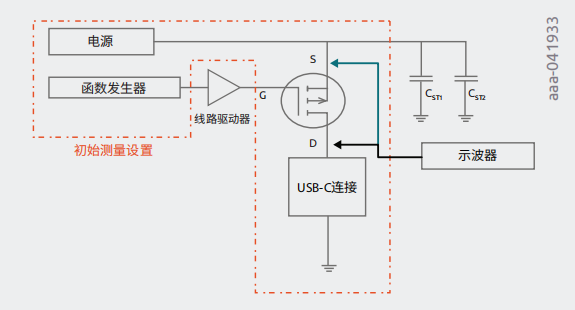

短路是通過一個驅動MOSFET的信號發生器來引發的,其上升持續時間約為50 ns(圖12)。

△ 圖12 短路驅動電路

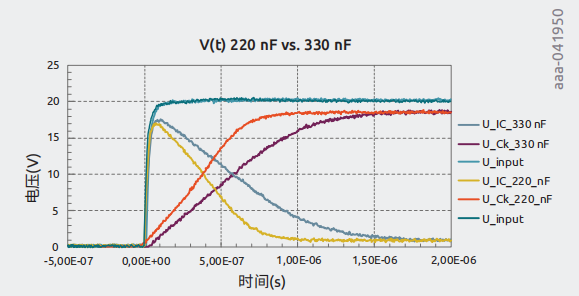

如圖13所示,施加此類短路會產生不同的波形。輸入端(U_input)信號上升至20 V,上升時間為數十納秒,而交流耦合電容 (U_ck)上的壓降上升時間則取決于電容值,符合預期。IC替代電路(U_IC)上的壓降持續時間同樣取決于電容值,兩者共同產生了一個持續時間約為1 μs的浪涌脈沖。

△ 圖13 施加在帶有220 nF或330 nF電容的交流耦合超高速線路上的20 V短路電壓波形

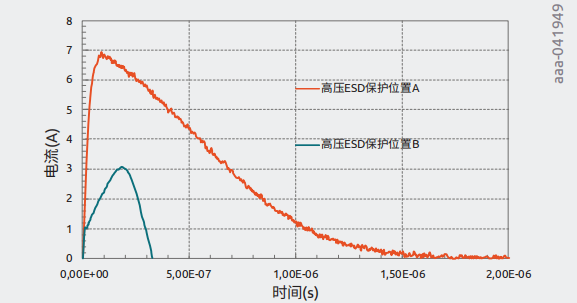

圖14顯示了當超高速收發器IC在ESD保護二極管的保護下,受到此類短路影響時流入IC的電流隨時間的變化。

△ 圖14 對交流耦合電容施加20 V短路時,通過超高速IC替代電路的浪涌電流

結論

研究顯示,超高速USB接口中使用的交流耦合電容的ESD魯棒性超過了IEC61000-4-2 4級標準接觸放電的要求,表明它們不太會成為系統級保護中的薄弱環節。相比之下,受保護收發器IC更可能因不理想的ESD保護策略導致的高鉗位電壓而失效。

對比不同的保護策略發現,在位置A(距離IC較遠的位置)放置高壓ESD二極管(>20 V)時,會在短路事件中產生較大且持續時間較長的浪涌電流(例如,在20 V VBUS下約為7 A,持續 1 μs)。即便ESD保護器件本身未受損,但這種級別的應力超過了多數IC能夠承受的范圍。

而在位置B(即位于交流耦合電容與收發器IC之間)使用低壓ESD二極管(約1 V),則能顯著降低因VBUS短路至交流耦合數據線所引發的浪涌事件電流的強度和持續時間。在我們的研究中,該方案在ESD和短路事件中均表現出更出色的保護性能。通過加入一個小的串聯電阻,可以進一步降低瞬變電流,但需考慮其對射頻性能的潛在影響。

這種放置方式雖與傳統做法相沖突(傳統做法是通過增加IC與ESD器件的間距,利用走線寄生電感實現保護),但優勢顯著,在位置B采用低壓器件的好處,遠勝于位置A使用高壓保護器件時,依靠較長走線所帶來的傳統優勢。

我們建議,在可能發生VBUS短路的系統中,應優先在位置B使用低壓ESD二極管,以實現更可靠的保護。

隨著USB供電EPR支持高達48 V的VBUS電壓,確保有效的低壓保護變得愈發重要。

本文作者

Steffen Holland,Nils Duchow,Stefan Seider

Nexperia (安世半導體)

Nexperia(安世半導體)總部位于荷蘭,是一家在歐洲擁有豐富悠久發展歷史的全球性半導體公司,目前在歐洲、亞洲和美國共有12,500多名員工。作為基礎半導體器件開發和生產的領跑者,Nexperia(安世半導體)的器件被廣泛應用于汽車、工業、移動和消費等多個應用領域,幾乎為世界上所有電子設計的基本功能提供支持。

Nexperia(安世半導體)為全球客戶提供服務,每年的產品出貨量超過1,000億件。這些產品在效率(如工藝、尺寸、功率及性能)方面成為行業基準,獲得廣泛認可。Nexperia(安世半導體)擁有豐富的IP產品組合和持續擴充的產品范圍,并獲得了IATF 16949、ISO 9001、ISO 14001和ISO 45001標準認證,充分體現了公司對于創新、高效、可持續發展和滿足行業嚴苛要求的堅定承諾。

Nexperia:效率致勝。

-

二極管

+關注

關注

149文章

10278瀏覽量

176164 -

ESD

+關注

關注

50文章

2363瀏覽量

178658 -

交流耦合

+關注

關注

0文章

44瀏覽量

12561 -

Nexperia

+關注

關注

1文章

796瀏覽量

58834

原文標題:白皮書分享 | 為什么ESD二極管的放置位置至關重要:優化交流耦合超高速數據線的保護

文章出處:【微信號:Nexperia_China,微信公眾號:安世半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

什么是肖特基二極管?肖特基二極管的工作原理和作用

超高速二極管反向恢復時間測試

肖特基二極管與快恢復二極管的區別

超低電容ESD保護二極管系列應用SRV05-4 SR05

USB2.0高速端口的ESD保護二極管陣列NUP4114UPXV6

瞬態抑制二極管和ESD靜電二極管的區別

瞬態抑制二極管和ESD靜電二極管的區別有哪些?

快恢復二極管和肖特基二極管的區別有哪些?

Littelfuse推出瞬態抑制二極管陣列 為超高速接口提供超低電容ESD保護

TVS二極管陣列是什么,它的優勢有哪些

交流耦合超高速數據線中ESD二極管的放置位置研究

交流耦合超高速數據線中ESD二極管的放置位置研究

評論