1986年,工程師John Hennessy在斯坦福大學(Standford)首次公布了MIPS CPU架構,截至去年這款CPU架構已經經歷了30年的發展與實踐。‘簡潔’和‘優雅’是這款精簡指令集MIPS處理器的代名詞。這也是很多人嘗試用它來開始學習微處理器設計的原因。

Imagination大學計劃(IUP)項目是面向廣大的教育工作者的。它的目的是讓教師更好的幫助學生使用MIPS架構處理器學習如何編程。MIPS CPU的低功耗特性是專業物聯網(IoT)項目的最佳選擇,學習如何使用它才能夠讓學生更好的投入到物聯網(IoT)蓬勃發展的浪潮中。

Robert Owen,一名已經管理IUP項目很多年的工程師,將舉辦首次網絡研討會,對這個項目進行全面的介紹。

這次網絡研討會將會討論以下三方面:

? 從移動類應用的角度來講圖形技術教學

? 在FPGA平臺上MIPS處理器內核的使用,以獨特的方式展示一個計算機的架構和組成,處理器是如何成為一個SoC(System on Chip,片上系統)核心的

? 對于新上來的本科生如何向他們更好的介紹微控制器(MCUs),引導他們了解物聯網的互聯世界

IUP教學項目有很多的優勢,采用低成本的硬件平臺、免費使用的SDK開發工具、豐富的教學資料(完全針對教師而非營銷材料)以及活躍的技術論壇提供各種幫助。

項目中使用到的硬件平臺來自很多合作伙伴,基于Microchip MIPS PIC32的MCU、Digilent(迪芝倫)PIC32 ChipKit開發套件以及Xilinx提供的FPGA開發平臺。

-

處理器

+關注

關注

68文章

20250瀏覽量

252204 -

FPGA

+關注

關注

1660文章

22408瀏覽量

636211 -

物聯網

+關注

關注

2945文章

47818瀏覽量

414810 -

Xilinx

+關注

關注

73文章

2200瀏覽量

131116

發布評論請先 登錄

TAS3103A數字音頻處理器:特性、架構與應用詳解

MAX262微處理器可編程通用有源濾波器:設計與應用指南

【「龍芯之光 自主可控處理器設計解析」閱讀體驗】--全書概覽與概述

云拼接處理器的性能如何?

ARM入門學習方法分享

格羅方德擬收購人工智能和處理器IP供應商MIPS

龍芯處理器支持WINDOWS嗎?

HXS320F28027數字信號處理器(32位RISC-V DSP)

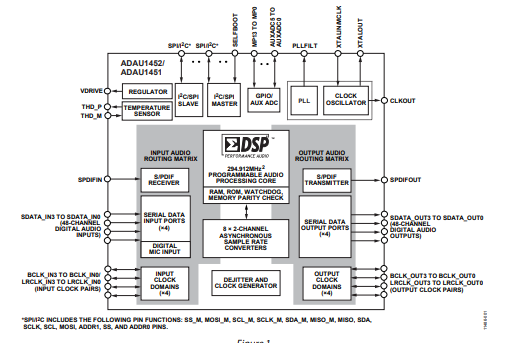

ADAU1452/ADAU1451/ADAU1450 SigmaDSP數字音頻處理器技術手冊

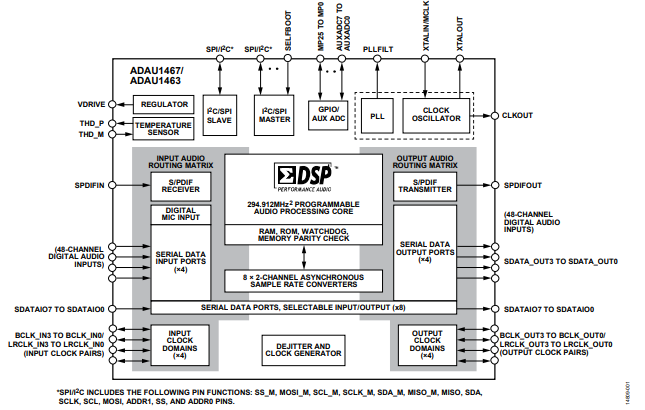

ADAU1463/ADAU1467 具有擴展內部存儲器和 I/O功能的Sigma DSP數字音頻處理器技術手冊

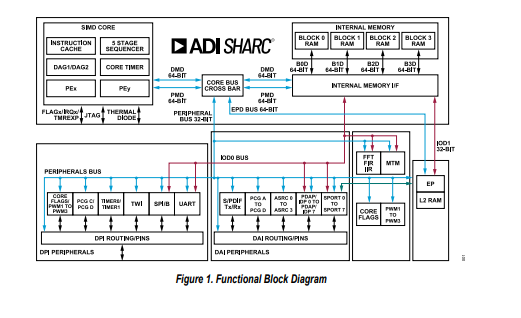

ADSP1802 SHARC處理器技術手冊

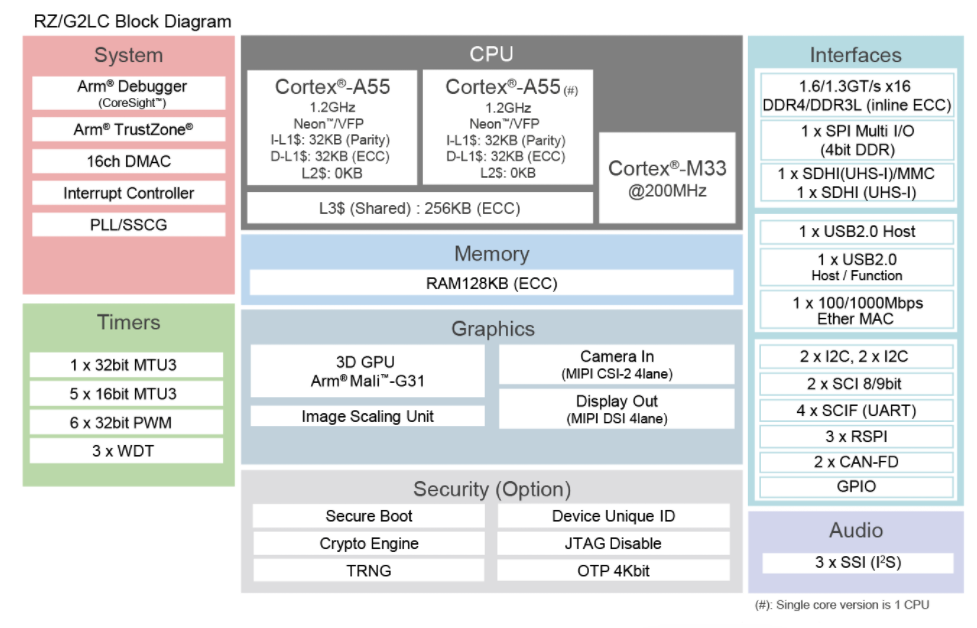

配備3D圖形加速引擎的通用微處理器RZ/G2LC數據手冊

使用MIPS架構處理器學習如何編程_從移動類應用的角度來講圖形技術教學

使用MIPS架構處理器學習如何編程_從移動類應用的角度來講圖形技術教學

評論