聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

ADI

+關注

關注

151文章

46104瀏覽量

277304 -

pll

+關注

關注

6文章

982瀏覽量

138180 -

雜散信號

+關注

關注

1文章

5瀏覽量

7370

發布評論請先 登錄

相關推薦

熱點推薦

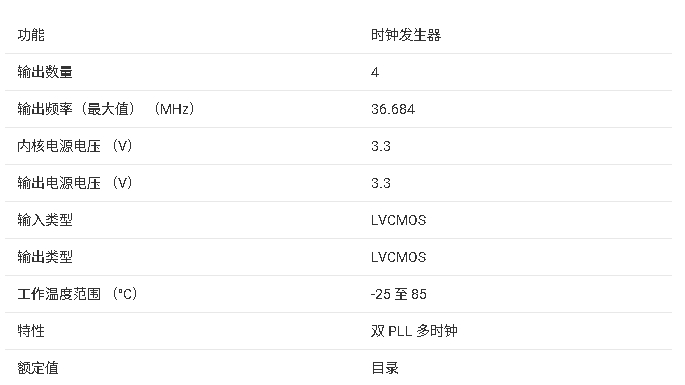

?PLL1707/PLL1708 雙PLL多時鐘發生器技術文檔總結

PLL1707成本低、鎖相 環路 (PLL) 多時鐘發生器。PLL1707和 PLL1708可以從 27 MHz 生成四個系統時鐘 參考輸入頻率

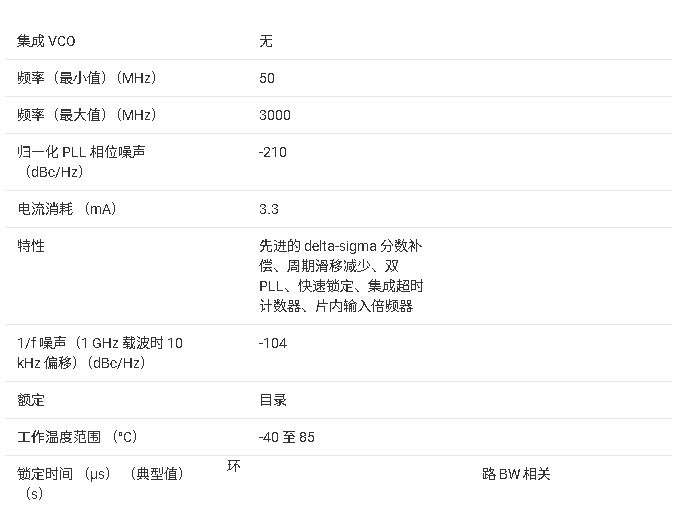

LMX2485E 用于射頻個人通信的 50 MHz 至 3 GHz Δ-Σ 低功耗雙通道 PLL技術手冊

架構,在較低失調頻率下推動分數雜散 到環路帶寬之外的更高頻率。能夠接近雜散噪聲和相位噪聲 能量

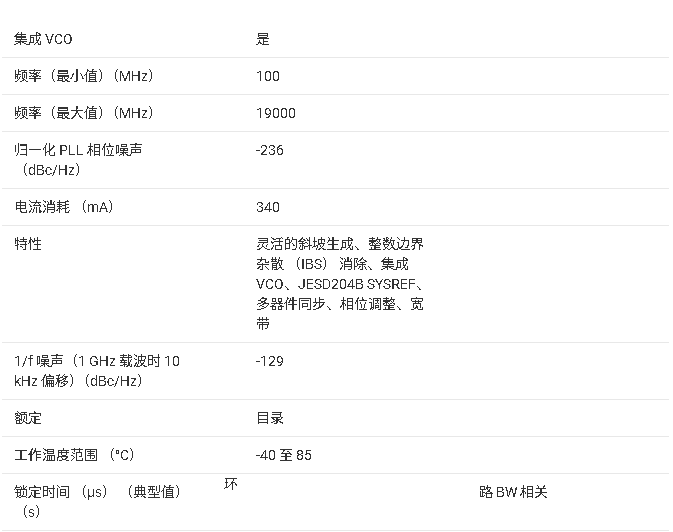

?LMX2595 20-GHz寬帶PLLATINUM?射頻合成器技術文檔總結

LMX2595高性能寬帶合成器,可生成 10 MHz 至 20 GHz 的任何頻率。集成倍頻器用于 15 GHz 以上的頻率。具有–236 dBc/Hz品質因數和高相位檢測器頻率的高性

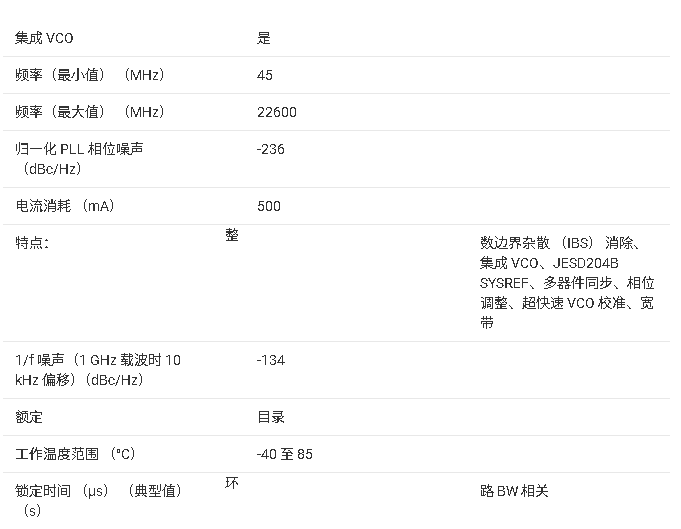

?LMX2820 22.6 GHz寬帶PLLatinum?射頻合成器技術文檔總結

和集成抖動。高速N分頻器沒有預分頻器,因此顯著降低了雜散的幅度和數量。還有一個可編程輸入乘法器,用于減輕整數邊界雜散。

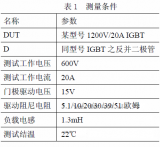

IGBT功率模塊動態測試中夾具雜散電感的影響

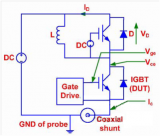

在IGBT功率模塊的動態測試中,夾具的雜散電感(Stray Inductance,Lσ)是影響測試結果準確性的核心因素。雜散電感由測試夾具的layout、材料及連接方式引入,會導致開關

無雜散、50 MHz 至 2.1 GHz 單通道小數 N 分頻頻率合成器 skyworksinc

電子發燒友網為你提供()無雜散、50 MHz 至 2.1 GHz 單通道小數 N 分頻頻率合成器相關產品參數、數據手冊,更有無雜散、50 M

發表于 05-23 18:30

ADC采樣率與信號頻率:關鍵概念與設計要點

在模數轉換器(ADC)的設計與應用中,采樣率與信號頻率的關系是影響系統性能的核心因素。采樣率是指ADC對模擬輸入進行采樣的速度,通常由外部時鐘或內部鎖相環(PLL)提供。現代高速ADC常采用

發表于 05-13 09:53

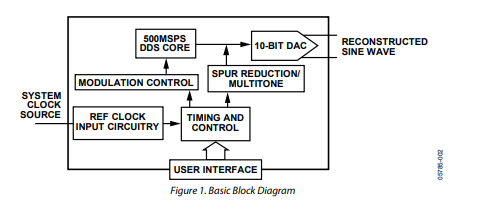

AD9911 500 MSPS直接數字頻率合成器,內置10位DAC技術手冊

AD9911是一款完整的直接數字頻率合成器(DDS)。該器件內置具有出色寬帶和窄帶無雜散動態范圍(SFDR)以及三個輔助DDS內核的高速DAC,而未分配數模轉換器(DAC)。這些輔助通道用于

雜散電感對IGBT開關過程的影響(2)

為驗證對主回路雜散電感效應的分析并考察不同電感量以及門極驅動情況下的實際情況,我們人為對Lp 大小進行了干預,其具體方法是在D 的陰極與電路PCB 之間(即Lp2 與Lc1之間)加入長度可調的導線,用試湊辦法得到期望的附加電感量。

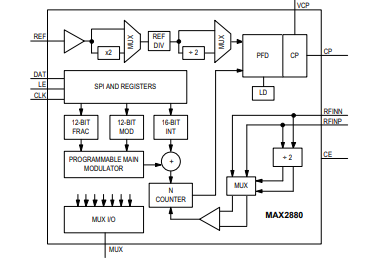

MAX2880 250MHz-12.4GHz、高性能、分數/整數型N分頻PLL技術手冊

MAX2880為高性能鎖相環(PLL),提供整數或分數N分頻工作模式。器件配合外部參考時鐘振蕩器、環路濾波器和VCO,可以構成超低噪聲、低雜散頻率合成器,可接受高達12.4GHz的RF

ADF41513 26.5GHz整數N/小數N PLL頻率合成器技術手冊

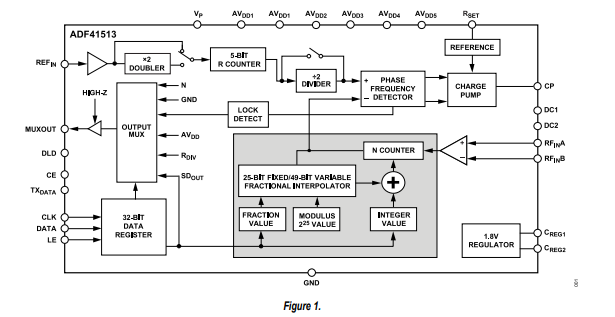

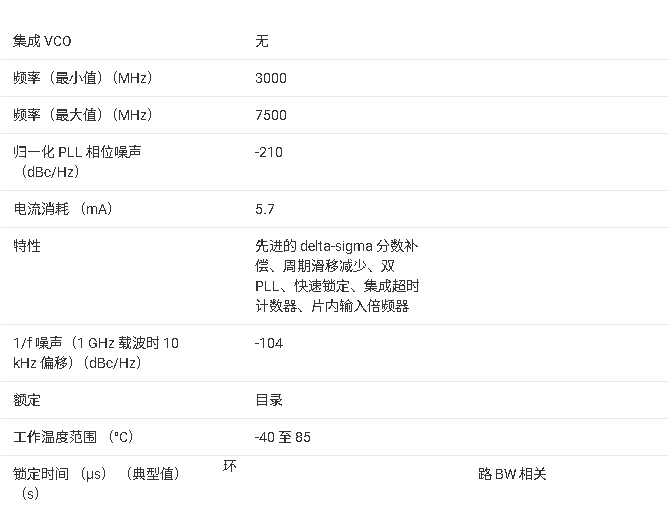

MHz(小數 N 模式),可實現更高的相位噪聲和雜散性能。使用 49 位分值時,可變模數 Δ-Σ 調制器可以實現極精細的分辨率。ADF41513 可用作整數 N 鎖相環 (PLL) 或小數 N

雜散電感對IGBT開關過程的影響(1)

的結構如主回路雜散電感會影響IGBT的開關特性,進而影響開關損耗,任何對其開關性能的研究都必然建立在實驗測試基礎之上,并在實際設計中盡量優化以降低變流回路雜散電感。

用于雜散信號消除的PLL頻率規劃

用于雜散信號消除的PLL頻率規劃

評論