概述

DS4520是9位非易失(NV) I/O擴展器,具有通過I2C兼容的串行接口控制的64字節NV用戶存貯器。與用來控制數字邏輯節點的硬件跳線和機械開關相比,DS4520為用戶提供了數字可編程的替代方案。并且,每一個引腳的數字狀態可以通過串行接口讀取。每一個I/O引腳都是獨立配置的。輸出是開漏極輸出,并具有可選的上拉。每一個輸出都能吸收12mA的電流。因為設備是NV的,它可以一上電就處于期望的狀態,從而能夠在上電之后立即控制數字邏輯輸入,而不用等待主機CPU來初始化控制。

數據表:*附件:DS4520 9位、I2C、非易失、輸入 輸出擴展器與存儲器技術手冊.pdf

應用

特性

- 機械跳線和開關的可編程替代品

- 九個NV輸入/輸出引腳

- 64字節NV用戶存儲器(EEPROM)

- 兼容I2C的串行接口

- 最多8個器件可以在同一I2C總線上工作

- 具有可配置上拉的開漏極輸出

- 輸出能吸收12mA電流

- 低功耗

- 寬工作電壓范圍(2.7V至5.5V)

- 工作溫度范圍:-40°C至+85°C

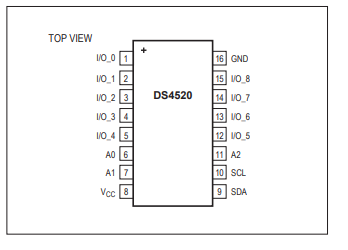

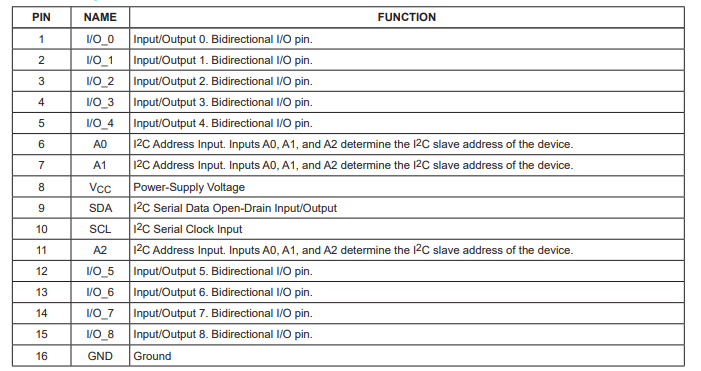

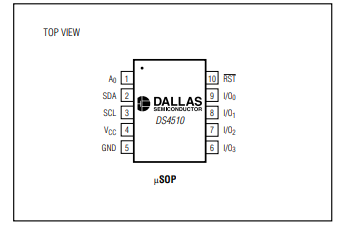

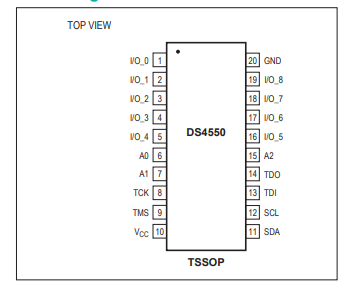

引腳配置描述

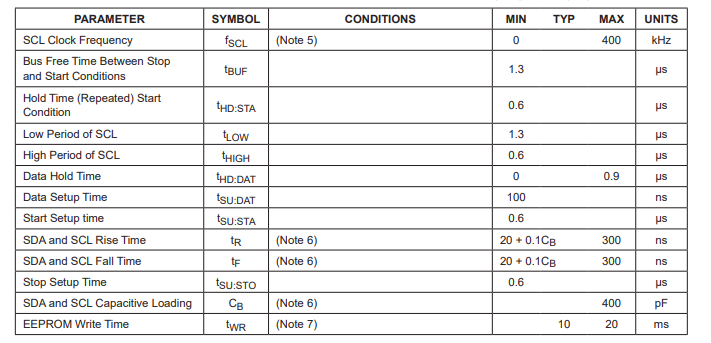

交流電氣特性

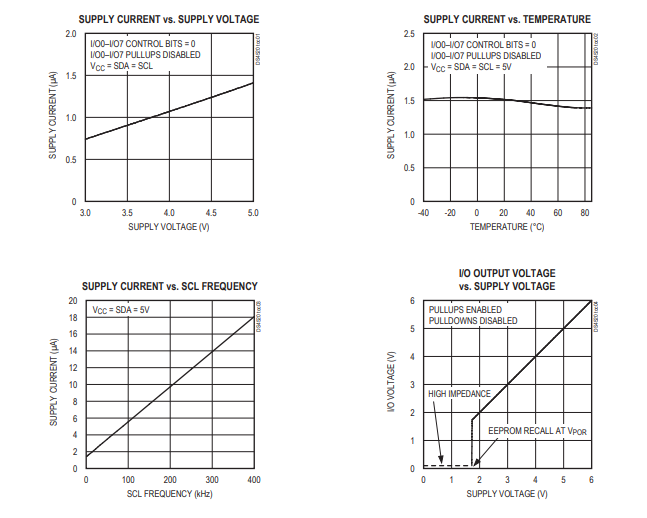

典型操作特性

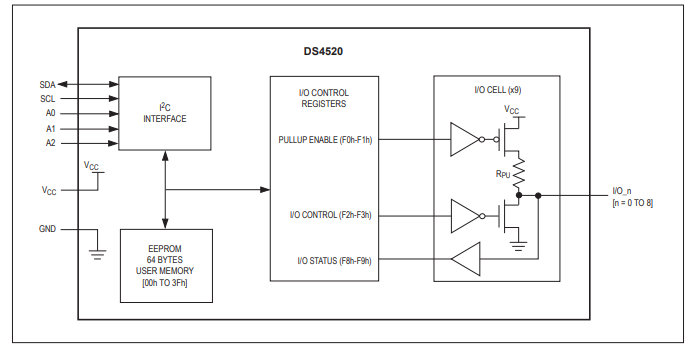

框圖

詳細說明

DS4520 包含九個雙向、非易失性(NV)輸入/輸出(I/O)引腳,以及一個 64 字節的 EEPROM 用戶存儲器。I/O 引腳和用戶存儲器可通過 I2C 兼容串行總線進行訪問。

可編程非易失性 I/O 引腳

每個可編程 I/O 引腳由一個輸入和一個集電極開路輸出組成,帶有一個可選擇的內部上拉電阻。要為每個 I/O 引腳啟用上拉功能,請寫入上拉使能寄存器(F0h 和 F1h)。要將輸出拉低,或將下拉晶體管置于高阻抗狀態,請寫入 I/O 控制寄存器(F2h 和 F3h)。要讀取 I/O 引腳上的電壓電平,請讀取 I/O 狀態寄存器(F8h 和 F9h)。要確定輸出的狀態,請讀取 I/O 控制寄存器和上拉電阻寄存器。I/O 控制寄存器和上拉使能寄存器均為 SRAM 映射的 EEPROM 寄存器。可以使用配置寄存器中的 SEE 位禁用寄存器的 EEPROM 寫入操作。這樣做可以減少寫入寄存器所需的時間,并且增加在 EEPROM 磨損之前可對 I/O 引腳進行調整的次數。

內存映射與內存類型

DS4520 的內存映射見表 1。DS4520 中有三種不同類型的內存:EEPROM、SRAM 映射 EEPROM 和 SRAM。指定為 EEPROM 的內存位置是非易失性的。向這些位置寫入內容會在 EEPROM 寫入周期中產生兩次寫入操作,其時間特性如“AC 電氣特性”表中所示。指定為 SRAM 映射 EEPROM 的位置可通過配置寄存器(最低有效位為 F4h)中的 SEE 位配置為在兩種模式下運行。當 SEE 位為 0(默認值)時,該內存位置的行為類似于 EEPROM。然而,當 SEE 位為 1 時,會寫入影子 SRAM 而非 EEPROM。這消除了 EEPROM 寫入時間(tWR)的問題,同時也消除了 EEPROM 磨損的問題。這對于需要頻繁更新 I/O 引腳的應用來說是理想的選擇。上電默認狀態下,I/O 引腳配置寫入 EEPROM(SEE = 0),上電后,可將 SEE 位寫為 1,這樣 I/O 引腳就能定期更新到影子 SRAM。DS4520 中存在的最后一種內存類型是標準 SRAM。

從機地址和地址引腳

DS4520 的從機地址由圖 1 中所示的 A0、A1 和 A2 地址引腳的狀態決定。連接到 VCC 的地址引腳會在從機地址的相應位位置產生“1”。反之,連接到 GND 的地址引腳會在從機地址的相應位位置產生“0”。I2C 通信中的從機地址將在后面的 I2C 串行接口描述部分進行說明。

I2C 串行接口描述

I2C 定義

以下術語常用于描述 I2C 主設備:

- 主設備:主設備控制總線上的從設備。主設備生成 SCL 時鐘脈沖,啟動和停止通信。

- 從設備:從設備在主設備的請求下發送和接收數據。

- 總線空閑或非忙狀態:停止條件和開始條件之間的時間,此時 SDA 和 SCL 均為高電平邏輯狀態。當總線空閑時,它通常會為從設備啟動低功耗模式。

- 開始條件:開始條件由主設備生成,用于啟動與從設備的數據傳輸。主設備在保持 SCL 高電平的同時將 SDA 從高電平轉換為低電平,以生成開始條件。有關適用的定時,請參見定時圖。

- 停止條件:停止條件由主設備生成,用于結束與從設備的數據傳輸。主設備在保持 SCL 高電平的同時將 SDA 從低電平轉換為高電平,以生成停止條件。有關適用的定時,請參見定時圖。

- 重復開始條件:主設備可在一次數據傳輸結束時使用重復開始條件,以表明它會立即啟動新的數據傳輸。重復開始條件通常在讀取操作期間用于標識特定內存地址,以啟動數據傳輸。正常的重復開始條件在總線空閑時發出。有關適用的定時,請參見定時圖。

- 位寫入:在 SCL 為低電平狀態期間,SDA 上的數據必須保持不變。在 SCL 的上升沿期間,數據進入高電平脈沖加上建立和保持時間要求(見圖 2)。在 SCL 的下降沿,設備會在 SCL 為低電平時讀取數據。

-

存儲器

+關注

關注

39文章

7746瀏覽量

172006 -

擴展器

+關注

關注

0文章

169瀏覽量

16257

發布評論請先 登錄

SGM4593:低電壓16位I2C和SMBus低功耗I/O擴展器的深度解析

SGM4594:低電壓16位I2C和SMBus低功耗I/O擴展器的全面解析

探索DS1321:靈活的非易失性控制器與鋰電池監測器

MAX7310:2線接口8位I/O端口擴展器的詳細解析

深入解析PCF8574:I2C總線8位I/O擴展器的設計與應用

深入解析PCF8575:16位I2C與SMBus I/O擴展器的卓越之選

TCA6408A:低電壓8位I2C和SMBus I/O擴展器的深度解析

TCA9555:低電壓16位I2C和SMBus I/O擴展器的全面解析

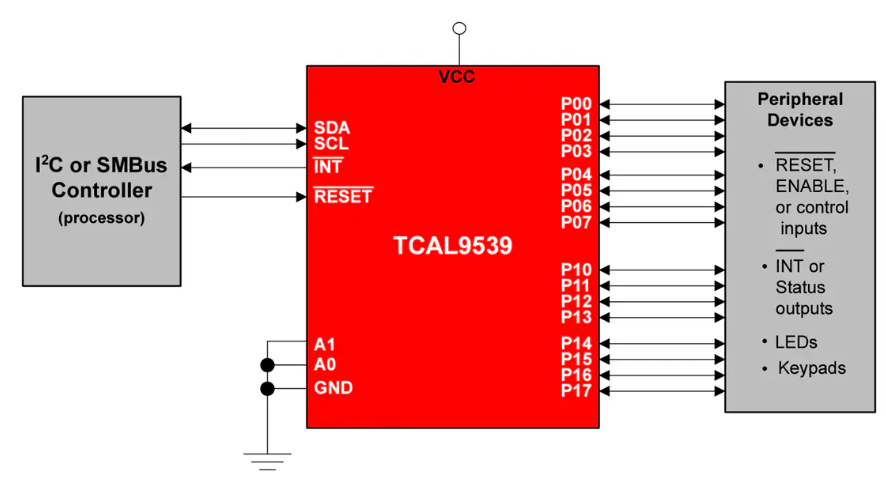

深入解析 TCA9539:低電壓 16 位 I2C 和 SMBus I/O 擴展器

TCA6424A:低電壓24位I2C和SMBus I/O擴展器的深度解析

深入解析TCA9554:8位I2C和SMBus低功耗I/O擴展器

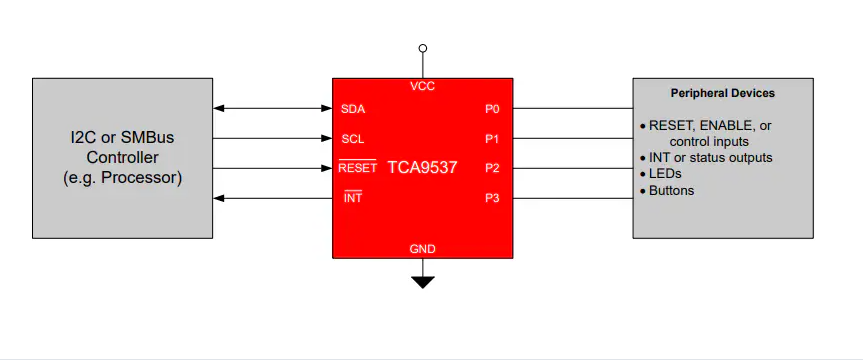

TCA9537遠程4位I2C/SMBus I/O擴展器技術解析與應用指南

DS4520 9位、I2C、非易失、輸入/輸出擴展器與存儲器技術手冊

DS4520 9位、I2C、非易失、輸入/輸出擴展器與存儲器技術手冊

評論