對(duì)相關(guān)NVMe IP視頻感興趣的,請(qǐng)到B站搜用戶名: 專注與守望

3)PCIe事務(wù)層

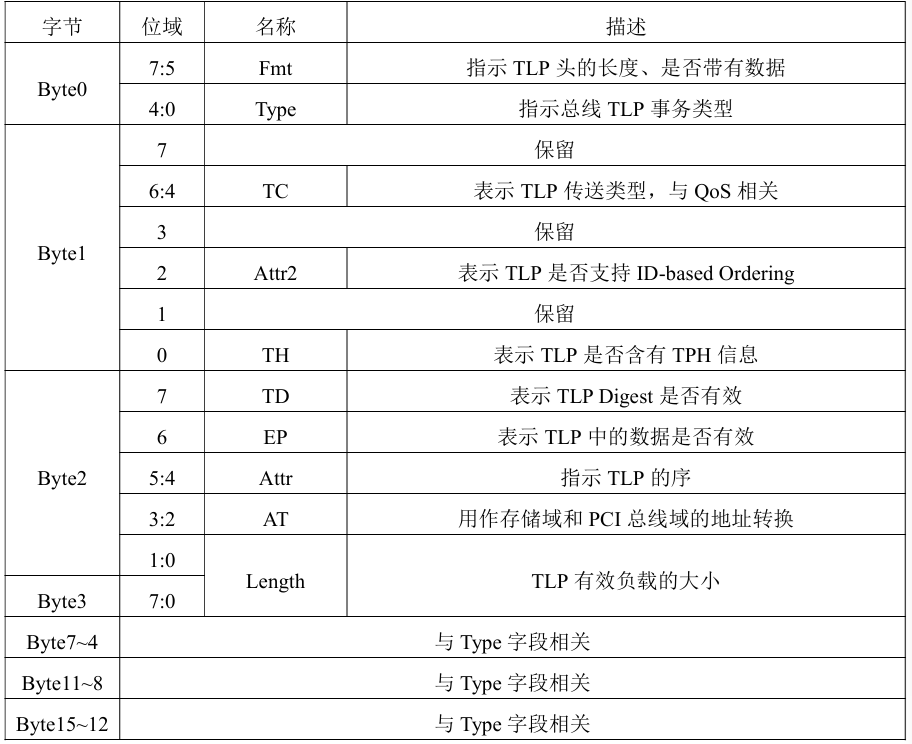

PCIe的事務(wù)層連接了PCIe設(shè)備核心與PCIe鏈路,這里主要基于PCIe事務(wù)層進(jìn)行討論與分析。事務(wù)層采用TLP傳輸事務(wù),完整的TLP由TLPPrefix、TLP頭、Payload和TLP Digest組成。TLP頭是TLP中最關(guān)鍵的部分,一般由三個(gè)或四個(gè)雙字的長(zhǎng)度,其格式定義如表1所示。

表1 PCIeTLP報(bào)文頭格式

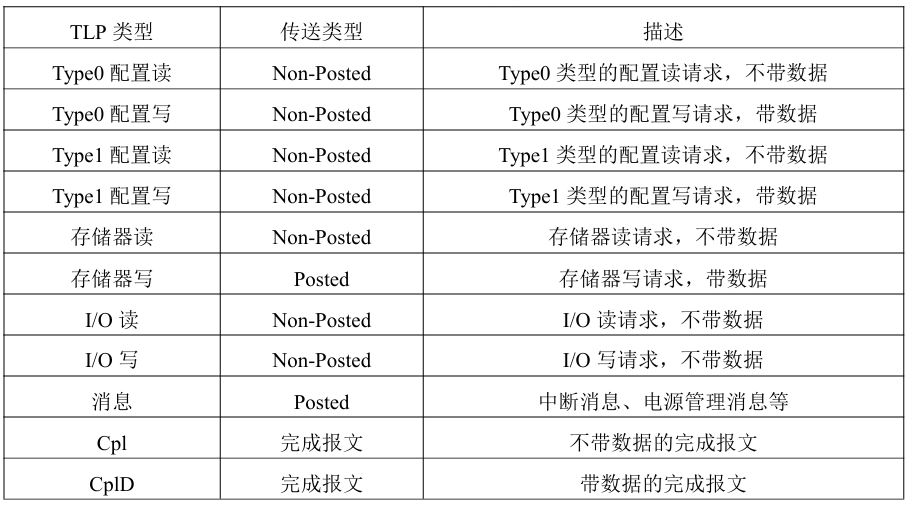

常用的PCIeTLP事務(wù)類型如表2所示。其中Non-Posted類型的事務(wù)請(qǐng)求需要 使用完成報(bào)文(CompletionPacket,Cpl)或帶數(shù)據(jù)的完成報(bào)文(CompletionPacketwith Data,CplD)類型的響應(yīng)包返回請(qǐng)求狀態(tài)或數(shù)據(jù),Posted類型的事務(wù)請(qǐng)求不需要使用 完成報(bào)文。 PCIe總線協(xié)議定義了基于地址的路由、基于ID的路由和隱式路由三種TLP路由 方式。其中,存儲(chǔ)器讀寫和I/O讀寫TLP采用基于地址的路由,該類型的報(bào)文可由 RC 或EP發(fā)出,根據(jù)TLP中的Address字段進(jìn)行路由選徑。配置讀寫報(bào)文、Cpl和 CplD 完成報(bào)文使用基于ID的路由,配置讀寫報(bào)文只能由RC發(fā)出,而完成報(bào)文可由 任何設(shè)備發(fā)出,這些報(bào)文根據(jù)TransactionID進(jìn)行路由選徑,TransactionID則由PCIe 總線號(hào)、設(shè)備號(hào)、功能號(hào)和Tag字段構(gòu)成。消息報(bào)文使用隱式路由,一般由RC發(fā)出 EP 響應(yīng),該類型報(bào)文的路由直接由下游端口到上游端口,或?yàn)镽C向EP發(fā)出的廣播。

表2 PCIeTLP事務(wù)類型

4)PCIe 配置空間

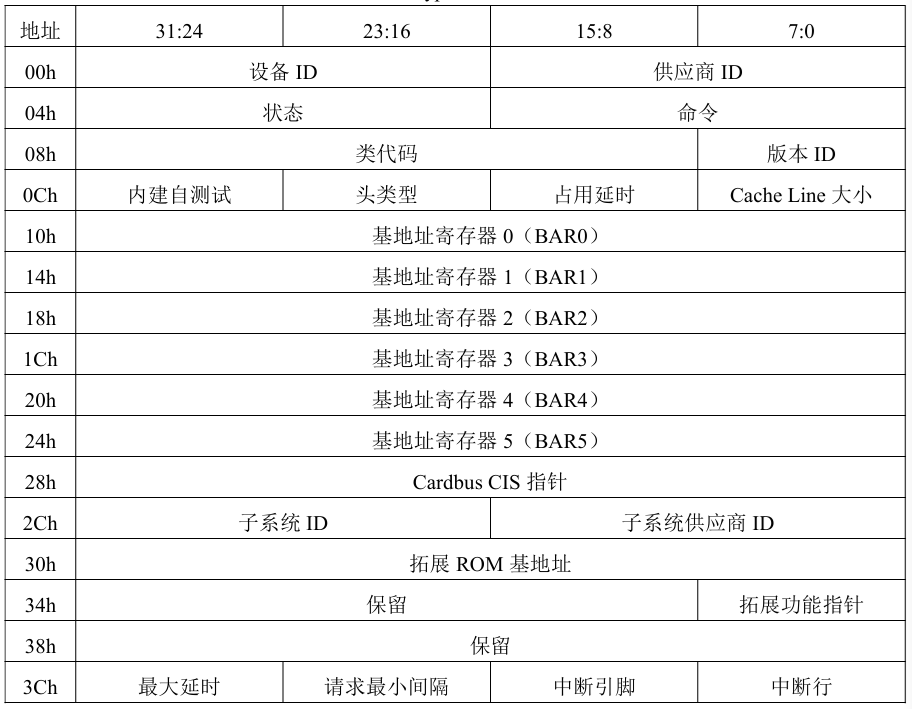

PCIe 設(shè)備具有和PCI設(shè)備相同的配置空間頭類型,此外使用PCIe拓展配置空間 管理PCIe總線。PCI配置空間頭分為Type0和Type1兩種類型,Type0類型配置空間 頭在PCIe總線中用于EP,Type1類型配置空間頭用于Switch中的虛擬PCI橋。 Type0 類型的配置空間頭結(jié)構(gòu)如表3所示。其中主要的寄存器的作用如下:

(1)設(shè)備ID和供應(yīng)商ID:由PCI-SIG分配,當(dāng)供應(yīng)商ID為16’hFFFF時(shí)表示 無(wú)效的設(shè)備;

(2)狀態(tài)寄存器:保存PCIe設(shè)備的狀態(tài)信息;

(3)命令寄存器:初始值為0,需要合理配置該寄存器才能訪問(wèn)該設(shè)備的存儲(chǔ) 器或者I/O空間;

(4)頭類型:當(dāng)值為0時(shí)表示設(shè)備使用Type0的配置空間,值為1時(shí)表示設(shè)備 使用Type1的配置空間;

(5)基地址寄存器(BaseAddressRegister,BAR):保存PCIe 設(shè)備使用的地址空間的基地址;

(6)拓展功能指針:指向拓展配置空間的偏移地址。

表3 PCIeType0類型配置空間頭

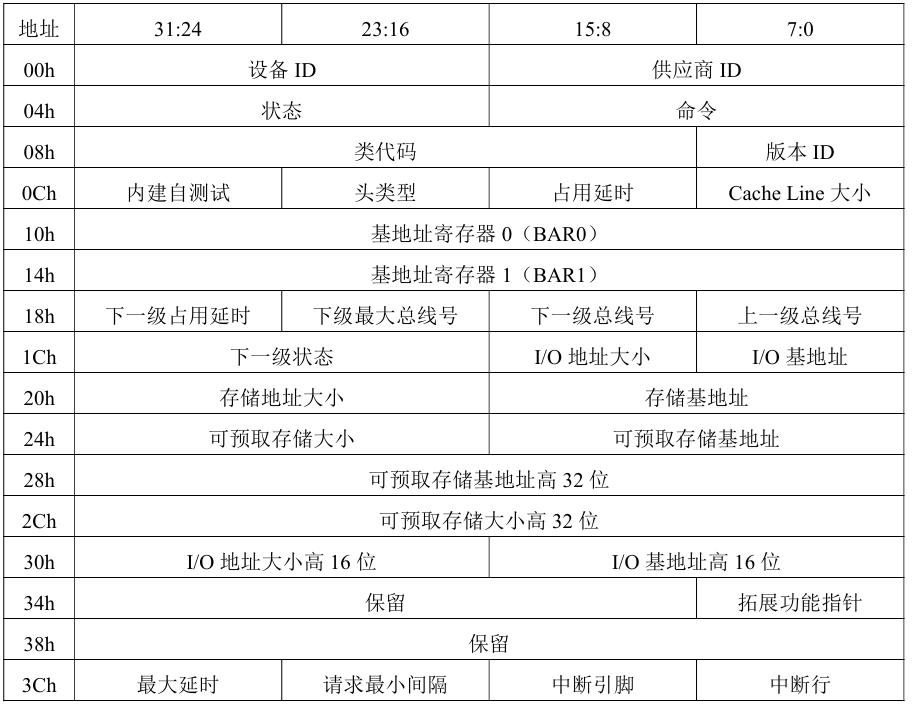

Type1類型的配置空間頭如表4所示。其中主要寄存器的作用如下:

(1)00h~14h的寄存器作用與Type0類型的相同;

(2)下級(jí)最大總線號(hào)、下一級(jí)總線號(hào)、上一級(jí)總線號(hào):下級(jí)最大總線號(hào)為該設(shè) 備下游的PCIe子樹(shù)中最大的總線號(hào),下一級(jí)總線號(hào)為直接連接在該設(shè)備下游端口的 總線號(hào),上一級(jí)總線號(hào)為與該設(shè)備上游端口直接連接的總線號(hào),三者共同確定了該設(shè) 備在PCIe樹(shù)中的位置;

(3)存儲(chǔ)地址大小、存儲(chǔ)基地址:兩者共同表示分配到該設(shè)備的存儲(chǔ)地址域;

(4)拓展功能指針:指向拓展配置空間的偏移地址。

表4 Type1類型的配置空間頭

審核編輯 黃宇

-

PCIe

+關(guān)注

關(guān)注

16文章

1461瀏覽量

88425 -

nvme

+關(guān)注

關(guān)注

0文章

299瀏覽量

23842

發(fā)布評(píng)論請(qǐng)先 登錄

高性能NVMe主機(jī)控制器,Xilinx FPGA PCIe 3

NVMe協(xié)議簡(jiǎn)介2

nvme IP開(kāi)發(fā)之PCIe上

nvme IP開(kāi)發(fā)之PCIe下

NVMe高速傳輸之擺脫XDMA設(shè)計(jì)之七:系統(tǒng)初始化

NVMe高速傳輸之擺脫XDMA設(shè)計(jì)之十:NVMe初始化狀態(tài)機(jī)設(shè)計(jì)

NVMe高速傳輸之擺脫XDMA設(shè)計(jì)18:UVM驗(yàn)證平臺(tái)

NVMe高速傳輸之擺脫XDMA設(shè)計(jì)之12:PCIe請(qǐng)求模塊設(shè)計(jì)(上)

NVMe高速傳輸之擺脫XDMA設(shè)計(jì)14: PCIe應(yīng)答模塊設(shè)計(jì)

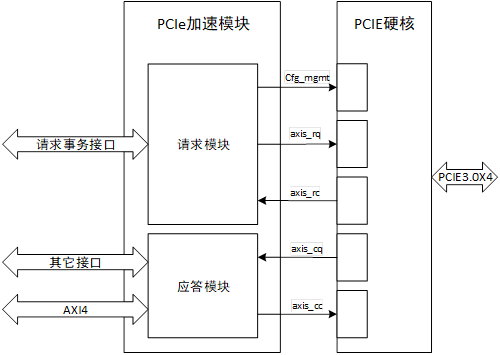

NVMe高速傳輸之擺脫XDMA設(shè)計(jì)17:PCIe加速模塊設(shè)計(jì)

NVMe高速傳輸之擺脫XDMA設(shè)計(jì)20: PCIe應(yīng)答模塊設(shè)計(jì)

Flashtec NVMe 3108 PCIe第四代NVMe固態(tài)硬盤控制器怎么樣?

NVMe高速傳輸之擺脫XDMA設(shè)計(jì)14: PCIe應(yīng)答模塊設(shè)計(jì)

NVMe高速傳輸之擺脫XDMA設(shè)計(jì)17:PCIe加速模塊設(shè)計(jì)

NVMe高速傳輸之擺脫XDMA設(shè)計(jì)20: PCIe應(yīng)答模塊設(shè)計(jì)

NVMe簡(jiǎn)介之PCIe下

NVMe簡(jiǎn)介之PCIe下

評(píng)論