隨著半導體產業快速發展,人工智能加速推動對高性能計算的需求,Cadence 將自己定位為仿真和設計自動化領域的行業先鋒。在于圣克拉拉會議中心舉行的 DesignCon 2025 大會上,Cadence 產品管理總監 Brad Griffin 分享了公司在信號完整性、電源完整性、熱仿真和電磁分析方面的最新進展,這些技術正是行業向異構集成和芯粒架構轉型的關鍵驅動力。

“這標志著 Cadence 在 DesignCon 大會上的一個新起點。”Griffin 表示。“我們已連續參會 20 余年,雖然印刷電路板仍然很重要,但行業格局已發生變化——過去分布在電路板上的器件,如今被集成至單一封裝中。”

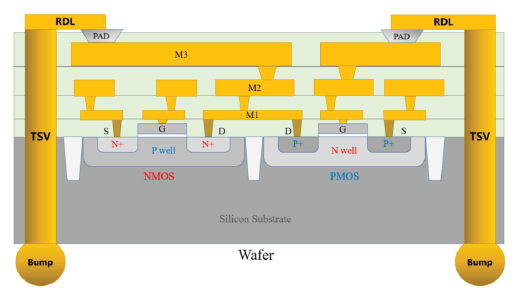

通用芯粒互聯技術 (UCIe) 標準和高帶寬存儲器 (HBM) 接口極大推動了這一轉變,大幅增加了設計復雜性、數據規模和仿真要求。隨著 AI 芯片在硅基板或有機基板上集成多個芯粒,傳統仿真流程已難以滿足新興架構的需求。

應對異構集成的復雜性

隨著系統架構從單裸片架構轉向多裸片架構,Cadence 專注于開發新工具,以應對裸片間通信數據的指數級增長。“先進封裝內的幾何尺寸遠遠小于印刷電路板上的幾何尺寸,這導致我們的設計數據庫規模呈爆炸式增長。”Griffin 解釋道。

其中一項關鍵挑戰是如何確保芯粒之間的無縫通信。目前,UCIe 標準已廣泛應用于裸片間互連,但隨之而來的信號完整性和電源完整性問題,需要依賴先進的仿真工作流程來解決。與此同時,HBM 接口通過堆疊內存裸片來實現高速性能,但會生成大量數據,這些數據必須在制造前通過仿真進行驗證。

“Cadence 已將仿真工具直接集成至我們的設計平臺,”Griffin 表示,“如果等到設計過程結束才進行仿真,可能為時已晚。通過在設計過程中進行實時、選擇性仿真,我們可以幫助工程師實現設計“左移”,通過設計同步分析,提前發現并解決問題,減少設計迭代次數,加快產品上市時間。”

仿真可擴展性:實現 AI 芯片設計

Cadence 的一項主要創新是具有高效的多核擴展能力,可大大縮短計算時間。這對于具有多個 HBM 接口(有時單一設計中有多達 12 個接口)的 AI 芯片尤為重要,因為 AI 芯片設計流程涉及龐大的仿真工作量。

“過去,工程師必須導出可能高達 500GB 的設計數據才能進行一次仿真,整個過程往往耗時數天。”Griffin 說道。“而如今,Cadence 的工具僅提取必要的數據,將仿真周期從幾天縮短至幾分鐘。”

在這一過程中,Cadence 的 Clarity 3D Solver 發揮了關鍵作用。傳統的全波 3D 電磁求解器僅用于解決特定的問題,但隨著設計日益緊湊和復雜,具備簽核級精度的電磁分析已成為必然趨勢。

“現如今,全波 3D 求解器被用作先進封裝設計的標準解決方案。”Griffin 表示。“Cadence 的 Clarity 求解器兼具準確性和可擴展性,能夠幫助公司滿足新一代 AI 硬件的需求。”

高性能系統中的熱挑戰

隨著 AI 工作負載推動功率密度不斷提升,熱管理已成為芯粒架構設計工程師關注的核心問題。如果沒有適當的冷卻方案,即使是最先進的半導體設計也可能面臨過熱和故障的風險。

“二十年前,熱分析并不是 Cadence 關注的重點,”Griffin 表示,“但如今已成為客戶首要關注的問題。”

為了應對這些挑戰,Cadence 推出了多物理場仿真平臺 Celsius Studio。該平臺集成了電熱協同仿真和計算流體力學 (CFD),能夠仿真芯片、封裝、電路板和系統級別的散熱。

“借助 Celsius,電氣工程師可以仿真瞬態熱行為,動態調整功耗以防止過熱。”Griffin 說道。“同時,機械工程師能夠在同一環境中完成氣流、液體冷卻和外殼設計仿真。”

修復損壞的設計流程:

從“弗蘭肯流程”到集成工作流程

大型先進封裝設計面臨的一個緊迫問題是 Griffin 所稱的“弗蘭肯流程”——依賴獨立且缺乏協調的工具進行仿真、分析和設計的碎片化方法。

“工程師不可能花費數周時間將數據從一種工具傳輸到另一種工具。”Griffin 說道。“Cadence 在設計環境中進行仿真,消除了這一低效環節,使工程師能夠在完成整個設計之前簽核關鍵子系統。”

Cadence前瞻性的“左移”方法將 PCB、IC 封裝和 3D-IC 設計工作流程與信號完整性、電源完整性、熱和電磁仿真相結合,確保工程師能夠在設計的早期階段發現并解決問題。

“我們正在見證設計思維的重大轉變。”Griffin 表示。“如今,越來越多的設計工程師直接運行仿真,而不再等待專門的信號完整性或電源完整性專家來處理。這不僅加快了開發周期,還降低了設計錯誤率。”

前景展望:仿真和 AI 驅動設計的未來

隨著行業深入推進 AI 驅動的芯片設計,Cadence 不斷拓展其電子設計自動化 (EDA) 解決方案。公司利用機器學習和基于云的仿真可擴展性,進一步簡化異構集成工作流程,使 AI、高性能計算和新一代半導體設計比以往更加高效。

Cadence 還專注于提高設計驗證的自動化水平,通過 AI 輔助仿真和驗證,減輕工程師的負擔。隨著半導體制造商競相開發突破能效和計算性能極限的芯片,這些進步將變得尤為重要。

“我們不僅緊跟行業發展的步伐,”Griffin 總結道,“更致力于塑造行業的未來。”

-

Cadence

+關注

關注

68文章

1011瀏覽量

146928 -

人工智能

+關注

關注

1817文章

50098瀏覽量

265380 -

封裝設計

+關注

關注

2文章

48瀏覽量

12168

發布評論請先 登錄

電力電子行業“死磕固變”的戰略意義及前瞻性

Qorvo UWB解決方案助力Algorized實現先進感知技術

2025 Cadence 中國技術巡回研討會即將開啟 ——系統設計與分析專場研討會(上海站)

《AI芯片:科技探索與AGI愿景》—— 勾勒計算未來的戰略羅盤

Cadence SPB OrCAD Allegro24.1安裝包

MUN12AD03-SEC的封裝設計對散熱有何影響?

Chiplet與先進封裝設計中EDA工具面臨的挑戰

整流橋關鍵參數與封裝設計的關聯都有哪些?

在樹莓派上設置 DeepSeek R1:2025 年離線人工智能的未來

DesignCon 采訪 | Cadence 的前瞻性方法和先進封裝設計的未來

DesignCon 采訪 | Cadence 的前瞻性方法和先進封裝設計的未來

評論