在高帶寬、高頻率、高同步精度的電子系統(tǒng)中,傳統(tǒng)單端晶體振蕩器已難以滿足系統(tǒng)對(duì)信號(hào)完整性與誤碼率控制的嚴(yán)苛要求。差分振蕩器憑借其抗干擾能力強(qiáng)、信號(hào)穩(wěn)定性高、驅(qū)動(dòng)能力優(yōu)異的特性,逐步取代傳統(tǒng)晶振,成為數(shù)據(jù)中心、通信基站、高速接口控制平臺(tái)的主力時(shí)鐘源。特別是具備0.15ps超低相位抖動(dòng)性能的差分輸出晶振,其在SerDes、ADC、光通信等系統(tǒng)中發(fā)揮著至關(guān)重要的作用。

什么是差分振蕩器?

差分振蕩器是一類采用雙信號(hào)輸出(正負(fù)對(duì)稱)的高性能晶體時(shí)鐘器件,常見輸出接口包括LVDS、LVPECL與HCSL。與單端CMOS輸出不同,差分信號(hào)在布線中可以相互抵消干擾,提高時(shí)鐘線上的抗EMI能力,同時(shí)大幅減少抖動(dòng)對(duì)系統(tǒng)造成的誤差放大。其輸出上升沿陡峭、信號(hào)擺幅穩(wěn)定、對(duì)稱性強(qiáng),可直接驅(qū)動(dòng)高速SerDes鏈路、FPGA時(shí)鐘樹或多路同步ADC等應(yīng)用。作為現(xiàn)代高速通信與數(shù)據(jù)處理平臺(tái)的重要組成部分,差分晶振廣泛用于數(shù)據(jù)中心交換設(shè)備、5G通信模塊、高速網(wǎng)絡(luò)存儲(chǔ)、工業(yè)級(jí)數(shù)據(jù)采集等領(lǐng)域。

0.15ps RMS抖動(dòng)意味著什么?

0.15ps RMS相位抖動(dòng)代表著極為純凈的時(shí)鐘信號(hào)輸出,是衡量時(shí)鐘源質(zhì)量的核心指標(biāo)之一。對(duì)于PCIe Gen4/Gen5、40G/100G光模塊、SerDes鏈路或高速DAC輸入等應(yīng)用而言,時(shí)鐘抖動(dòng)越低,系統(tǒng)誤碼率越小,數(shù)據(jù)恢復(fù)與同步越穩(wěn)定。通過精準(zhǔn)控制晶片振蕩頻率、驅(qū)動(dòng)級(jí)電路優(yōu)化與內(nèi)部抑噪技術(shù),部分差分振蕩器可將抖動(dòng)壓縮至0.1ps以下,支撐多通道、高帶寬的數(shù)據(jù)系統(tǒng)運(yùn)行。相比普通晶振的3~5ps抖動(dòng)水平,0.15ps級(jí)差分振蕩器具備更高的通信完整性與更寬的帶寬容忍度。

常見差分輸出類型及應(yīng)用匹配

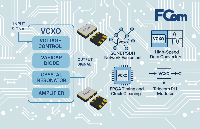

差分振蕩器常采用三類主流接口輸出:LVPECL、LVDS與HCSL。LVPECL具有高驅(qū)動(dòng)能力,適用于超高速接口如10G SFP+、25G/40G SerDes鏈路;LVDS功耗低、線性好,常用于FPGA/SoC時(shí)鐘輸入、視頻同步信號(hào)等;HCSL則廣泛應(yīng)用于PCIe時(shí)鐘網(wǎng)絡(luò),兼容主板與服務(wù)器時(shí)鐘架構(gòu)。根據(jù)不同系統(tǒng)平臺(tái)與終端芯片接口標(biāo)準(zhǔn)選擇合適輸出方式,不僅能提升傳輸效率,也能降低布線復(fù)雜度與干擾容忍風(fēng)險(xiǎn)。

典型應(yīng)用場(chǎng)景與芯片/頻率推薦

1)數(shù)據(jù)中心高速互連:支持頻點(diǎn) 100~156.25MHz,推薦搭配芯片:Intel Stratix 10、Broadcom BCM82391;

2)光通信模塊:支持頻點(diǎn) 19.44MHz、125MHz、155.52MHz,推薦芯片:MACOM MAOM-002313、Semtech GN2117;

3)PCIe系統(tǒng):支持頻點(diǎn) 25MHz、100MHz,搭配Intel Xeon、AMD EPYC平臺(tái)用于服務(wù)器主板、交換芯片;

4)同步ADC/DAC:推薦頻點(diǎn) 40MHz~100MHz,適配芯片:Analog Devices AD9689、Texas Instruments DAC38RFxx系列。

趨勢(shì)展望:更低抖動(dòng)、更小封裝、更智能接口

未來的差分振蕩器將進(jìn)一步在三個(gè)方向持續(xù)優(yōu)化:一是抖動(dòng)性能將邁入0.1ps甚至0.05ps RMS級(jí)別,服務(wù)于112G PAM4、CXL等高速互連技術(shù);二是尺寸將向更小封裝(如2520、3225)過渡,便于部署在高密度PCB與多模平臺(tái)中;三是智能接口功能將加入I2C調(diào)頻、故障檢測(cè)、遠(yuǎn)程控制等能力,使振蕩器不僅是時(shí)鐘源,更是系統(tǒng)運(yùn)行的時(shí)序“感知中心”。這將極大推動(dòng)差分晶振在AI服務(wù)器、邊緣計(jì)算、光電混合模塊等前沿系統(tǒng)中的普及與進(jìn)化。

總結(jié)

差分振蕩器正成為高速通信與高精度同步系統(tǒng)中不可或缺的核心部件,尤其是在對(duì)信號(hào)完整性與抖動(dòng)控制提出極高要求的應(yīng)用中,其0.15ps級(jí)超低抖動(dòng)性能為系統(tǒng)提供了堅(jiān)實(shí)的時(shí)鐘保障。隨著SoC頻率提升與數(shù)據(jù)鏈路高速化趨勢(shì)加劇,這類振蕩器將在數(shù)據(jù)中心、工業(yè)平臺(tái)、通信骨干與智能終端中持續(xù)拓展其應(yīng)用邊界,成為未來時(shí)鐘解決方案演進(jìn)中的關(guān)鍵節(jié)點(diǎn)。

-

振蕩器

+關(guān)注

關(guān)注

28文章

4186瀏覽量

143058 -

低抖動(dòng)

+關(guān)注

關(guān)注

0文章

74瀏覽量

6117 -

差分晶振

+關(guān)注

關(guān)注

0文章

185瀏覽量

2082

發(fā)布評(píng)論請(qǐng)先 登錄

差分TCXO:新一代高精度、低抖動(dòng)時(shí)鐘振蕩器解析

從SFP到OSFP:FCom差分晶振覆蓋全類型光模塊的時(shí)鐘設(shè)計(jì)方案

差分輸出VCXO振蕩器 | FCom富士晶振 - 低抖動(dòng)時(shí)鐘解決方案

中型數(shù)據(jù)中心中的差分晶體振蕩器應(yīng)用與匹配方案

中型數(shù)據(jù)中心應(yīng)用平臺(tái)與差分晶體振蕩器參數(shù)對(duì)照中型數(shù)據(jù)中心應(yīng)用平臺(tái)與差分晶體振蕩器參數(shù)對(duì)照

差分輸出 × 超低抖動(dòng):打造高速穩(wěn)定的大型數(shù)據(jù)同步時(shí)脈

差分振蕩器,用0.15ps超低抖動(dòng),保障高速數(shù)據(jù)傳輸?shù)拿恳晃痪珳?zhǔn)! #電路知識(shí) #差分晶振 #差分信號(hào)

LTC6951:集成壓控振蕩器數(shù)據(jù)表的超低抖動(dòng)多輸出時(shí)鐘合成器

MEMS差分振蕩器與傳統(tǒng)差分振蕩器的比較

MG7050VAN 基于聲表的差分多輸出 晶體振蕩器(LVDS)

MG7050HAN 基于聲表的差分多輸出 晶體振蕩器(HCSL)

FCom富士差分振蕩器-高性能交換機(jī)中的應(yīng)用及性能要求

低抖動(dòng)VCXO振蕩器:SONET時(shí)鐘與高速通信的核心時(shí)序方案

差分振蕩器:支持0.15ps超低抖動(dòng)的高速時(shí)鐘核心

差分振蕩器:支持0.15ps超低抖動(dòng)的高速時(shí)鐘核心

評(píng)論