高速先生成員--黃剛

作為三大分立元器件之一的電容,的確身上掛滿了title,之前的高速先生文章中也部分描述過它的用途,例如用作電源網(wǎng)絡(luò)的去耦電容和用作高速串行鏈路中的隔直電容。今兒我們再普及它的另外一個作用---縫合!

本著高速先生的一貫風(fēng)格,主打一個不講道理,額,不是!是不講太多深奧的理論,希望以直觀形象的仿真結(jié)果來說明問題。所以一上來我們就直奔仿真建模,通過仿真讓大家輕松“get”到要點。

案例1:

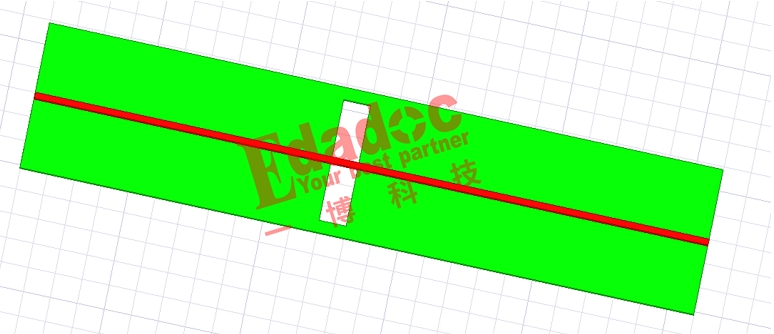

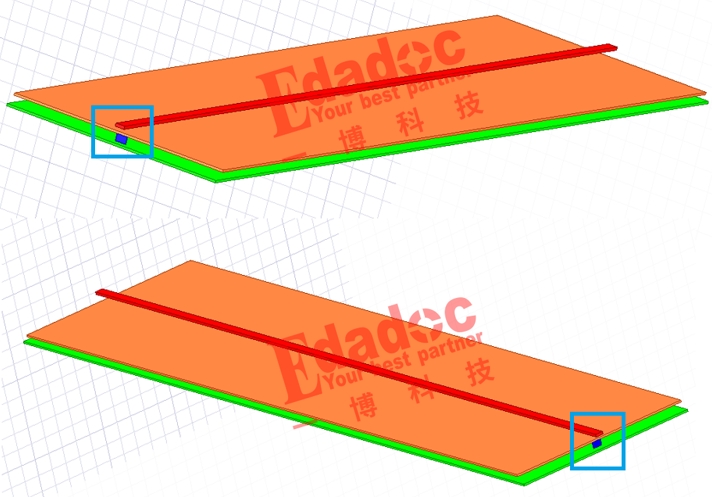

相信很多人都遇到走線跨分割地平面的情況,例如下面的模型所展示的:

大家都知道跨分割肯定對信號有影響了,那你們能想到的優(yōu)化方案是什么呢!什么,告訴我不跨分割平面不就解決了嗎!要是能不跨分割平面,鬼都知道肯定是最好的解決方案啦!那如果在避免不了跨分割的情況下呢?相信部分資深的硬件工程師或者設(shè)計工程師就會條件反射的想到這樣去做,那就是在地平面跨分割的位置整上1到2個電容。

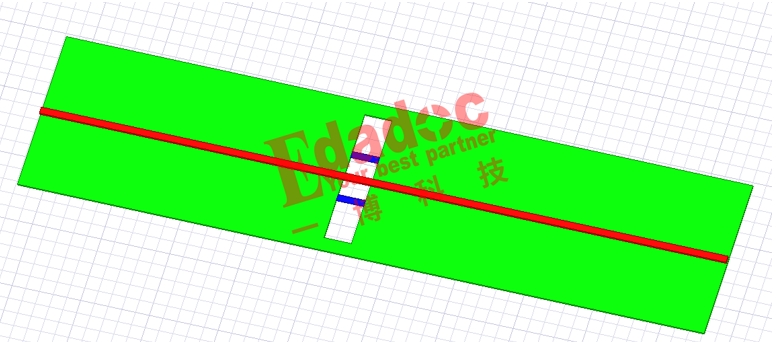

具體怎么放?就像下面藍色器件這樣放。

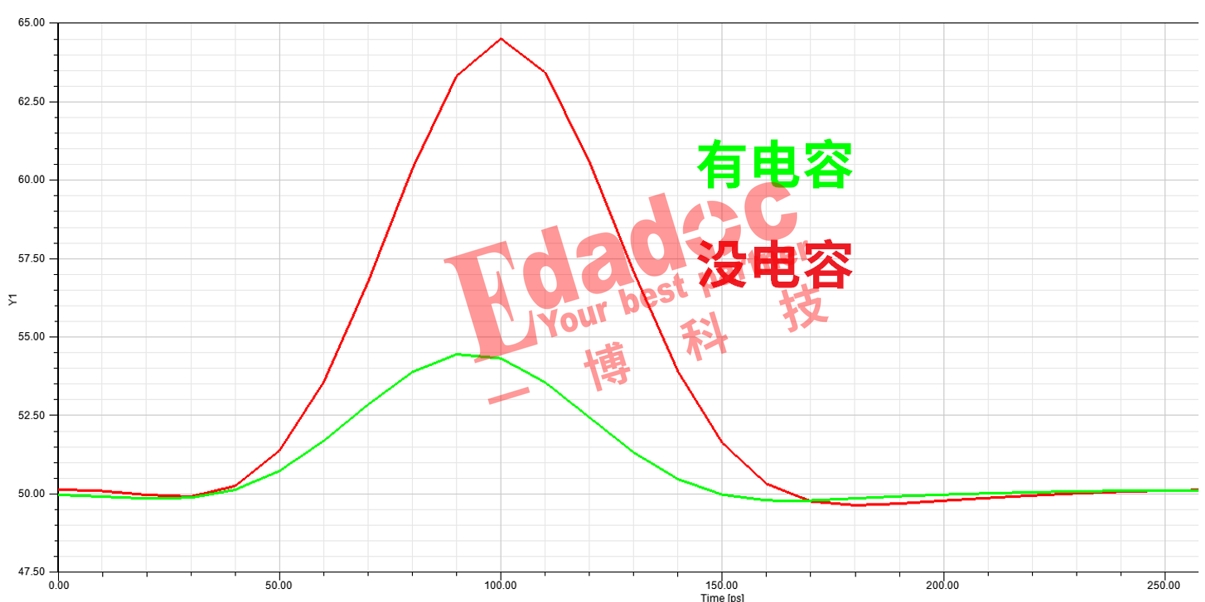

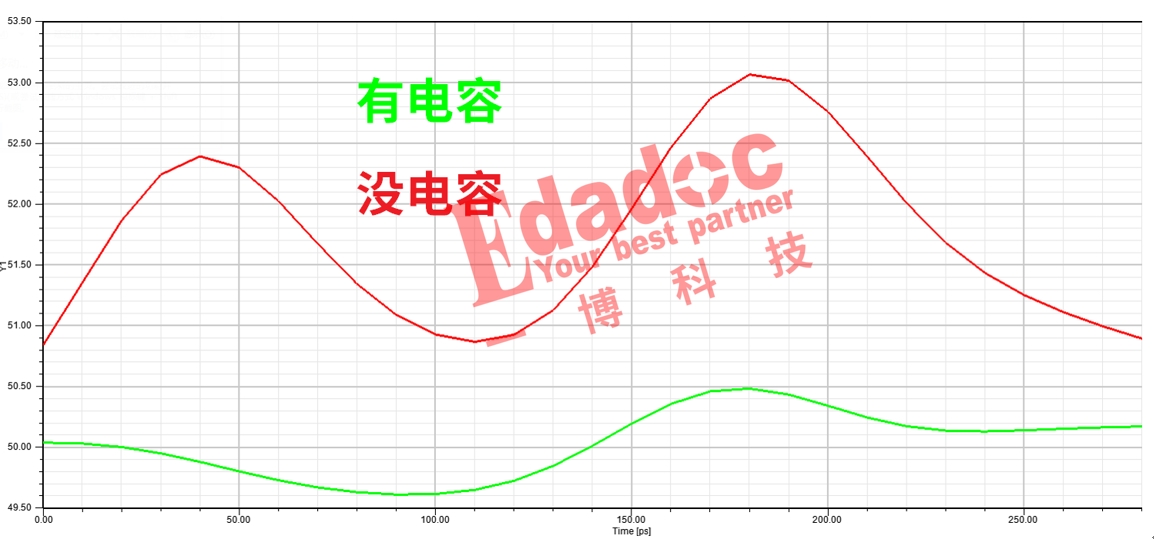

從仿真結(jié)果上看,放和不放電容的插損對比是這樣的。

而在跨分割位置的TDR阻抗結(jié)果對比是這樣的:

案例2:

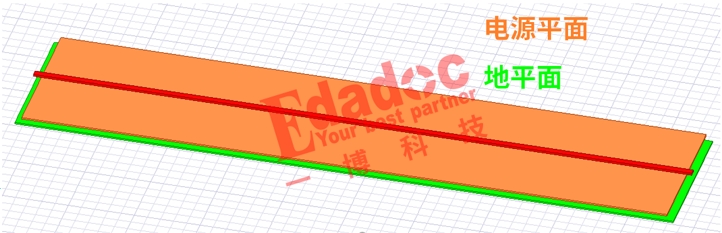

線還是那根信號線,我們換個場景,讓這根信號線只能參考電源平面,沒法直接參考地平面,如下所示:紅色信號線參考的是下面層的橙色電源平面,電源平面再下一層才是本來需要參考的地平面。

當(dāng)然,高速先生從來也沒說過信號線就不能參考電源平面了。你如果硬要直接按上面的模型去做設(shè)計的話,也不是說一定會掛!這時候,還是案例1那幫資深工程師又有解決方案了,那就是下面的樣子!

在走線首尾兩端的電源平面和地平面之間各加一個電容,如下面藍色東東所示。

還別說,資深就是資深,加了電容后,信號質(zhì)量就是比你直接不加電容硬做的來得好。

插損對比結(jié)果如下:

TDR阻抗結(jié)果對比如下:

案例3?由于篇幅已經(jīng)很長了,就當(dāng)沒有了吧!當(dāng)然本身縫合電容能用到的設(shè)計場景肯定是有很多的,在一些非常規(guī)的設(shè)計中,用上它之后的改善度可以非常的大。快到假期了,相信大家也不太想看那么多字了哈,留下后面的一個思考問題,就這樣了哈!

問題:那大家能說說縫合電容縫的到底是啥呢?或者大家的設(shè)計有類似的用法也可以詳細(xì)描述下?

關(guān)于一博科技:

一博科技成立于2003年3月,深圳創(chuàng)業(yè)板上市公司,股票代碼: 301366,專注于高速PCB設(shè)計、SI/PI仿真分析等技術(shù)服務(wù),并為研發(fā)樣機及批量生產(chǎn)提供高品質(zhì)、短交期的PCB制板與PCBA生產(chǎn)服務(wù)。致力于打造一流的硬件創(chuàng)新平臺,加快電子產(chǎn)品的硬件創(chuàng)新進程,提升產(chǎn)品質(zhì)量。

審核編輯 黃宇

-

仿真

+關(guān)注

關(guān)注

55文章

4526瀏覽量

138592 -

PCB

+關(guān)注

關(guān)注

1文章

2337瀏覽量

13204

發(fā)布評論請先 登錄

小小跳線大講究:PCB設(shè)計跳線用法全攻略

組合導(dǎo)航不知道怎么選,看這里

PCB設(shè)計 | AI如何顛覆PCB設(shè)計?從手動布線到智能自動化的30年演進

深度解讀PCB設(shè)計布局準(zhǔn)則

PCB仿真結(jié)果天下無敵,板廠加工讓你一敗涂地

編譯錯誤: error: unrecognizable insn,不知道原因,請教!

開關(guān)電源的PCB設(shè)計

PCB設(shè)計如何用電源去耦電容改善高速信號質(zhì)量

原理圖和PCB設(shè)計中的常見錯誤

高速PCB設(shè)計中揭秘DC-BIAS效應(yīng):電容“縮水”對電源噪聲的影響

PCB設(shè)計仿真,“縫合電容”我怎么可能不知道

球壓試驗裝置:你可能不知道的電氣安全衛(wèi)士

PCB設(shè)計仿真,“縫合電容”我怎么可能不知道

PCB設(shè)計仿真,“縫合電容”我怎么可能不知道

評論