概述

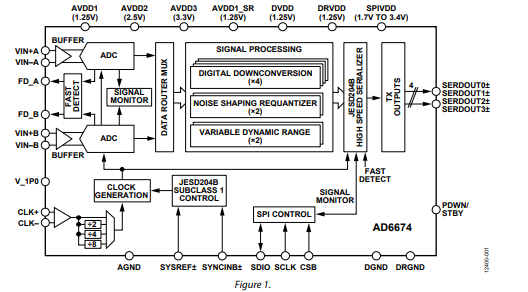

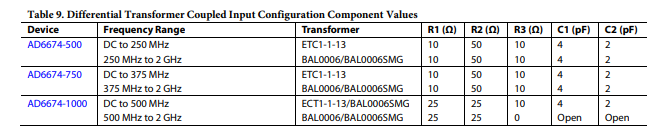

AD6674是一款385 MHz帶寬混合信號中頻(IF)接收器。內(nèi)置雙通道、14位1.0 GSPS/750 MSPS/500 MSPS模數(shù)轉(zhuǎn)換器(ADC)和各種數(shù)字信號算法模塊,包括四個寬帶DDC、一個NSR和VDR監(jiān)控。它具有片內(nèi)緩沖器和采樣保持電路,專門針對低功耗、小尺寸和易用性而設(shè)計。該產(chǎn)品設(shè)計支持通信應(yīng)用,能夠?qū)崿F(xiàn)高達(dá)2 GHz的寬帶寬模擬信號采樣。AD6674針對寬輸入帶寬、高采樣速率、出色的線性度和小封裝低功耗而優(yōu)化。

這款雙通道ADC內(nèi)核采用多級、差分流水線架構(gòu),并集成了輸出糾錯邏輯。每個ADC均具有寬帶寬輸入,支持用戶可選的各種輸入范圍。集成基準(zhǔn)電壓源可簡化設(shè)計考量。

數(shù)據(jù)表:*附件:AD6674 385MHz BW IF分集接收機技術(shù)手冊.pdf

應(yīng)用

特性

- JESD204B(子類1)編碼串行數(shù)字輸出

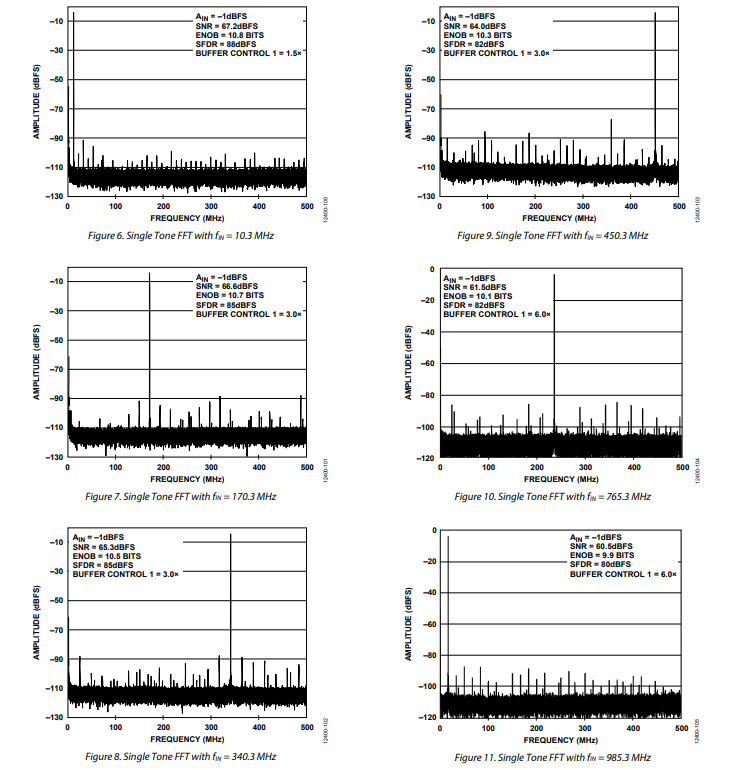

- 帶內(nèi)SFDR = 83 dBFS (340 MHz時,750 MSPS)

- 帶內(nèi)SNR = 66.7 dBFS (340 MHz時,750 MSPS)

- 750 MSPS 時每通道總功耗:1.4 W(默認(rèn)設(shè)置)

- 噪聲密度 = -153 dBFS/Hz (750 MSPS)

- 1.25 V、2.5 V和3.3 V 直流電源供電

- 靈活的輸入范圍

- AD6674-750和AD6674-1000

1.46 V p-p至1.94 V p-p(標(biāo)稱值1.70 V p-p) - AD6674-500

1.46 V p-p至2.06 V p-p(標(biāo)稱值2.06 V p-p)

- AD6674-750和AD6674-1000

- 95 dB通道隔離/串?dāng)_

- 幅度檢測位支持實現(xiàn)高效自動增益控制(AGC)

- 噪聲整形再量化器(NSR)選項支持主接收機功能

- 可變動態(tài)范圍(VDR)選項支持?jǐn)?shù)字預(yù)失真(DPD)功能

- 每通道集成 2 個寬帶數(shù)字處理器

- 差分時鐘輸入

- 整數(shù)時鐘分頻值:1、2、4或8

- 節(jié)能的關(guān)斷模式

- 靈活的 JESD204B 通道配置

- 小信號擾動

框圖

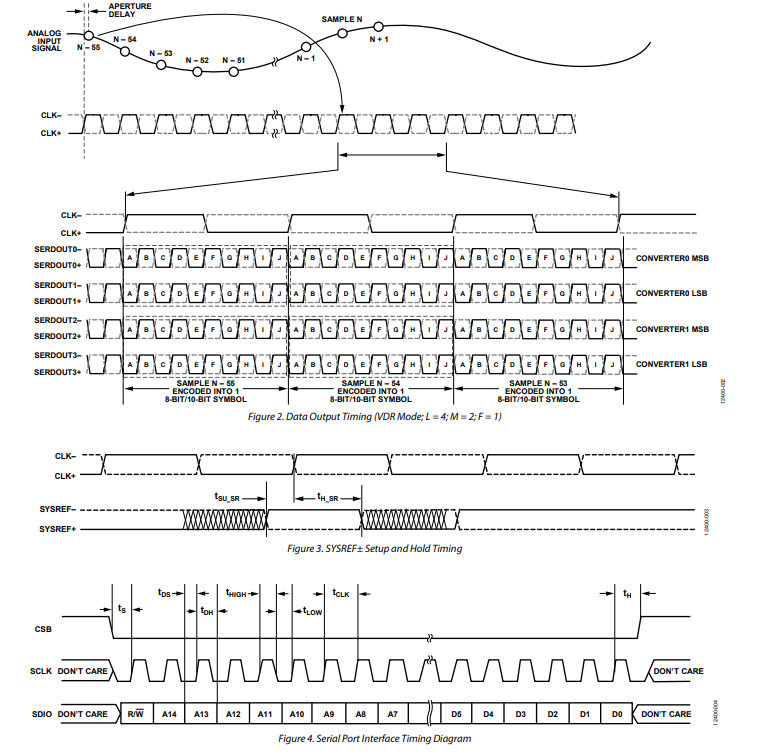

時序圖

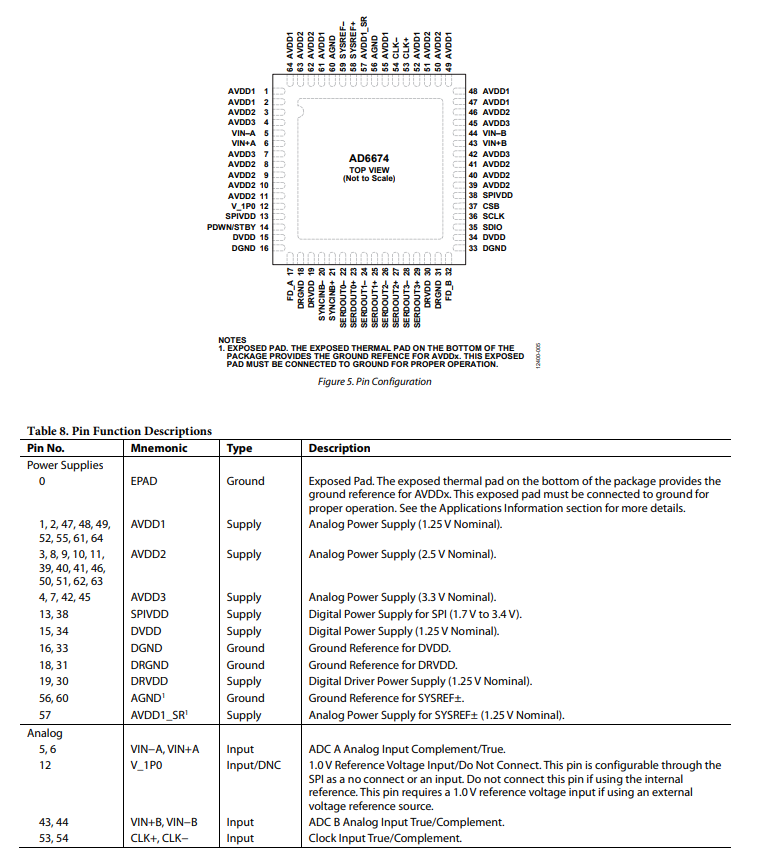

引腳配置描述

典型性能特征

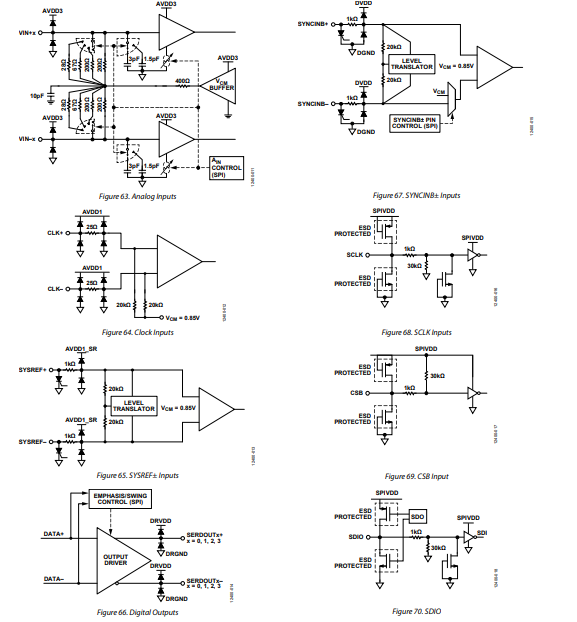

等效電路

AD6674有兩個模擬輸入通道和兩個JESD204B輸出通道。AD6674旨在對高達(dá)2 GHz的寬帶寬模擬信號進行采樣。其優(yōu)化設(shè)計用于實現(xiàn)寬帶寬、高采樣速率、出色的線性度以及小封裝低功耗。

雙ADC內(nèi)核采用差分流水線架構(gòu),集成輸出誤差校正邏輯。每個ADC具有寬帶寬輸入,支持多種用戶可選輸入范圍。集成的電壓基準(zhǔn)簡化了設(shè)計考量。

AD6674具備多項功能,可簡化通信接收器中的自動增益控制(AGC)功能。可編程閾值檢測器能夠監(jiān)測ADC數(shù)據(jù)輸出流的功率。當(dāng)檢測到的功率超過可編程閾值(通過寄存器0x24B設(shè)置)時,快速檢測指示燈將變高。由于該閾值指示燈具有低延遲特性,用戶可以快速降低系統(tǒng)增益,以避免ADC輸入出現(xiàn)過載情況。

超速率1模式下的JESD204B高速串行輸出數(shù)據(jù)速率可配置為單通道(L = 1)和雙通道(L = 2),具體取決于采樣速率和抽取率。通過SYSREF?和SYNCIN?輸入引腳支持多路復(fù)用和設(shè)備間同步。

ADC架構(gòu)

該架構(gòu)采用輸入緩沖偽差分ADC。輸入緩沖器旨在提供一個與模擬輸入信號相匹配的終端阻抗。這種終端連接可以通過使用SPDT來切換驅(qū)動/放大器的電源實現(xiàn)。圖43展示了輸入緩沖器的設(shè)置。為實現(xiàn)高線性度、低噪聲和低功耗,對終端進行了優(yōu)化。輸入緩沖器具有高輸入阻抗(可降低驅(qū)動源的負(fù)載),并從ADC的最終量化級獲取反饋。反饋路徑中的延遲有助于偽差分電路在采樣瞬間像連續(xù)時間運算放大器一樣工作。在時鐘上升沿進行采樣。

模擬輸入注意事項

AD6674的模擬輸入為差分信號。內(nèi)部共模電壓為2.05 V。時鐘信號交替切換輸入電路,在采樣模式和保持模式之間切換。當(dāng)輸入電路切換到采樣模式時,它會在半個時鐘周期內(nèi)對輸入電容器進行采樣和設(shè)置。采樣保持電路中的每個電容器都有一個低阻抗驅(qū)動源。此外,可在輸入的每個部分放置低Q值電感或鐵氧體磁珠,以降低模擬輸入的高差分電容,從而實現(xiàn)寬輸入帶寬。使用低Q值電感或鐵氧體磁珠會在驅(qū)動源與轉(zhuǎn)換器輸入端之間引入寄生極點。寄生極點會產(chǎn)生一個單端等效電容,使輸入與無源網(wǎng)絡(luò)分離。這種未端接的低通濾波器會限制輸入帶寬,從而影響性能。有關(guān)詳細(xì)信息,請參考《AN - 742:應(yīng)用筆記,電壓反饋運算放大器》,編號為AN - 742,出版于2005年4月,可在analog.com網(wǎng)站獲取。一般來說,進行精密設(shè)計時,需使源阻抗匹配戴維南等效值,該等效值是通過對模擬輸入的公共模式設(shè)置進行建模得出的。內(nèi)部基準(zhǔn)緩沖器會產(chǎn)生差分基準(zhǔn),從而確定ADC內(nèi)核的比例。

通過設(shè)置ADC的最大差分配置,可實現(xiàn)最高SNR性能。在共模電壓為1.9 V的情況下,AD6674 - 1000的滿量程峰值 - 峰值范圍為1.46 V p - p至2.06 V p - p,而AD6674 - 500的默認(rèn)值為1.70 V p - p,額定值為2.06 V p - p。

不同輸入配置

有多種方法可優(yōu)化AD6674的性能,包括有源和無源方式。然而,最佳性能是通過有源方式實現(xiàn)的。

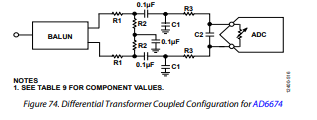

對于需要SNR和SFDR的應(yīng)用,建議使用變壓器耦合和共模輸入配置(見圖74和表9),因為這種配置可實現(xiàn)最佳性能,且不會影響AD6674的真實性能。

為了對混疊頻率進行鏡像處理,建議使用雙巴倫(見圖75和表9)。對于接近或高于AD6674奈奎斯特頻率的頻率,建議使用雙巴倫,以去除前端無源元件,確保寬帶寬工作(見圖74和表9)。

-

接收器

+關(guān)注

關(guān)注

15文章

2644瀏覽量

77119 -

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

4013瀏覽量

130100 -

IF

+關(guān)注

關(guān)注

1文章

64瀏覽量

27535 -

ADC

+關(guān)注

關(guān)注

0文章

226瀏覽量

16845

發(fā)布評論請先 登錄

請問AD6674的VDR功能有什么好處?

RAKE接收機與分集接收

385MHz帶寬中頻分集接收機

AD6674 385 MHz BW IF分集接收機

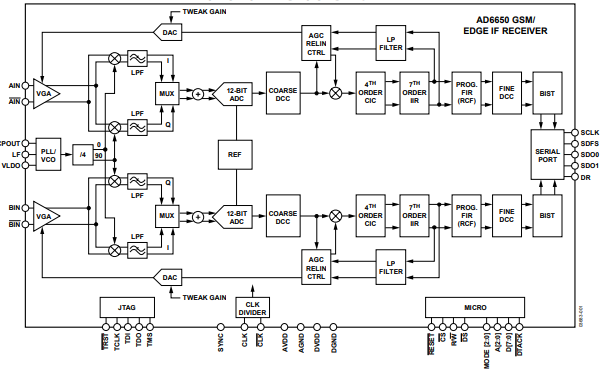

AD6650:分集IF-to-基帶GSM/EDGE窄帶接收機數(shù)據(jù)表

AD6650分集中頻至基帶GSM/EDGE窄帶接收機技術(shù)手冊

AD6674 385MHz BW IF分集接收機技術(shù)手冊

AD6674 385MHz BW IF分集接收機技術(shù)手冊

評論