概述

ADF4196頻率合成器可以用來在無線接收機和發(fā)射機的上變頻和下變頻部分實現(xiàn)本振(LO),其結構專門設計用來滿足基站的GSM/EDGE鎖定時間要求,其快速建立功能則使ADF4196非常適合脈沖多普勒雷達應用。

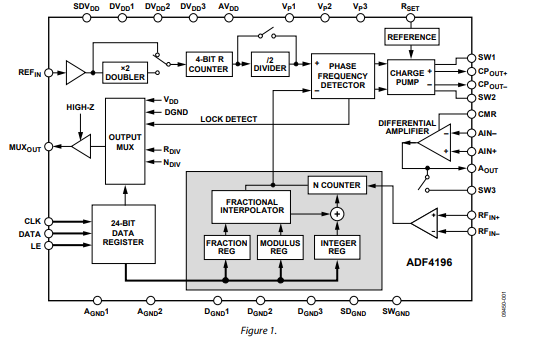

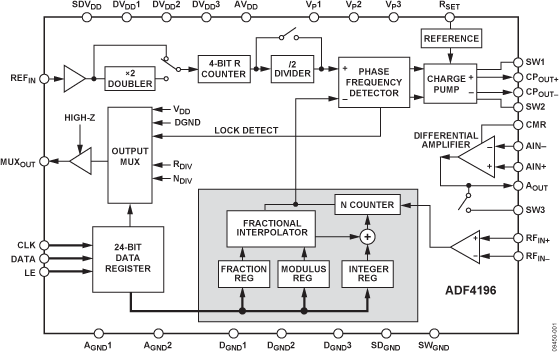

ADF4196由低噪聲數(shù)字鑒頻鑒相器(PFD)和精密差分電荷泵組成。還有一個差分放大器,用來將電荷泵的差分輸出轉換為外部電壓控制振蕩器(VCO)的單端電壓。Σ-Δ型小數(shù)插值器與N分頻器一起使用,能夠實現(xiàn)可編程模數(shù)小數(shù)N分頻。此外,4位參考(R)分頻器和片內倍頻器允許PFD輸入端的參考信號(REFIN)頻率為可選值。

如果頻率合成器與外部環(huán)路濾波器和VCO一起使用,則可以實現(xiàn)完整的鎖相環(huán)(PLL)。開關結構確保PLL能在GSM時隙保護期間內建立,而無需第二PLL及相關的隔離開關。與以前的乒乓式GSM PLL結構相比,這種結構能節(jié)省成本,降低復雜度,減小PCB面積,并減少屏蔽和特性測試工作。

數(shù)據(jù)表:*附件:ADF4196低相位噪聲,快速解決6GHz鎖相頻率合成器技術手冊.pdf

應用

- GSM/EDGE基站

- PHS基站

- 脈沖多普勒雷達

- 儀器儀表和測試設備

- 波束形成/相控陣系統(tǒng)

特性

- 快速建立小數(shù)N

分頻PLL結構 - 單個PLL可取代乒乓式頻率合成器

- 在5 μs內完成整個GSM頻段上的跳頻,相位建立時間低于20 μs

- 相位誤差:1度rms

(4 GHz RF輸出) - 數(shù)字可編程輸出相位

- 數(shù)字可編程輸出相位

- RF輸入范圍最高可達6 GHz

- 三線式串行接口

- 片內低噪聲差分放大器

- 相位噪聲品質因數(shù):–216 dBc/Hz

- 利用ADIsimPLL可實現(xiàn)環(huán)路濾波器設計

框圖

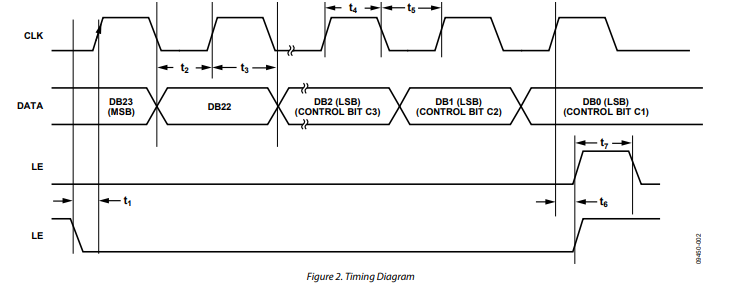

時序圖

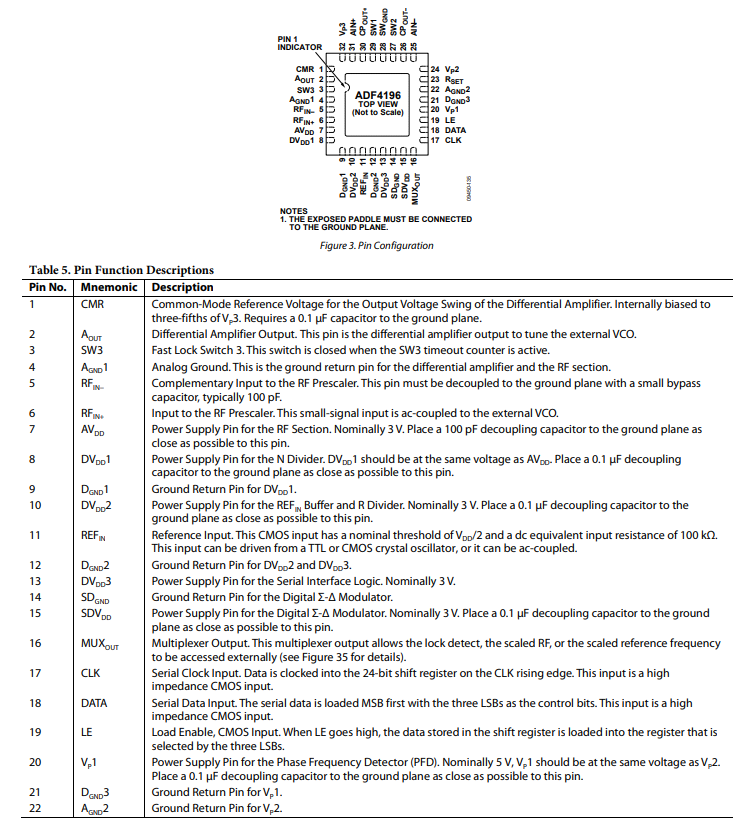

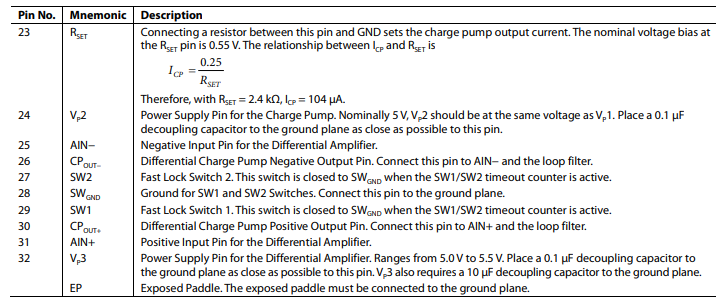

引腳配置描述

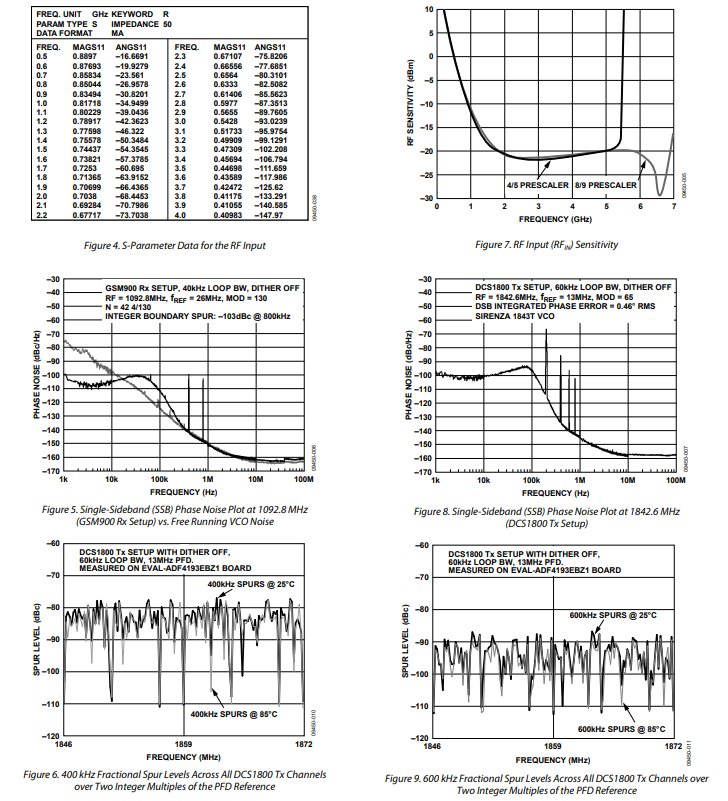

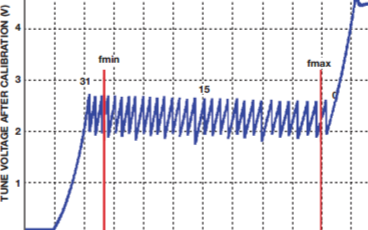

典型性能特征

總體描述

ADF4196專為滿足GSM基站要求而設計,特別是針對乒乓解決方案的定時需求。它也可用于多普勒雷達應用。ADF4196基于快速鎖定原理工作,使用窄環(huán)路帶寬進行頻率鎖定,并在實現(xiàn)頻率鎖定后采用窄環(huán)路帶寬。

通過增加電荷泵電流來拓寬環(huán)路帶寬。為在變化的電荷泵電流下保持穩(wěn)定性,ADF4196包括用于改變環(huán)路濾波器組件值的開關。

窄環(huán)路帶寬可確保滿足相位噪聲和雜散規(guī)格要求。差分電荷泵和環(huán)路濾波器拓撲結構確保在拓寬環(huán)路帶寬時實現(xiàn)快速鎖定,并且在環(huán)路恢復到窄帶寬模式以進行正常操作時,仍能保持快速鎖定帶來的優(yōu)勢。

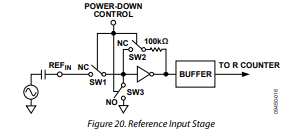

參考輸入

參考輸入級如圖20所示。開關SW1和SW2通常閉合,開關SW3通常斷開。掉電時,SW3閉合,SW1和SW2斷開,以確保在掉電期間**REF_{IN}**引腳不會有負載。**REF_{IN}**的下降沿是鑒頻鑒相器(PFD)正沿觸發(fā)的有效沿。

R計數(shù)器和倍頻器

4位R計數(shù)器可對輸入?yún)⒖碱l率進行分頻,以產生PFD的參考時鐘。可通過觸發(fā)R計數(shù)器的翻轉 - 翻轉功能實現(xiàn)額外的二分頻。使用此選項的額外優(yōu)勢是,PFD參考時鐘的間隔比為50/50。該比率可使快速鎖定定時器的最大間隔最大化,該定時器由PFD的下降沿生成,上升沿為有效沿。建議對于大于2的偶數(shù)R分頻值啟用此翻轉 - 翻轉功能。通過對**REF_{IN}**頻率進行分頻,可將翻轉 - 翻轉功能的頻率提高到120MHz以上。

在4位R計數(shù)器之前,可使用一個可選倍頻器,用于處理低至20MHz的**REF_{IN}**頻率。通過這些可編程選項,**REF_{IN}**與PFD之間的分頻比范圍為0.5至30。

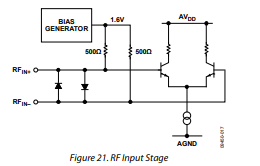

射頻輸入級

射頻輸入級如圖21所示。其后接兩級限幅放大器,用于生成預分頻器所需的電流模式邏輯(CML)時鐘電平。有兩種預分頻器選項:4/5和8/9。對于N分頻器值大于80的情況,選擇8/9預分頻器。

圖21. 射頻輸入級

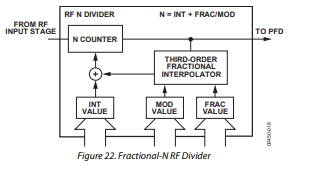

射頻N分頻器

射頻N分頻器可在鎖相環(huán)(PLL)反饋路徑中實現(xiàn)分數(shù)分頻比。分頻比中的整數(shù)部分和分數(shù)部分通過獨立寄存器編程,如圖22所示,并在“INT、FRAC和MOD關系”部分進行了說明。允許的整數(shù)分頻比范圍為26至511,三階Σ-Δ調制器可在整數(shù)步長之間對分數(shù)值進行插值。

INT、FRAC和MOD關系

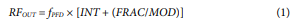

通過串行接口編程的INT、FRAC和MOD值,能夠生成間隔為PFD參考頻率分數(shù)倍的射頻輸出頻率。N分頻器值由以下公式構成,用于計算外部VCO的射頻輸出頻率(RF_{OUT}):

其中:

- **RF_{OUT}**是外部VCO的輸出頻率。

- **f_{PFD}**是PFD參考頻率。

選擇MOD的值以獲得所需的信道步長與可用參考頻率的比值。然后,根據(jù)所需的輸出頻率編程INT和FRAC值。有關更多信息,請參見“應用信息”部分。

-

頻率合成器

+關注

關注

5文章

330瀏覽量

33836 -

ADF4196

+關注

關注

0文章

3瀏覽量

5754 -

PFD

+關注

關注

0文章

22瀏覽量

14971

發(fā)布評論請先 登錄

低相位噪聲電壓控制振蕩器(VCO)和穩(wěn)定基準電壓構成的頻率合成器

基于鎖相環(huán)芯片ADF4106的工作特性設計頻率合成器

ADI推出新款PLL頻率合成器ADF4151和ADF4196

TI推出LMX2581業(yè)界最低相位噪聲的頻率合成器

面向 RF 應用的低相位噪聲頻率合成器

ADF4196 低相位噪聲,快速解決6 GHz 鎖相頻率合成器

ADF4196:低相位噪聲、快速建立、6 GHz PLL頻率合成器數(shù)據(jù)表

ADF4193:低相位噪聲、快速建立PLL頻率合成器數(shù)據(jù)表

CN0369 低相位噪聲的轉換鎖相環(huán)頻率合成器

基于ADF4111的鎖相環(huán)頻率合成器設計

ADF4196低相位噪聲,快速解決6GHz鎖相頻率合成器技術手冊

ADF4196低相位噪聲,快速解決6GHz鎖相頻率合成器技術手冊

評論