概述

MAX3523是一款超越DOCSIS 3.1上游發射要求的可編程增益放大器(PGA)。PGA滿足DOCSIS 3.1雜散限制,同時在5MHz至204MHz的射頻帶寬范圍內發射68dBmV的組合輸出功率。增益使用SPI 3線接口在60dB的范圍內進行控制,以1dB為步長。該器件采用Maxim的高壓CMOS工藝,能夠提供高動態范圍,同時充分降低+5V電源軌下的功耗。

MAX3523采用20引腳5mm x 5mm x 0.75mm TQFN封裝,工作溫度范圍為0°C至+70°C。

數據表:*附件:MAX3523低功耗DOCSIS 3.1可編程增益放大器技術手冊.pdf

應用

- 電纜調制解調器(CM)

- 用戶端設備(CPE)

- DOCSIS 3.1上游(D3.1 US)

特性

- 在符合DOCSIS 3.1要求的同時提供 +68dBmV輸出功率

- 輸出帶寬范圍:5MHz–204MHz

- 使用5V電源電壓時的功耗為3.5W

- 可編程電源代碼實現低功耗操作

- 在調制解調器輸出為+65dBmV時超越了OFDM滿載分配的雜散要求

- 采用帶裸露焊盤的20L 5mm x 5mm x 0.75mm TQFN封裝

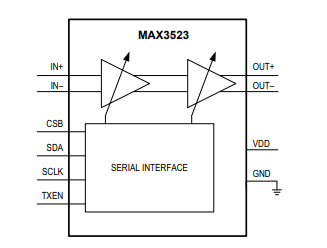

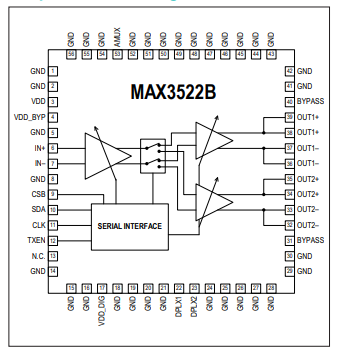

簡化框圖

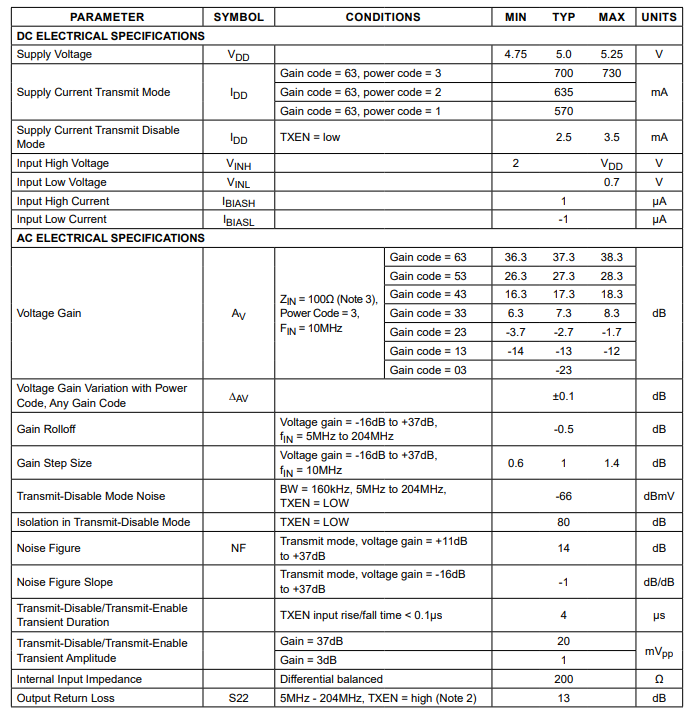

電特性

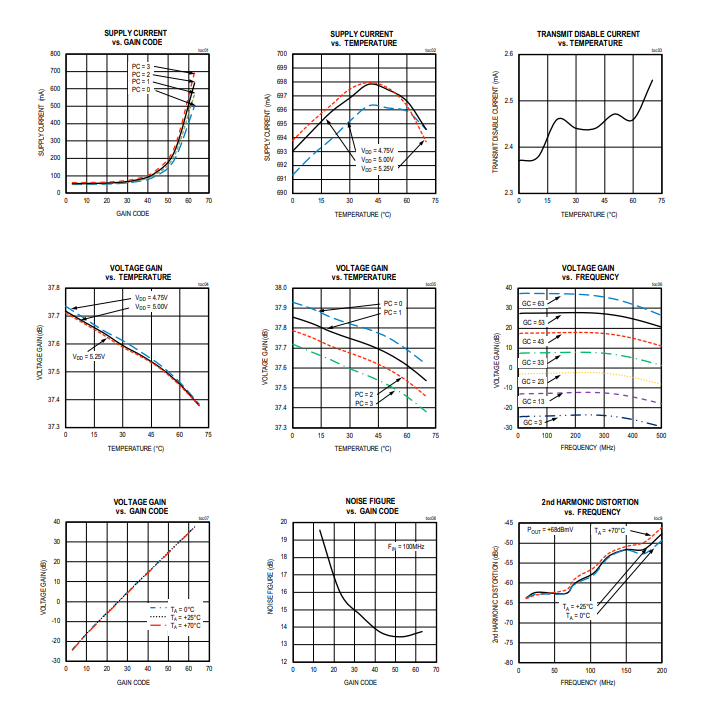

典型操作特性

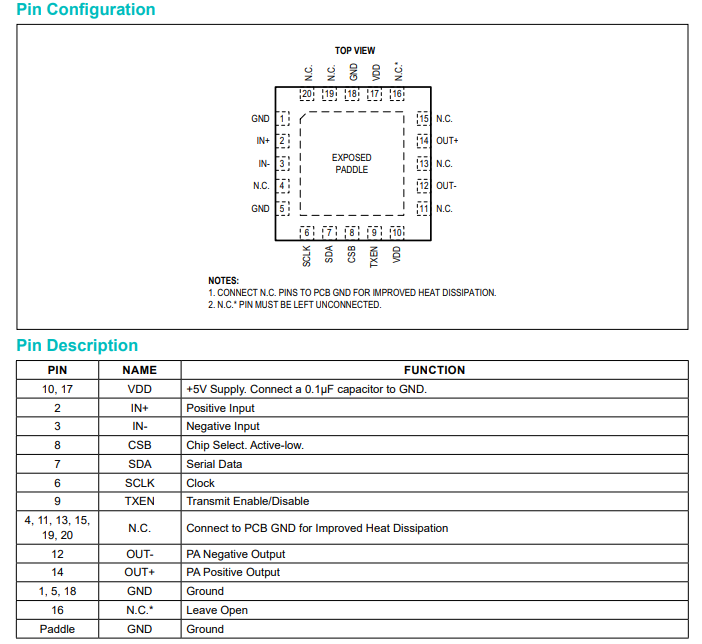

引腳配置描述

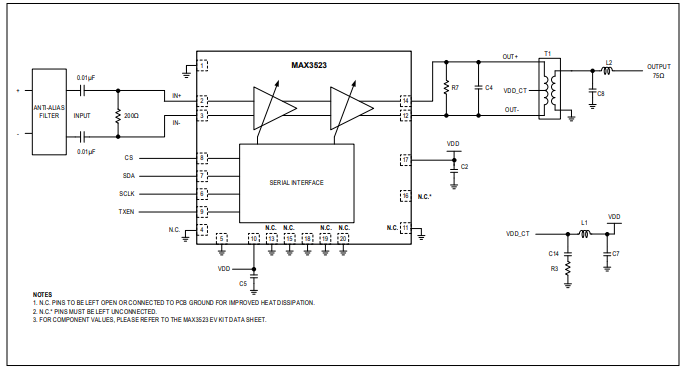

應用電路

應用信息

電源編碼

該器件的設計旨在滿足DOCSIS 3.1的嚴格線性度要求(功率碼3 )。使用較低的電源編碼(PC = 2、1或0 )可降低器件的工作電流。全量程增益編碼之間的增益差異通常小于0.1dB。

發射禁用模式

在DOCSIS系統中,通過將TXEN置低,可使MAX3523進入發射禁用模式。在滿足DOCSIS 3.1要求的情況下,應在發送之前將TXEN保持低電平。

如果需要更改增益碼或電源編碼,新的PC或GC碼值應在發射禁用(TXEN低 )時進行時鐘控制。MAX3523應在SCLK的第12個上升沿設置新的工作點。此操作應在傳輸突發之間完成。

輸出電路

輸出電路是一個漏極開路差分放大器。輸出應進行電阻端接,如典型應用電路所示。應使用50Ω - 75Ω的射頻變壓器作為器件差分輸出與非平衡75Ω負載之間的接口。

放大器的性能取決于端接電阻的值。使用典型應用電路中所示的R7端接電阻可獲得額定性能。增加該電阻的值會提高增益并改善信噪比,但會增加輸出回波損耗。

變壓器的初級電感可能會隨溫度變化。應提供足夠的初級電感,以確保在溫度變化時仍能保持寬帶輸出能力。

輸入電路

MAX3523的差分輸入阻抗為200Ω。但在典型應用中,由于需要100Ω差分源匹配,因此需使用一個200Ω匹配電阻,如典型應用電路所示。

該器件具有足夠的增益和線性度,當輸入信號為+31dBmV時,可產生+68dBmV的輸出電平。如果使用高于+31dBmV的輸入電平,可能會導致三階互調失真產物增大。

布局問題

精心設計的印刷電路板(PCB)是射頻電路的關鍵部分。為實現最佳性能,需關注電源供應布局問題以及輸出電路布局。MAX3523評估版(EV)電路板可用作PCB設計的參考指南。其電氣性能經過了全面測試,是優秀的參考資料。有關更多信息,請參考MAX3523評估套件。

輸出電路布局

盡可能縮短輸出走線長度。器件與變壓器之間的串聯電感會在較高的工作頻率范圍內降低性能。為保持輸出網絡的平衡,請使差分走線的長度盡可能匹配。

電源供應布局

為使器件不同部分之間的耦合最小化,理想的電源供應布局是星形配置。這種配置在電源分支節點處有一個大容值的去耦電容。電源供應走線從該節點出發,分別連接到電路的各個部分。在每條走線的末端放置一個去耦電容,以提供非常低的阻抗。這種布局可在每個電源引腳處實現本地電源去耦。電源走線必須能夠承載最大電流,且不會產生明顯的電壓降。

外露焊盤熱特性考量

MAX3523的20引腳TQFN封裝的外露焊盤(EP)為芯片提供了低熱阻路徑。重要的是,印刷電路板的設計應使器件安裝在與該低熱阻路徑有熱接觸的位置。如有必要,應提供一個低電感的接地路徑。MAX3523評估板就是一個在熱性能和電氣性能方面都能提供最佳效果的示例。

-

pga

+關注

關注

1文章

113瀏覽量

42433 -

DOCSIS

+關注

關注

0文章

15瀏覽量

8788 -

可編程增益放大器

+關注

關注

0文章

29瀏覽量

8002

發布評論請先 登錄

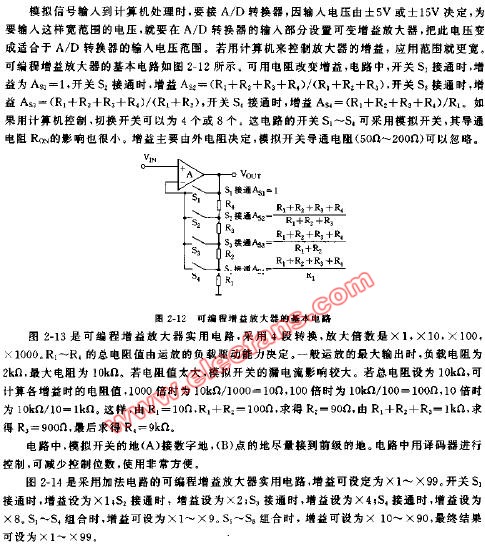

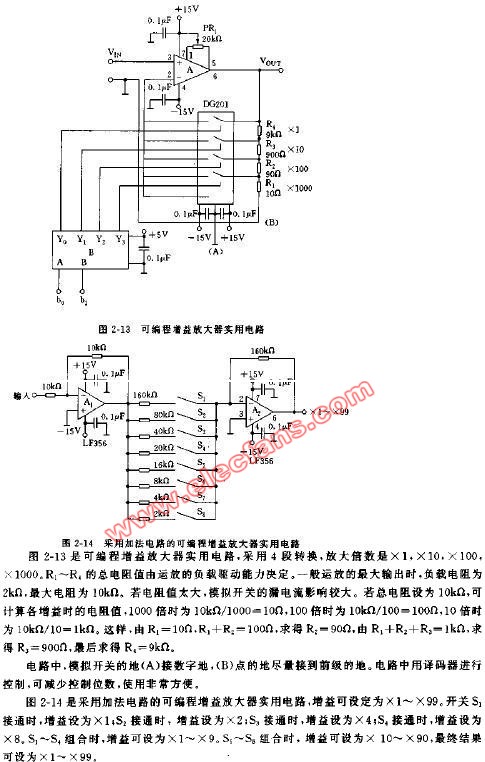

低功耗數字可編程增益放大器參考設計

用于 DOCSIS 3.0 上行路徑的可編程增益放大器 skyworksinc

MAX3523低功耗DOCSIS 3.1可編程增益放大器技術手冊

MAX3523低功耗DOCSIS 3.1可編程增益放大器技術手冊

評論