概述

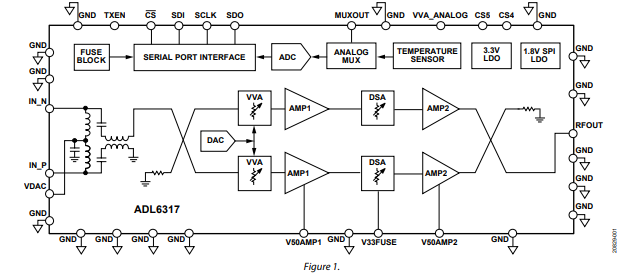

ADL6317 是一款發射可變增益放大器 (VGA),它可提供從射頻數模轉換器 (RF DAC)、收發器和片內系統 (SoC) 到功率放大器的接口。集成式平衡/不平衡轉換器和混合耦合器可以在 1500 MHz 至 3000 MHz 的頻率范圍內實現高性能 RF 能力。

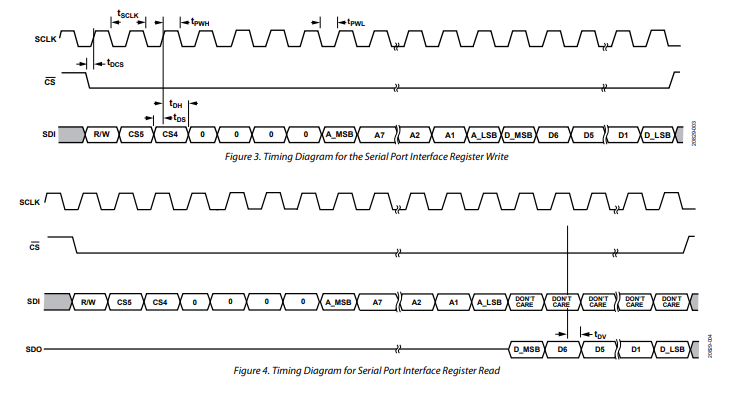

為了優化性能與功率水平,ADL6317 包含了電壓可變衰減器 (VVA)、高線性度放大器和數字分級衰減器 (DSA)。集成到 ADL6317 中的所有套件都可以通過 4 線串行端口接口 (SPI) 進行編程。

ADL6317 采用高級硅鍺 (SiGe)、雙極互補金屬氧化物半導體 (BiCMOS) 工藝制成。

數據表:*附件:ADL6317用于RF DAC和收發器的發射VGA技術手冊.pdf

應用

特性

- 提供從 RF DAC、收發器和 SoC 到功率放大器的接口的發射 VGA

- RF 輸出頻率范圍:1500 MHz 至 3000 MHz

- 采用偏置器提供 RF DAC 輸出的內部平衡/不平衡轉換器

- 使用片內 DAC 時的集成 VVA 衰減范圍:20.5 dB

- 2 級高線性度放大器

- RF DSA 衰減范圍:15.5 dB,步進分辨率為 0.5 dB

- 50 Ω 差分輸入和 50 Ω 單端輸出

- 可通過 4 線 SPI 完全編程

- 5 V 單電源

- 38 端子 10.5 mm × 5.5 mm LGA

框圖

時序圖

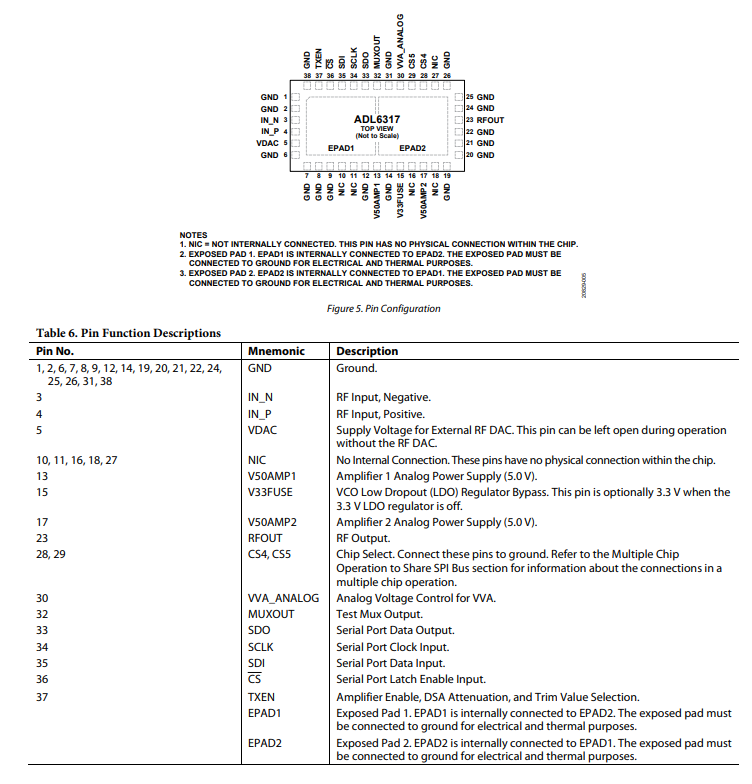

引腳配置描述

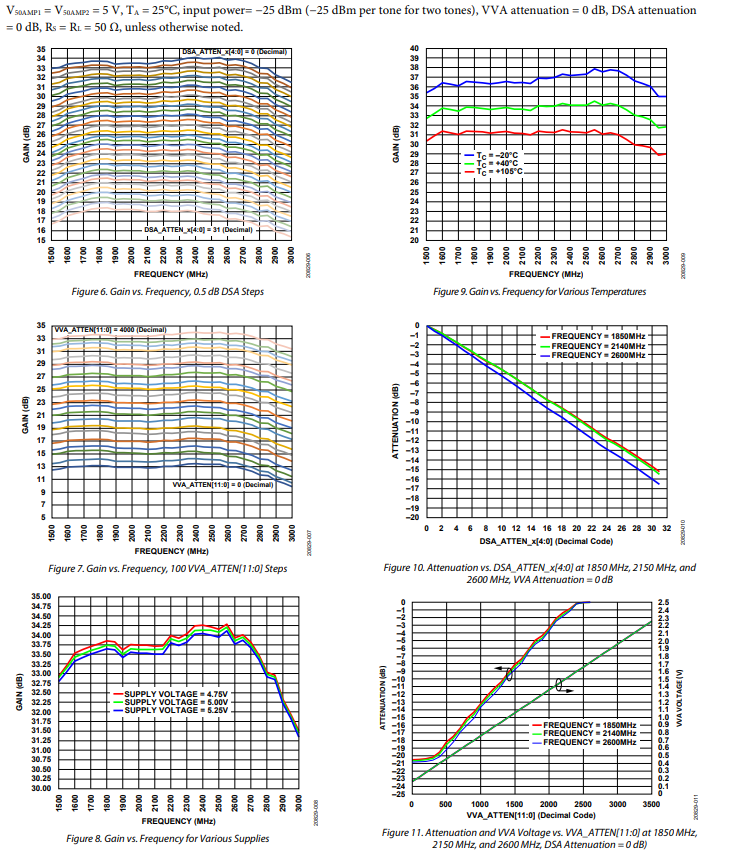

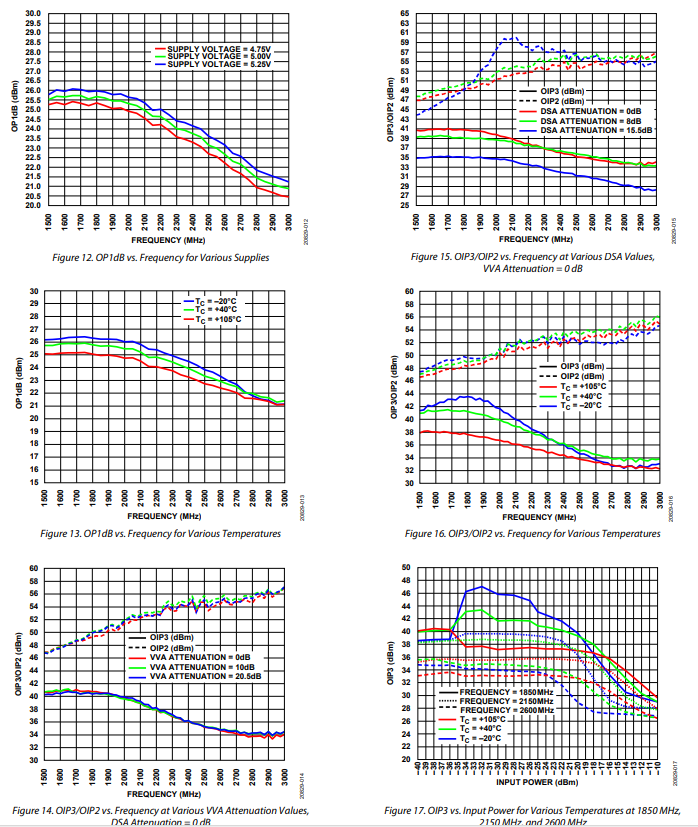

典型性能特征

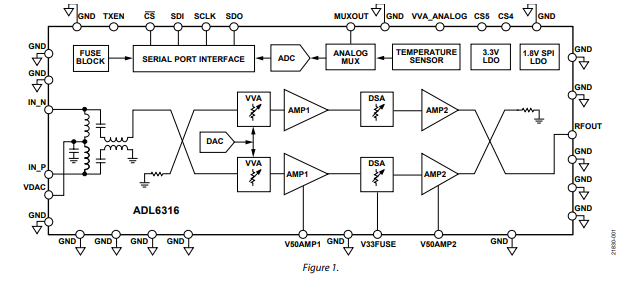

ADL6317是一款高度集成的發射可變增益放大器(VGA),用于在發射機中連接射頻數模轉換器(RF DAC)和功率放大器。ADL6317適用于高動態范圍多載波發射機設計。

ADL6317提供多種增益控制選項,集成了一個20.5 dB可變增益放大器(VGA),可通過片內DAC控制或外部電壓控制。它具有高線性度放大器、一個15.5 dB的射頻數字步進衰減器(DSA),以0.5 dB的步長進行衰減,隨后是第二級高線性度放大器。

將ADL6317的各個模塊組合起來,信號通過器件的路徑從差分輸入開始,由集成的平衡 - 不平衡變換器轉換為單端信號,然后由內部正交耦合器進行正交耦合。

接下來,集成的VVA、放大器1、DSA和放大器2會在射頻信號輸出到輸出端口之前對其幅度進行優化。ADL6317的所有集成模塊均可通過SPI進行編程。

帶DAC接口網絡的射頻輸入平衡 - 不平衡變換器

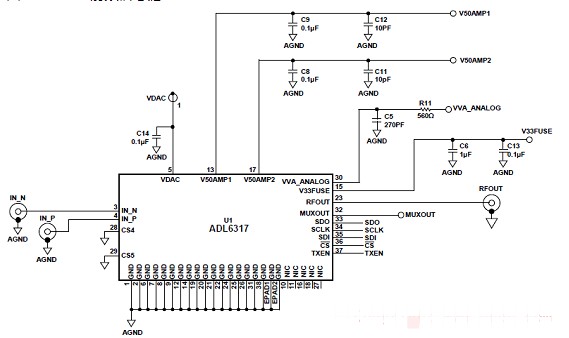

ADL6317通過集成的平衡 - 不平衡變換器,將單通道50Ω輸入差分信號轉換為單端信號。寬帶匹配使DAC能夠在1500 MHz至3000 MHz的頻率范圍內進行操作,并且包含一個偏置三通,為RF DAC提供直流偏置。

正交混合器

射頻輸入和射頻輸出端的集成正交混合器可實現寬帶反射系數匹配,并與低輸入和輸出回波損耗的RF DAC實現功率匹配。

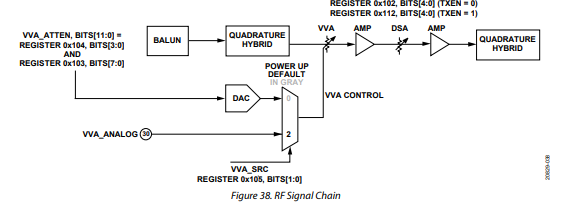

射頻信號鏈

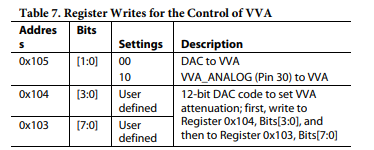

射頻路徑包括一個20.5 dB的VVA、第一級固定增益放大器(15.5 dB DSA)和第二級固定增益放大器(見圖38 )。ADL6317對VVA衰減有兩種控制模式:使用集成12位DAC的內部模擬控制,以及外部模擬控制。對于內部控制,使用寄存器0x04,位[3:0]和寄存器0x03,位[7:0]來設置衰減量。數字位采用雙緩沖,以避免主載波毛刺。因此,在寫入寄存器0x03之前,必須先寫入寄存器0x04。對于VVA的外部模擬控制(引腳30 ),需將電壓施加到VVA_ANALOG引腳(引腳30 )。圖38展示了用于VVA控制的寄存器寫入示例。

接下來,固定增益放大器采用正交平衡配置。DSA提供15.5 dB的衰減范圍,步長為0.5 dB。數字5位DSA衰減控制在寄存器0x112的位[4:0]中。最后,第二級固定增益放大器采用正交平衡配置。

-

收發器

+關注

關注

10文章

3819瀏覽量

111188 -

dac

+關注

關注

44文章

2713瀏覽量

197065 -

VGA

+關注

關注

5文章

579瀏覽量

66293

發布評論請先 登錄

RadioVerse生態系統中的寬帶收發器

RadioVerse生態系統中的寬帶收發器分享!

什么是用于RF收發器的簡單基帶處理器?

MAX2830 直接變頻RF收發器

VGA光纖收發器是什么

ADL6316:500 MHz至1000 MHz發射VGA,與射頻DAC和收發器配合使用數據表

基于ADI ADL6317輔助射頻(RF)增益增益(VGA)方案設計

ADL6317用于RF DAC和收發器的發射VGA技術手冊

ADL6317用于RF DAC和收發器的發射VGA技術手冊

評論