概述

ADMV4640是一款微波下變頻器,針對(duì)各種衛(wèi)星通信(SATCOM)用戶(hù)終端進(jìn)行了優(yōu)化,RF工作頻率范圍為10.7 GHz至12.7 GHz。

ADMV4640本振(LO)信號(hào)可從內(nèi)部通過(guò)片內(nèi)整數(shù)N分頻(INT)頻率合成器產(chǎn)生。內(nèi)部頻率合成器的LO頻率覆蓋范圍為8.7 GHz至10.7GHz。10.7 GHz至12.7 GHz范圍內(nèi)的輸入RF信號(hào)會(huì)下變頻為1.4 GHz至2.2 GHz的輸出中頻(IF)信號(hào)。芯片具有濾波特性以抑制6.7 GHz至8.7 GHz的鏡像頻段。片內(nèi)低噪聲放大器在混頻器前集成了6 dB步進(jìn)衰減器,使用戶(hù)能夠在較低噪聲系數(shù)和較高線性度之間進(jìn)行權(quán)衡。此外,該芯片還在IF輸出端集成了數(shù)字步進(jìn)衰減器,可提供高達(dá)31 dB的增益控制范圍和1 dB步進(jìn),以便對(duì)后續(xù)電纜損耗進(jìn)行調(diào)整。

數(shù)字串行外設(shè)接口(SPI)可對(duì)該器件輕松編程。除了數(shù)字SPI控制之外,模擬控制引腳(RX_MUTE)可快速關(guān)斷所有電路,讓接收器進(jìn)入待機(jī)模式以便省電。模擬通用輸入-輸出(AGPIO)引腳可用作由片內(nèi)模數(shù)轉(zhuǎn)換器(ADC)讀取的輸入,或與絕對(duì)溫度(PTAT)電壓成正比的內(nèi)部模擬輸出。還提供三個(gè)數(shù)字GPIO引腳,用于輸出邏輯電平以使用SPI控制外部器件。

ADMV4640下變頻器采用緊湊的散熱增強(qiáng)型、6 mm × 6 mm、40引腳引腳架構(gòu)芯片級(jí)封裝(LFCSP)。ADMV4640工作殼溫范圍為?40°C至+85°C。

數(shù)據(jù)表:*附件:ADMV4640集成小數(shù)N分頻PLL和VCO的Ku頻段下變頻器技術(shù)手冊(cè).pdf

應(yīng)用

- SATCOM用戶(hù)終端

特性

- 集成PLL的X/Ku頻段至IF下變頻器

- RF輸入頻率范圍:10.7 GHz至12.7 GHz

- 內(nèi)部LO頻率范圍:8.7 GHz至10.7 GHz

- 噪聲系數(shù):5.2 dB、最小衰減、LNA低增益模式

- 匹配、50 Ω、單端RF輸入和IF輸出

- 片內(nèi)溫度傳感器

- 片內(nèi)ADC

- 接收器頻率合成器鎖定檢測(cè)引腳

- 20 MHz時(shí)可通過(guò)四線式SPI接口編程

- 接收器待機(jī)功能

- 40引腳、6 mm × 6 mm LFCSP封裝

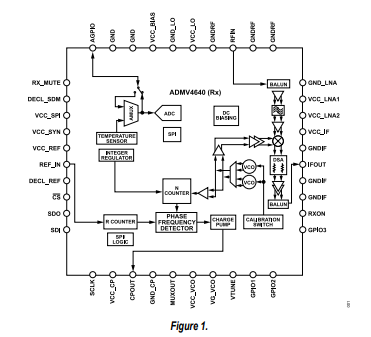

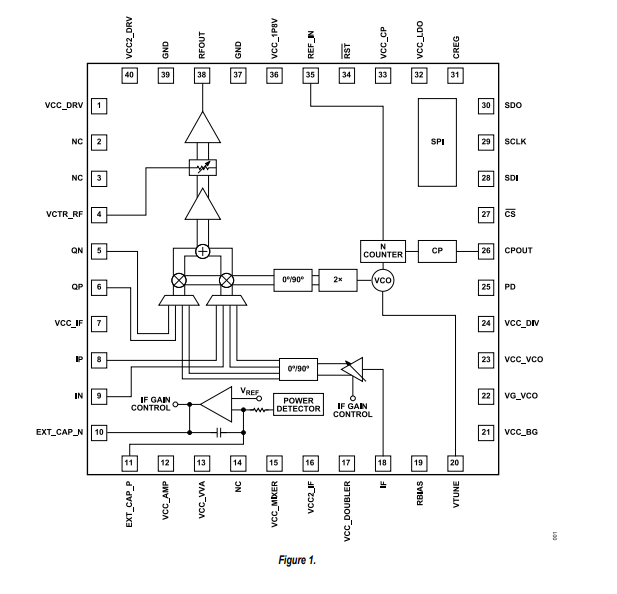

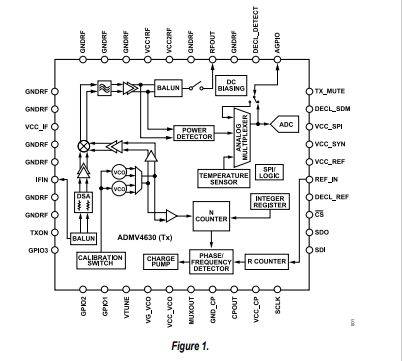

框圖

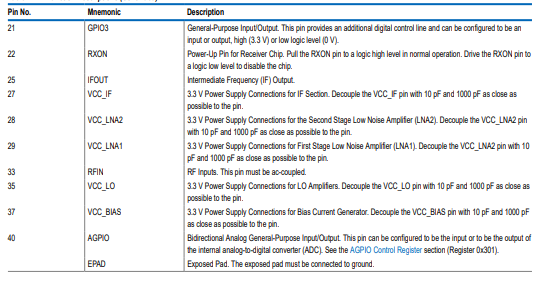

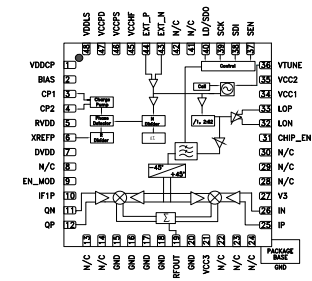

引腳配置描述

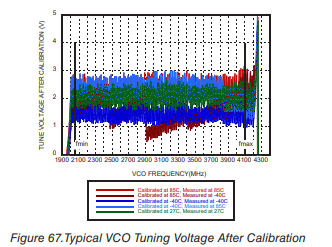

典型性能特征

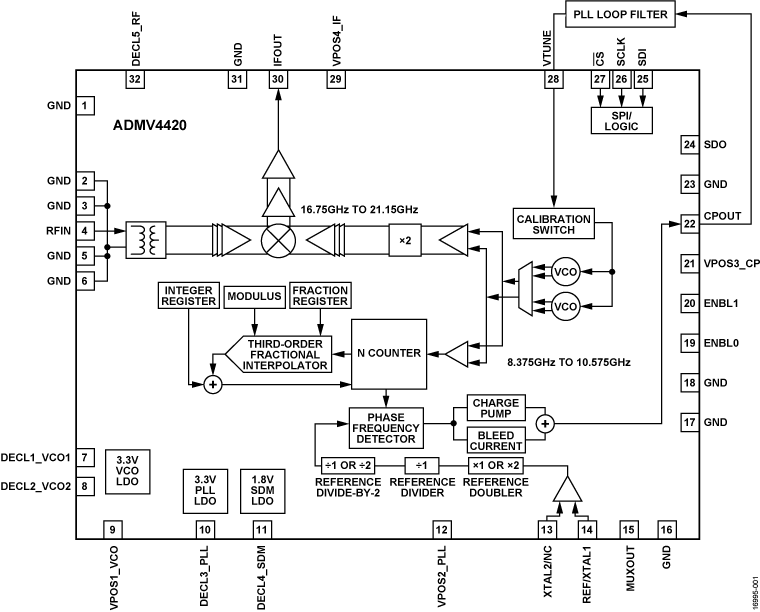

ADMV4640是一款針對(duì)工作在10.7 GHz至12.7 GHz頻段的各類(lèi)衛(wèi)星通信(SATCOM)用戶(hù)終端優(yōu)化的微波下變頻器。圖1為該器件的功能框圖。ADMV4640的數(shù)字設(shè)置通過(guò)SPI(串行外設(shè)接口)進(jìn)行控制。

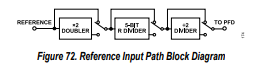

參考輸入級(jí)

參考輸入級(jí)如圖72所示,可由外部單端25 MHz信號(hào)源驅(qū)動(dòng)。需確保外部直流模塊用于參考輸入。

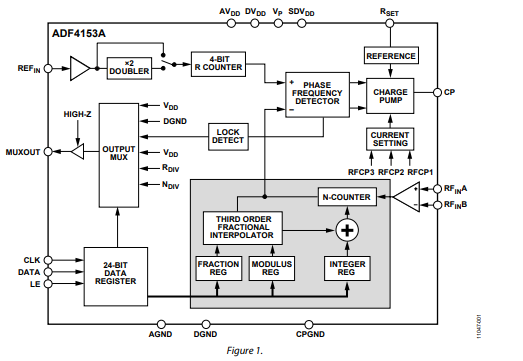

參考倍頻器、R計(jì)數(shù)器和參考二分頻器

內(nèi)部有一個(gè)參考倍頻2模塊(×2倍頻器,見(jiàn)圖72),用于生成更高的鑒相頻率(fpd)。通過(guò)設(shè)置寄存器0x20E的第3位(DOUBLER_EN位)使能參考倍頻器。

有兩個(gè)頻率分頻器:一個(gè)5比特R分頻器(1至32可選,見(jiàn)圖72)和一個(gè)二分頻模塊。這些分頻器將輸入?yún)⒖碱l率(fref)降低,以產(chǎn)生更低的fpd。通過(guò)設(shè)置寄存器0x20C的第4 - 0位(R_DIV位)來(lái)設(shè)置R計(jì)數(shù)器。

通過(guò)設(shè)置寄存器0x20E的第0位(RDNV2_SEL位)使能參考二分頻模塊。

整數(shù)模式和N計(jì)數(shù)器

ADMV4640合成器工作在整數(shù)模式(INT模式)。

N計(jì)數(shù)器在鎖相環(huán)(PLL)從壓控振蕩器(VCO)返回的反饋路徑中設(shè)置分頻比。分頻比由INT位值決定。使用寄存器0x200和寄存器0x201來(lái)設(shè)置INT位值。

INT值與參考路徑相結(jié)合,可生成間隔為fpd的VCO頻率。

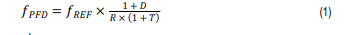

使用以下公式計(jì)算fpd,其中涉及fref和參考路徑配置參數(shù):

其中:

- D是參考倍頻器位(0或1)。

- R是5比特二進(jìn)制可編程計(jì)數(shù)器(1到31)的參考分頻比。

- T是參考二分頻比特(0或1)。

使用以下公式計(jì)算VCO頻率(fVCO):

其中:

- fLO是驅(qū)動(dòng)混頻器的本振頻率。

- N是INT的期望取值,INT是16比特整數(shù)值(0到65535)。

鑒相鑒頻器(PFD)和電荷泵(CP)

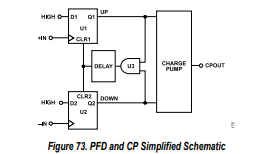

PFD接收來(lái)自R計(jì)數(shù)器和N計(jì)數(shù)器的輸入,產(chǎn)生一個(gè)與兩個(gè)計(jì)數(shù)器之間的相位和頻率差成比例的輸出。該比例信息輸出到一個(gè)CP電路,產(chǎn)生電流以驅(qū)動(dòng)外部環(huán)路濾波器,進(jìn)而適當(dāng)?shù)卦黾踊蚪档蚔TUNE調(diào)諧電壓。

圖73展示了PFD和CP的簡(jiǎn)化原理圖。U1和U2是雙D型觸發(fā)器,U3是一個(gè)接地門(mén)。PFD包含一個(gè)固定延遲元件,用于確保PFD傳遞函數(shù)中不存在死區(qū),從而保證參考雜散電平一致。

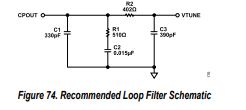

環(huán)路濾波器和電荷泵電流

為PLL定義環(huán)路濾波器取決于PFD頻率、N計(jì)數(shù)器值、VCO的調(diào)諧靈敏度特性(kVCO)以及所選的CP電流。較低的fpd允許PLL在INT模式下工作,這可以消除整數(shù)邊界雜散,但代價(jià)是帶內(nèi)相位噪聲更高。

在頻率規(guī)劃和fpd選擇時(shí)需謹(jǐn)慎,以確保帶內(nèi)相位噪聲性能符合要求,同時(shí)雜散電平在最終應(yīng)用可接受的范圍內(nèi)。

ADMV4640 - EVALZ評(píng)估板上實(shí)現(xiàn)的環(huán)路濾波器如圖74所示。CP電流(ICP)由寄存器0x22E設(shè)置。推薦默認(rèn)寄存器值0x0E。

-

變頻器

+關(guān)注

關(guān)注

256文章

7368瀏覽量

155617 -

微波

+關(guān)注

關(guān)注

16文章

1085瀏覽量

86059 -

pll

+關(guān)注

關(guān)注

6文章

985瀏覽量

138272 -

VCO

+關(guān)注

關(guān)注

14文章

320瀏覽量

71358

發(fā)布評(píng)論請(qǐng)先 登錄

ADMV4420 具有集成小數(shù) N 分頻 PLL 和 VCO 的 K 波段下變頻器

ADMV4530:帶集成小數(shù)N PLL和壓控振蕩器的雙模Ka波段上變頻器數(shù)據(jù)表

ADMV4420:集成小數(shù)N PLL和壓控振蕩器數(shù)據(jù)表的K波段下變頻器

UG-1404:評(píng)估集成小數(shù)N鎖相環(huán)和壓控振蕩器的ADMV4420,K波段下變頻器

HMC1190ALP6NE:寬帶High IP3雙通道下變頻器,帶小數(shù)N PLL和VCO,0.7-3.8 GHz數(shù)據(jù)表

ADRF6650:帶DVGA和PLL/VCO的雙下變頻器,450 MHz至2700 MHz數(shù)據(jù)表

ADMV4530具有集成小數(shù)N分頻PLL和VCO的雙模式Ka頻段上變頻器技術(shù)手冊(cè)

HMC1197集成小數(shù)N分頻PLL和VCO的寬帶直接正交調(diào)制器技術(shù)手冊(cè)

HMC1190ALP6NE集成小數(shù)N分頻PLL和VCO的寬帶高IP3雙通道下變頻器技術(shù)手冊(cè)

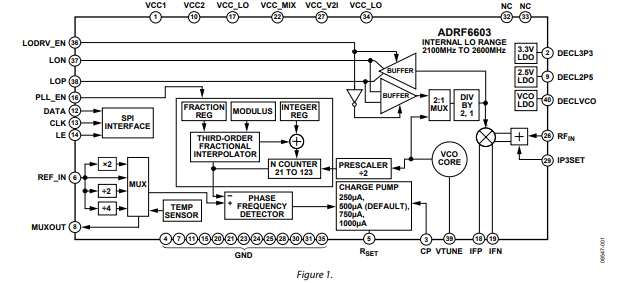

ADRF6603 1,100 MHz至3,200MHz接收混頻器,集成小數(shù)N分頻PLL和VCO技術(shù)手冊(cè)

ADMV4630集成小數(shù)N分頻PLL和VCO的Ku頻段上變頻器技術(shù)手冊(cè)

ADF4153A小數(shù)N分頻頻率合成器技術(shù)手冊(cè)

ADF4151小數(shù)N/整數(shù)N分頻PLL頻率合成器技術(shù)手冊(cè)

集成整數(shù) N 分頻 PLL 和 VCO 的 350-5000 MHz 寬帶接收混頻器 skyworksinc

ADMV4640集成小數(shù)N分頻PLL和VCO的Ku頻段下變頻器技術(shù)手冊(cè)

ADMV4640集成小數(shù)N分頻PLL和VCO的Ku頻段下變頻器技術(shù)手冊(cè)

評(píng)論