1984 年,在硅谷工作的Bernie Vonderschmitt、Ross Freeman 和 Jim Barnett 共同構建了一個設想,他們夢想創(chuàng)立一家不同于一般的公司。他們希望創(chuàng)建一家在整個新領域內(nèi)開發(fā)和推出先進技術的公司。并且,他們還希望以這種方式領導它:在這里工作的人們熱愛他們的工作、享受工作的樂趣,并對他們所從事的工作著迷。他們創(chuàng)造性地推出了“無晶圓半導體”公司的概念。

圖2-1 Ross Freeman(左)是FPGA的發(fā)明人,Bernie Vonderschmitt(右)是賽靈思公司的創(chuàng)始人

RossFreeman,這位密西根大學的畢業(yè)生,1984年提出了在那個晶體管堪比黃金的時代最為激進的想法——讓芯片就像一個空白的磁帶,可以隨由工程師在上面編程增添功能,就好像畫師在白布上任意涂鴉。而這念頭,又如一石激起千層浪,誕生了一個價值數(shù)十億美元的全新行業(yè)——可編程邏輯器件(PLD)。看,牛人是這樣看IC layout的,這是Ross Freeman在檢查全球第一款FPGA--XC2064

時光荏苒,光陰如箭,30多年過去,RossFreeman最初構建的可編程器件帝國已經(jīng)發(fā)生了翻天覆地的變化,恰如人間的滄海桑田,賽靈思還是賽靈思 ,但是FPGA已經(jīng)不是原來的FPGA了!從最初的膠合邏輯到嵌入式邏輯處理再到云計算人工智能加速處理單元再到賽靈思第四任CEO Vitor Peng帶來的ACAP平臺,與時俱進的賽靈思書寫了一個沒有競爭對手時不斷超越自己的勵志故事。

3月16日,剛上任不到兩個月的Vitor Peng來到中國,帶著他迷人的微笑,在長達近四個小時的時間里為中國媒體分享了他治下賽靈思的戰(zhàn)略并揭曉了一個有500億晶體管耗資10億美元打造的新品---ACAP平臺。

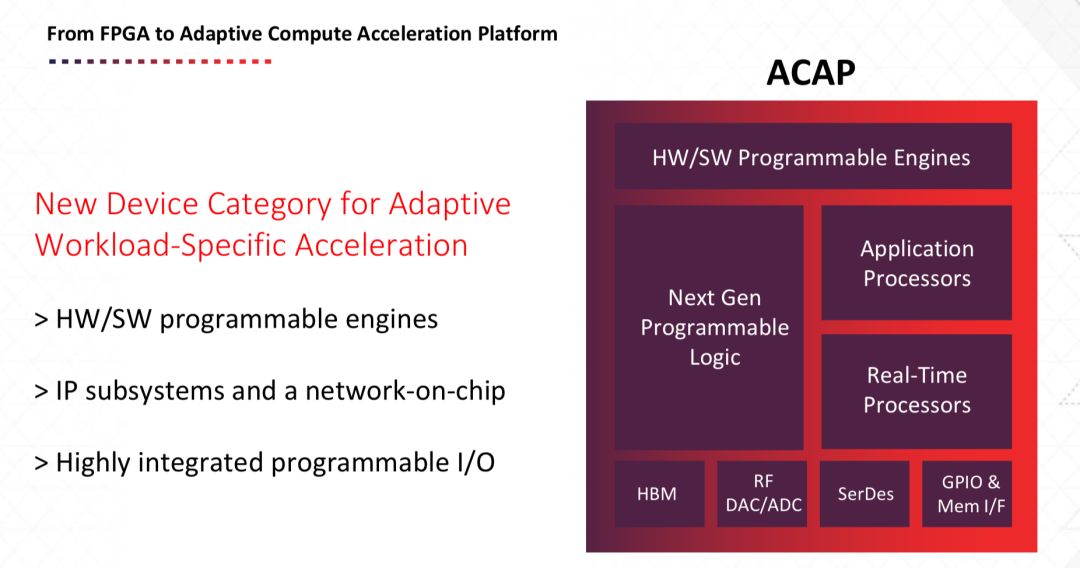

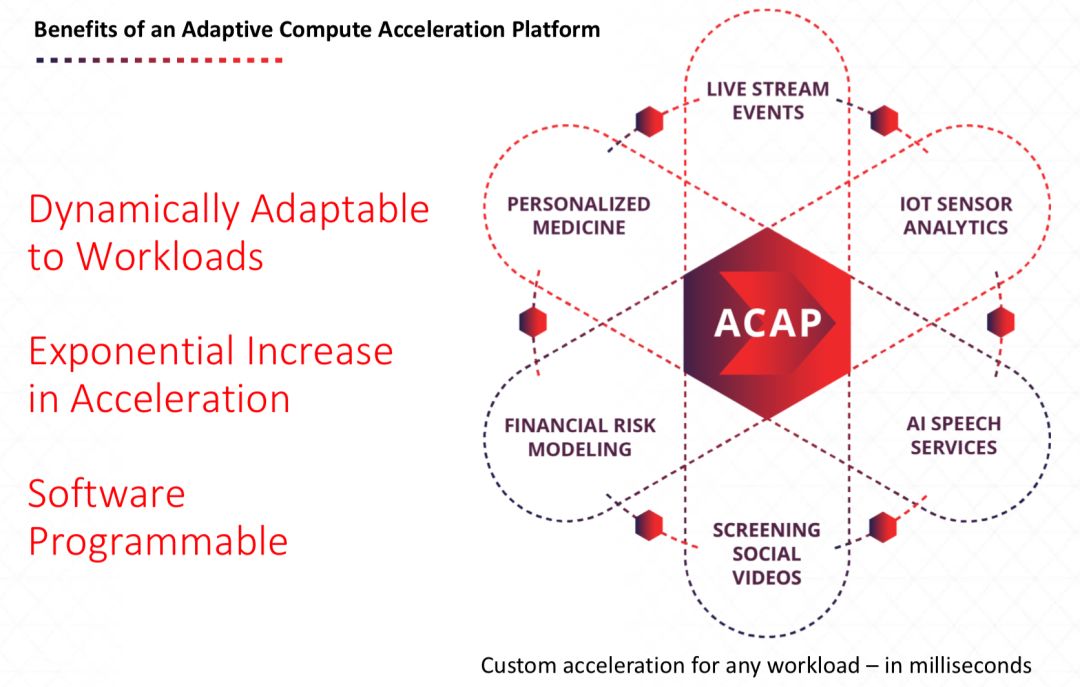

ACAP是什么?自適應計算加速平臺ACAP(Adaptive Compute Acceleration Platform),這是一款超越FPGA功能的突破性產(chǎn)品,簡稱ACAP(讀A-開普),“它是一個高度集成的多核異構計算平臺,能根據(jù)各種應用與工作負載的需求從硬件層對其進行靈活修改。ACAP 可在工作過程中進行動態(tài)調(diào)節(jié)的自適應能力,實現(xiàn)了 CPU 與 GPU 所無法企及的性能與性能功耗比。”Victor指出,“在大數(shù)據(jù)與人工智能迅速興起的時代,ACAP 理想適用于加速廣泛的應用,其中包括視頻轉(zhuǎn)碼、數(shù)據(jù)庫、數(shù)據(jù)壓縮、搜索、AI推斷、基因組學、機器視覺、計算存儲及網(wǎng)絡加速等。軟硬件開發(fā)人員將能夠針對端點、邊緣及云應用設計基于 ACAP 的產(chǎn)品。首款 ACAP 產(chǎn)品系列,將是采用臺積電 7 nm工藝技術開發(fā)的代號為“Everest(珠穆朗瑪峰)”的產(chǎn)品系列,該產(chǎn)品將于今年年底實現(xiàn)流片。 ”

這是賽靈思耗資10億美元,1500名員工四年打造的心血,最高級別有500億的晶體管!

“ACAP未來將成為一種新的主流產(chǎn)品類型,我們公司是首先推出ACAP這類產(chǎn)品的公司,我們認為未來需要這種更加靈活的能對工作負載適應性的平臺,它會變成一個主流平臺,和CPU、GPU一樣會成為非常基礎性的未來世界構建平臺。”他堅定地表示。“ACAP的推出,不僅是對業(yè)界一項重大的技術顛覆,更是我們自發(fā)明 FPGA 以來最卓著的工程成就。這款革命性的全新架構是賽靈思更廣泛市場戰(zhàn)略的一部分,將幫助公司朝著 FPGA 以外的領域發(fā)展,并突破‘僅支持硬件開發(fā)者’的局限。ACAP 產(chǎn)品在數(shù)據(jù)中心以及我們廣泛市場領域的應用,將加速自適應算技術的廣泛普及,從而讓智能、互連、自適應的世界更早成為現(xiàn)實。”

500億晶體管!ACAP 技術細節(jié)

ACAP 的核心是新一代的 FPGA 架構,結(jié)合了分布式存儲器與硬件可編程的 DSP 模塊、一個多核 SoC 以及一個或多個軟件可編程且同時又具備硬件自適應的計算引擎,并全部通過片上網(wǎng)絡(NoC)實現(xiàn)互連。ACAP還擁有高度集成的可編程I/O功能,根據(jù)不同的器件型號這些功能從集成式硬件可編程存儲器控制器,到先進的SerDes收發(fā)器技術,前沿的RF-ADC/DAC和集成式高帶寬存儲器(HBM)。

Victor表示軟件開發(fā)人員將能夠利用 C/C++、OpenCL 和 Python 等軟件工具應用ACAP系統(tǒng)。同時,ACAP也仍然能利用 FPGA 工具從RTL 級進行編程。

據(jù)透露,ACAP歷經(jīng)四年的研發(fā),累積研發(fā)投資逾 10 億美元,每顆芯片有500億晶體管!賽靈思目前有超過 1500 名軟硬件工程師參與“ACAP 和Everest”的設計。目前,軟件工具已交付給主要客戶。首款“Everest”產(chǎn)品將于 2018 年實現(xiàn)流片,于 2019 年交付給客戶。

與當今最新的 16 納米Virtex? VU9P FPGA 相比,“Everest”有望將深度神經(jīng)網(wǎng)絡的性能提升20 倍!基于“Everest”的 5G 遠程無線電頭端和目前最新的 16 納米無線電相比可將帶寬提升 4 倍。屆時,跨多個市場領域的各種應用都能實現(xiàn)性能和功耗效率的顯著提升,這些市場包括汽車、工業(yè)、科學與醫(yī)療、航空航天、測試、測量與仿真、音視頻與廣播以及消費類電子產(chǎn)品市場等。他表示賽靈思未來幾個月會陸續(xù)發(fā)布更多ACAP平臺詳細信息,如需了解更多信息,請訪問china.xilinx.com。

賽靈思三大愿景

Victor Peng 于 2008 年加入賽靈思,加入賽靈思之前,Peng 曾擔任 AMD 公司圖形產(chǎn)品部(GPG)芯片工程企業(yè)副總裁,是 AMD 核心芯片工程團隊的主要領導人,負責為圖形、游戲主機產(chǎn)品、CPU 芯片和消費者業(yè)務部門提供支持。擁有CPU、GPU和FPGA經(jīng)歷的他,更能深刻理解處理器技術未來的發(fā)展。

他表示他的治理愿景是旨在為賽靈思帶來新發(fā)展、新技術和新方向,打造“自適應的智能世界”。在該世界中,賽靈思將超越 FPGA 的局限,推出高度靈活且自適應的全新處理器及平臺產(chǎn)品系列,為用戶從端點到邊緣再到云端多種不同技術的快速創(chuàng)新提供支持。"以前我們在FPGA領域,已經(jīng)沒有競爭對手,現(xiàn)在我們進入了更高級的處理器領域,競爭對手可能是來自CPU的也可能是來自GPU的,這是一個更高級別的競爭。"他表示。這意味著英特爾、Nvidia等公司將成為賽靈思未來的競爭對手。

要適應這樣的競爭,他提出未來賽靈思三大戰(zhàn)略:

一、“數(shù)據(jù)中心加速領先”提為發(fā)展新重點

他指出賽靈思正在加強與關鍵數(shù)據(jù)中心客戶、生態(tài)系統(tǒng)合作伙伴及軟件應用開發(fā)商的合作力度,以進一步推動計算加速、計算存儲及網(wǎng)絡加速領域的創(chuàng)新與部署。數(shù)據(jù)中心是一個快速普及技術的領域,以此為重點,可以讓客戶迅速受益于賽靈思技術為各種應用所帶來的數(shù)量級提升的性能和單位功耗性能優(yōu)勢,其中包括人工智能(AI)推斷、視頻與圖像處理、基因組學等應用。

二、加速主流市場的發(fā)展

在這些主流市場中,賽靈思一直是關鍵技術的領先者而且擁有深厚的市場根基。這些市場包括八大市場領域:汽車、無線基礎設施、有線通信、音頻、視頻與廣播、航空航天、工業(yè)、科學與醫(yī)療、測試、測量與仿真以及消費類電子技術。這些主流市場與客戶仍然是賽靈思的核心,公司將繼續(xù)積極推進上述領域的創(chuàng)新。

三、驅(qū)動自適應計算,推出ACAP 平臺

Victor 指出未來的處理器平臺靈活處理負載需求,適應各種計算需求,ACAP 其實是高度集成的多核異構計算平臺,能針對各種應用與工作負載的需求,從硬件層進行更改變化。ACAP 的自適應能力可支持在工作過程中以毫秒級動態(tài)調(diào)節(jié),實現(xiàn)了 CPU 與 GPU 所無法企及的性能水平與單位功耗性能。

Peng指出:“雖然 FPGA 與 Zynq? SoC 技術仍然是我們業(yè)務的核心,但賽靈思今后將不再僅僅是一家 FPGA 企業(yè)。FPGA技術是我們的傳統(tǒng),我們在此基礎上已發(fā)展了多年,包括在可編程芯片上全面集成了 SoC,開發(fā)出了 3D IC,構建了軟件開發(fā)框架,并創(chuàng)建了合作伙伴生態(tài)系統(tǒng),為行業(yè)提供了獨一無二的產(chǎn)品。ACAP 的發(fā)明,意味著我們將上述創(chuàng)新提升到了一個新的高度,在當前以及未來我們將為數(shù)據(jù)中心與我們的主流市場創(chuàng)造更多的價值。”

自從2015年英特爾167億美元收購FPGA領域老二Altera后,賽靈思一直在不斷超越自己,從工藝從架構方面顛覆傳統(tǒng)的FPGA ,現(xiàn)在人工智能技術普及、智能化趨勢日益明顯,新一代自適應計算加速平臺ACAP也應運而生了希望ACAP帶來更多顛覆性產(chǎn)品。畢竟它的軟硬件可編程自適應計算引擎、下一代可編程邏輯單元都是很新的技術,可以適應靈活多變的處理需求。

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636303 -

晶體管

+關注

關注

78文章

10396瀏覽量

147746

原文標題:賽靈思還是賽靈思,但是FPGA已經(jīng)不是原來的FPGA了!

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發(fā)圈】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

揭秘芯片測試:如何驗證數(shù)十億個晶體管

MUN5136數(shù)字晶體管技術解析與應用指南

電壓選擇晶體管應用電路第二期

多值電場型電壓選擇晶體管結(jié)構

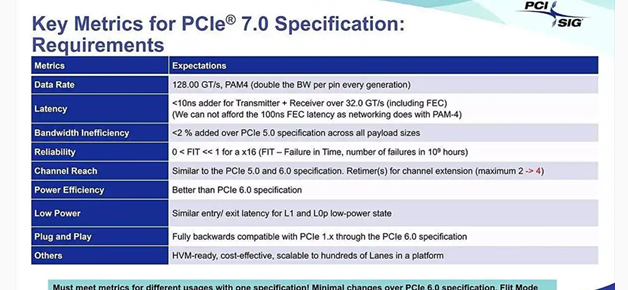

PCIe 7.0技術細節(jié)曝光

揭秘徐工新能源重卡的技術細節(jié)

下一代高速芯片晶體管解制造問題解決了!

薄膜晶體管技術架構與主流工藝路線

無結(jié)場效應晶體管詳解

500億晶體管!ACAP技術細節(jié)

500億晶體管!ACAP技術細節(jié)

評論