OpenTitan 是由 Google 主導的開源安全芯片項目,旨在為硬件系統提供 可信的硬件信任根(Root of Trust, RoT)? ,通過透明化設計和開源協作提升硬件安全水平。以下是其核心解讀:

*附件:OpenTitan Earl Grey (Discrete Chip) Datasheet.pdf

一、技術定位與核心特性

- ?開源硬件信任根

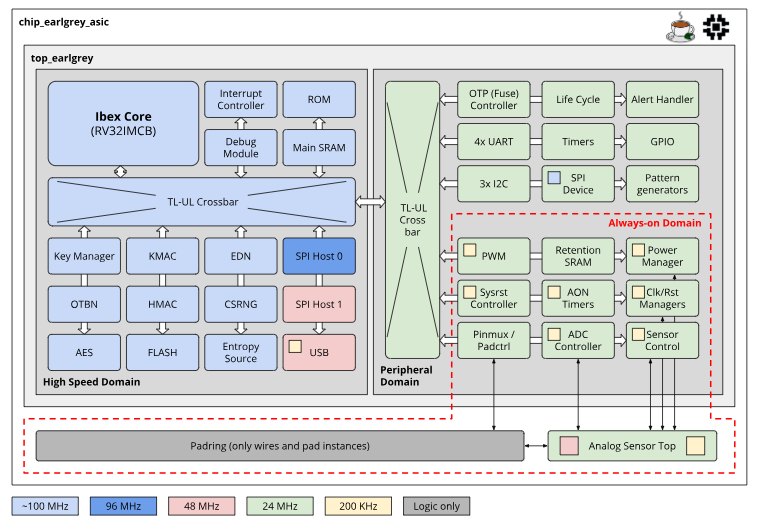

OpenTitan 的核心理念是通過開源設計實現硬件安全的透明化。其代碼、文檔和驗證流程均開放,允許開發者審查和貢獻,減少對專有設計的依賴。這種透明性被認為是抵御硬件攻擊的關鍵,例如供應鏈攻擊或固件篡改。 - ?基于 RISC-V 架構

項目采用 RISC-V 開源指令集,具備高度可擴展性和靈活性,支持定制化安全模塊(如加密協處理器、物理隨機數生成器等)。這一架構選擇降低了廠商鎖定風險,同時適配多種應用場景(如服務器、物聯網、消費電子)。 - ?模塊化與安全強化

二、應用場景與生態進展

- ?核心應用領域

- ?商業化落地

- ? 新唐科技合作 :2025 年推出的首款量產芯片將用于 Google Chromebook,提供可信啟動和硬件級密鑰保護。

- ? 生態合作伙伴 :Western Digital、Seagate 等企業參與硬件設計,lowRISC 組織負責項目運營,形成開源社區與商業實體的協同。

三、挑戰與未來趨勢

- ?技術局限性

- 當前版本主要聚焦 BIOS 防護,對 BMC(帶外管理)和 Boot Loader 的覆蓋有限,需進一步擴展驗證范圍。

- 開源模式可能導致企業擔心知識產權泄露,影響廠商參與度。

- ?與 AI 的融合潛力

盡管 OpenTitan 目前未明確集成 AI 加速功能,但其模塊化設計為未來整合 AI 安全模塊(如異常行為檢測算法)提供了可能。例如,通過機器學習實時分析硬件操作日志,可增強對零日攻擊的防御能力。

四、總結

OpenTitan 代表了硬件安全領域的范式轉變:? 通過開源協作打破傳統黑盒設計,以透明性構建信任基礎 。其 RISC-V 架構和模塊化特性使其在服務器、物聯網等場景中具備廣泛適用性,而商業化進展(如 Chromebook 集成)則驗證了開源模式的可行性。未來,隨著 AI 安全需求的增長,OpenTitan 可能進一步演變為“安全 AI SoC”的基礎平臺,融合硬件加密與智能威脅防護能力。

參考

Introduction to OpenTitan

OpenTitan is an open source secure silicon ecosystem producing both silicon IP and complete top-level designs capable of supporting numerous applications, including a discrete secure micro-controller and an integrated secure execution environment (both supporting Root of Trust functionality with secure boot and DICE attestation). OpenTitan will make design and implementation of secure silicon more transparent, trustworthy, and secure for enterprises, platforms, and chip manufacturers. OpenTitan is administered by lowRISC CIC as a collaborative, partner-centric project to produce high quality, open IP for instantiation as a full-featured product. This repository exists to enable collaboration across participating OpenTitan project partners and the broader open silicon community.

Getting Started

Start at the Getting Started page to begin your OpenTitan journey. Other helpful OpenTitan resources include the contribution and the tools guides. The Hardware book also contains useful technical documentation on the SoC, our RISC-V Ibex processor core, and the individual IP blocks. For questions about how project organization and governance, see the project landing spot.

Understanding OpenTitan

Datasheets

- OpenTitan Earl Grey (Standalone Chip) Datasheet

- OpenTitan Darjeeling (Integrated Admissible Architecture) Datasheet

Documentation

Development

發布評論請先 登錄

開源鴻蒙與RISC-V深度融合構建萬物智聯新底座

鷺島育芯 開源致遠 | 2026 RISC-V芯片設計與應用大賽頒獎典禮圓滿舉行

RISC-V vs ARM:為什么工業與邊緣計算仍然選擇 ARM 架構?

直播預約 |開源芯片系列講座第30期:“一生一芯”計劃——從零開始設計自己的RISC-V處理器芯片

深圳:“開源鴻蒙+RISC-V” 生態建設全面提速

開源鴻蒙RISC-V SIG線下技術融合交流會圓滿收官

進迭播客 |「RISC-V 圓桌白話錄」首期正式上線!

明晚開播 |開源芯片系列講座第29期:RISC-V AI芯片的創新和應用

明晚開播 |開源芯片系列講座第28期:高性能RISC-V微處理器芯片

芯新聞|昊芯亮相第五屆RISC-V中國峰會,共繪開源芯片新紀元

RISC-V 手冊

直播預約 |開源芯片系列講座第28期:高性能RISC-V微處理器芯片

RISC V 開源芯片項目:OpenTitan 詳細解讀

RISC V 開源芯片項目:OpenTitan 詳細解讀

評論