在30多年的半導(dǎo)體制造歷史上,最大的一個挑戰(zhàn)就是跟上1965年摩爾做出的預(yù)測,即集成電路中的晶體管數(shù)目每兩年翻一番。

為了實現(xiàn)這個目的,IC尺寸越來越大,而特征尺寸越來越小。有兩個方法來減小特征尺寸,一是減小用來刻印特征到晶圓的激光器波長,一是調(diào)整成像設(shè)備的數(shù)值孔徑,使得晶圓上的成像更加清晰。

但是當(dāng)特征尺寸低于光源波長時,從248nm的光刻工具開始情況有了改變。當(dāng)尺寸小于激光波長時,圖像開始失真,難于光刻。另外,有時臨近圖像還會變形。

而更小波長的研發(fā)卻停滯于193nm,很多人在研究超紫外線(EUV)試圖擴展193nm光刻的能力。目前,EUV離就緒還有5到15年的時間。

事實上,由于成本,EUV可能永遠(yuǎn)不會就緒。光刻的所有決定最終都?xì)w結(jié)到成本,業(yè)界還沒法在適當(dāng)?shù)某杀鞠峦瞥鲞@樣的精度。

除了波長,關(guān)于精度的另一個因素就是光刻工具的數(shù)值孔徑(NA)。一個通用的提高NA的方法是利用水來做浸液式光刻。

從光刻的角度看設(shè)計的難度,光刻師將特征尺寸代入一個公式:波長/NA=k1,此處k1是比例后的精度,也是光刻難易程度的一個表征。k1越大,光刻就越容易,k1越小,光刻就越難。浸液式光刻可以可以使NA大于1,但是還是會碰到困難,所以提高精度必須采用低k1的方式。

設(shè)計過程中低的k1就代表光刻越難,光刻對一些設(shè)計細(xì)節(jié)變得越來越敏感,所以在設(shè)計時必須制定很多限制條件,而現(xiàn)在的設(shè)計規(guī)則變得很復(fù)雜和繁復(fù),設(shè)計者想要得到一個完美結(jié)果很困難。

最近幾年的設(shè)計都會很受限,因為激光波長的減低在未來3到4年不會發(fā)生,采用浸液式光刻來提高數(shù)值孔徑也已經(jīng)很充分了,所以接下來幾年都會繼續(xù)使用193nm。想要降低特征尺寸,只能折衷設(shè)計。

同時,設(shè)計規(guī)則也很脆弱,它們對設(shè)計者來講變得不再易于配置和遵循,所以在過去的5年里規(guī)則表很明顯沒有完全被依照。

那么該怎么辦呢?要保證光刻師建立一個良好的設(shè)計規(guī)則表。并不一定要設(shè)計師成為光刻專家,也不一定要光刻師成為設(shè)計專家,但是主要的工作方向還是要健全光刻仿真,光刻師將他們的所知放入工具,而設(shè)計師可以利用這些數(shù)據(jù),以此來分析光刻的難易程度。

建立這樣的工具時最大的問題是工序問題。設(shè)計者需要在光刻制程確定制程節(jié)點前就布局標(biāo)準(zhǔn)單元,確定布局布線工具。比如你在用3年前TSMC提供的制程做設(shè)計,對于32nm,你必須在光刻到位前就開始設(shè)計,但是光刻制程能否在兩年內(nèi)到位是個問題,這個問題就會在生產(chǎn)開始前影響到設(shè)計流程。

事實上,隨著45nm制程的推出,代工廠對于塊cmos制程開始推薦限制性設(shè)計工具(RDR),要求采用先進的低功耗設(shè)計技術(shù)和設(shè)計為生產(chǎn)(DFM:design-for-manufacturing)工具,一些代工廠還推薦設(shè)計者采用概率分析工具,比如統(tǒng)計靜態(tài)時序分析和統(tǒng)計功耗分析等來減低時序和功耗問題。

很明顯,RDR的日子已經(jīng)來到。

對于仿真技術(shù)也有一些問題要解決:你如何確保你仿真的是正確的東西?你如何確保輸入?yún)?shù)就是你想要仿真的參數(shù)?對于光刻仿真OPC的供應(yīng)商來講,挑戰(zhàn)在于如何利用光刻信息,它們是仿真成功的源泉。

在研究光刻對IC設(shè)計影響的原因以及繼續(xù)縮減晶體管特征尺寸時,工程師或者降低光刻采用的激光器的波長或者增加成像工具的數(shù)值孔徑。如本文的第一部分所述。

因此,半導(dǎo)體制造商不斷減小激光的波長,從1980年的436nm到2001年直至目前的193nm。但是在248nm時,隨著圖形(patterning)開始低于光源的波長,這引起圖像失真和其它一些相關(guān)問題。

但是,波長的縮短停留在了193nm,雖然已經(jīng)有很多關(guān)于EUV光刻的研究想要來擴展目前的技術(shù),但是據(jù)估計EUV在未來5到15年還不會就緒。

第二個提高特征尺寸可刻性的方法是增加光刻成像工具的數(shù)值孔徑以及采用浸液式光刻。

第三個縮減特征尺寸的方法是目前半導(dǎo)體制造采用的兩次圖形曝光。這個方法雖然可以縮減尺寸,但是需要兩次通過掃描器,將一個圖形對半分為兩個掩模。

兩次圖形曝光是可以有效倍增光刻間距的精度提高技術(shù)(RET),它被認(rèn)為是在當(dāng)前工具情況下將193nm浸液式光刻應(yīng)用于32nm制程節(jié)點的主要方法,也是未來走向

EUV光刻技術(shù)的橋梁。

但是兩次圖形曝光有層疊限制,當(dāng)將掩模對分時會有OPC問題,這會使得某些特征實現(xiàn)很困難。雖然有這些挑戰(zhàn),但是刻印的瓶頸對于圖形來講并不存在。因為兩次曝光包含兩次蝕刻,所以有一部分難度轉(zhuǎn)移到了蝕刻和薄膜上。

因此,設(shè)計者、EDA公司、scanner供應(yīng)商、芯片制造商以及設(shè)備提供商需要多方展開合作,通過EDA公司和設(shè)備提供商的合作,光刻仿真就被看作是解決從設(shè)計到制造問題的一個解決方法。EDA公司不僅僅只關(guān)注設(shè)計,還要考慮后期流片的問題。

關(guān)鍵問題是如何使得EDA工具完全明白制造的問題。各種工具的融合從65nm開始,還將隨著分析和合并的需要一直到32nm流程。

隨著光刻仿真的挑戰(zhàn),兩次圖形曝光對半導(dǎo)體行業(yè)設(shè)計方面的影響還不清楚,有些會比較明顯,比如層的分解。目前已經(jīng)有6層的兩次圖形曝光制程。明年預(yù)計這個問題會更加清晰一些。

另一個影響現(xiàn)今設(shè)計的問題是光刻引起的電子偏差現(xiàn)象以及與壓力相關(guān)的系統(tǒng)缺陷。在設(shè)計方法學(xué)中這些數(shù)據(jù)如何應(yīng)用以及對時序的影響都還是問題。

另外,光刻引起的電子問題如何到時序和功率泄漏中也正在研究。Cadence和合作伙伴的研究表明如果直接將65nm設(shè)計技術(shù)移植到45nm,20%的時序關(guān)閉,泄漏偏差增加了300%。這不再單單是EDA的問題,設(shè)計師需要利用制造的數(shù)據(jù)以便于更好地設(shè)計芯片。

對于45nm以及更小的16nm,諸如基于模型的化學(xué)物質(zhì)平面化(CMP)等問題需要找到新的方案。應(yīng)力問題也需要被關(guān)注。對于P或者N溝道器件應(yīng)力對參數(shù)的影響很明顯。

Synopsys對此在開發(fā)一個叫“虛擬制造環(huán)境”,它采用了光刻仿真技術(shù)并集成了對最終圖形定義的蝕刻。這個環(huán)境考慮到了熱制程、移植等問題,它不僅僅是光刻的仿真,還力圖將仿真反饋到方法學(xué)中。Synopsys認(rèn)為從制造反饋到設(shè)計的消息越多,一個設(shè)計的穩(wěn)健程度就越大。

總之,業(yè)界為了趕上摩爾定律的預(yù)測而不斷開發(fā)新技術(shù),這使得以前很少合作的人們走到了一起。

-

IC設(shè)計

+關(guān)注

關(guān)注

38文章

1373瀏覽量

108309 -

工程師

+關(guān)注

關(guān)注

59文章

1603瀏覽量

71031 -

光刻

+關(guān)注

關(guān)注

8文章

364瀏覽量

31339

發(fā)布評論請先 登錄

什么是BSP工程師

電子工程師設(shè)計相關(guān)要點與案例分析

想成為硬件工程師?我教你啊!你得先學(xué)會這些...... #硬件工程師 #電子工程師 #電子愛好者 #電子行業(yè)

硬件工程師看了只會找個角落默默哭泣#硬件工程師 #MDD #MDD辰達(dá)半導(dǎo)體 #產(chǎn)品經(jīng)理 #軟件工程師

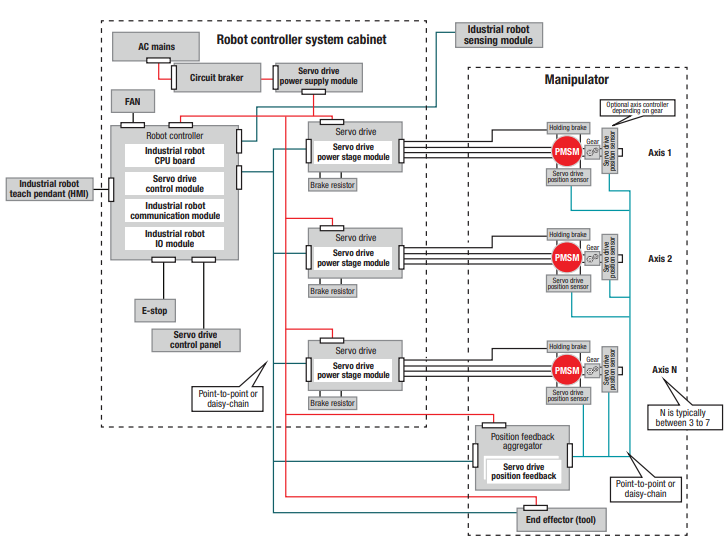

工業(yè)機器人設(shè)計工程師必備指南免費下載

IC設(shè)計工程師必須要知道光刻的原因

IC設(shè)計工程師必須要知道光刻的原因

評論