在當(dāng)今科技飛速發(fā)展的時(shí)代,高效能運(yùn)算(High-Performance Computing, HPC)正以其強(qiáng)大的計(jì)算能力,不斷突破各個(gè)領(lǐng)域的界限。HPC通過使用由成千上萬個(gè)處理器核心組成的超級(jí)計(jì)算機(jī)或計(jì)算機(jī)集群,執(zhí)行復(fù)雜的計(jì)算任務(wù),這些任務(wù)通常涉及大量的數(shù)據(jù)輸入,必須具備大量算力和高速數(shù)據(jù)處理能力。USI環(huán)旭電子在這一波市場(chǎng)角逐中,瞄準(zhǔn)AI領(lǐng)域的高度運(yùn)用,以我們自身的強(qiáng)項(xiàng)「3D封裝技術(shù)」切入市場(chǎng),應(yīng)用在多項(xiàng)HPC模組中。接下來,本文將從HPC的簡(jiǎn)介、挑戰(zhàn)與創(chuàng)新等方面,從正反兩面探討開發(fā)HPC最被重視的議題。

高效能運(yùn)算 (HPC) 簡(jiǎn)介

HPC是利用超級(jí)計(jì)算機(jī)實(shí)現(xiàn)并行計(jì)算的理論、方法、技術(shù)以及應(yīng)用的一門技術(shù)科學(xué)。處理器、內(nèi)存和存儲(chǔ)技術(shù)的不斷創(chuàng)新,為HPC系統(tǒng)提供了強(qiáng)大的計(jì)算資源。現(xiàn)代處理器采用多核設(shè)計(jì),具備更高的并行處理能力。內(nèi)存和存儲(chǔ)技術(shù)也在不斷進(jìn)步,如DDR5內(nèi)存、PCIe 4.0存儲(chǔ)等,提供了更高的數(shù)據(jù)傳輸速度和更大的容量,滿足HPC系統(tǒng)對(duì)高帶寬和低延遲的需求。

HPC的應(yīng)用領(lǐng)域廣泛,涵蓋科學(xué)研究、天氣預(yù)報(bào)、模擬等多個(gè)方面。它的多樣化應(yīng)用,使得各個(gè)領(lǐng)域都能夠受益于其強(qiáng)大的計(jì)算能力。然而,盡管取得了顯著的進(jìn)步,但在設(shè)計(jì)和部署HPC系統(tǒng)時(shí)仍面臨諸多挑戰(zhàn)。

高效能運(yùn)算 (HPC) 的供電挑戰(zhàn)

高效能運(yùn)算系統(tǒng)正面臨著功耗和散熱兩大嚴(yán)峻挑戰(zhàn)。這些系統(tǒng)通常由數(shù)量龐大的處理器組成,每個(gè)處理器都消耗大量電力,這使得降低能量耗損成為首要任務(wù)。傳統(tǒng)上,為了降低能量耗損,系統(tǒng)會(huì)采用高電壓供電,然后在微處理器前進(jìn)行多階段轉(zhuǎn)換為較低的電壓。這個(gè)過程中,從DC-DC轉(zhuǎn)換器到微處理器的路徑布線耗損扮演著關(guān)鍵角色。這些轉(zhuǎn)換器負(fù)責(zé)將12V或48V的直流總線電壓降低到處理器核心所需的特定電壓,同時(shí)將電流提升到所需的水平。

多階供電網(wǎng)路 (PDN) 的損耗與影響

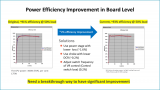

即使穩(wěn)壓器只需向晶片短距離供電,多階供電網(wǎng)路(PDN)仍然會(huì)因?yàn)?a target="_blank">電源軌上的電阻而產(chǎn)生損耗(I2R),進(jìn)而導(dǎo)致散熱問題。這些損耗也包括電感和電容造成的影響。因此,供電設(shè)計(jì)中最重要的因素之一是穩(wěn)壓器在PCB上的位置,這直接影響到饋入處理器引腳的電源軌上的電阻大小。

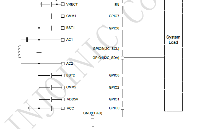

為了盡可能靠近負(fù)載點(diǎn)(POL)來減少電阻,垂直整合的電壓調(diào)節(jié)模組(VRM)成為了當(dāng)前熱門的解決方案。這種模組將負(fù)責(zé)電壓轉(zhuǎn)換的功率級(jí)、管理模組中電流和熱量的磁性元件,以及在電源進(jìn)入處理器前調(diào)節(jié)電源的電容器整合在同一個(gè)模組中。這意味著VRM可以放置在物理上更靠近POL的位置,從而有效地減少電流損失和功率損耗。

電壓調(diào)節(jié)模組 (VRM) & 垂直電源傳輸 (VPD)

穩(wěn)壓器模組(VRM)主要由三個(gè)部分組成:電容器、電感器和功率級(jí)。例如,雙相功率模組,則是將多相降壓穩(wěn)壓器的兩個(gè)相位的元件整合到一個(gè)基板上,形成一個(gè)單一裝置,并以陣列方式部署,構(gòu)成一個(gè)多相系統(tǒng)。隨著AI加速器在效能和功率需求上不斷提升,功率級(jí)的數(shù)量可能會(huì)進(jìn)一步增加。

除了元件整合和效能提升,為AI加速器供電的新趨勢(shì)是垂直供電,也稱為背面供電。垂直電源傳輸(VPD)技術(shù)將電源穩(wěn)壓器直接移到PCB背面處理器的下方。透過較短的垂直路徑傳輸電源,VPD可以大幅降低PDN(電源傳輸網(wǎng)路)的電阻并減少損耗,從而在較高電流和較低處理器核心電壓下達(dá)到更高的電源效率。此外,由于VPD消除了PCB上的空間占用,AI處理器設(shè)計(jì)人員可以增加記憶體和I/O線路,從而進(jìn)一步提升處理效能。

承上兩大解決方案,各有優(yōu)劣之處,因此,運(yùn)用最適合客戶需求的解決方案才是優(yōu)先考量。如何設(shè)計(jì)和部署高效能運(yùn)算系統(tǒng),以及如何有效地管理和優(yōu)化功耗、散熱和資源,是成就高效算力系統(tǒng)的必經(jīng)之路。

-

封裝技術(shù)

+關(guān)注

關(guān)注

12文章

599瀏覽量

69261 -

HPC

+關(guān)注

關(guān)注

0文章

344瀏覽量

24922 -

環(huán)旭電子

+關(guān)注

關(guān)注

0文章

75瀏覽量

3972

原文標(biāo)題:突破性能瓶頸:高效能運(yùn)算系統(tǒng)的雙重挑戰(zhàn)

文章出處:【微信號(hào):環(huán)旭電子 USI,微信公眾號(hào):環(huán)旭電子 USI】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

高效能運(yùn)算放大器LT1804的深度解析

探索MAX9613:低功耗、高效能的單/雙路軌到軌I/O運(yùn)算放大器

高效能運(yùn)算放大器LTC6262的深度剖析

環(huán)旭電子旗下環(huán)興光電取得光創(chuàng)聯(lián)科技控制權(quán)

五大無人機(jī)高效能動(dòng)力推進(jìn)系統(tǒng)軟件已融合AI模型

無人機(jī)高效能動(dòng)力推進(jìn)系統(tǒng):功能特點(diǎn)與平臺(tái)架構(gòu)解析

環(huán)旭電子模組化與微小化制程技術(shù)如何突破AI能源高墻

環(huán)旭電子借助NVIDIA Omniverse與RTX GPU構(gòu)建工廠級(jí)數(shù)字孿生系統(tǒng)

環(huán)旭電子即將推出新一代1.6T光模組產(chǎn)品

SL4013 耐壓2.7V-25V輸入升壓芯片 替換MP3212 高效能便攜電源方案

環(huán)旭電子成功交付Level 10等級(jí)JDM項(xiàng)目

SQ76115BADE同步降壓DC/DC轉(zhuǎn)換器:高效能、寬輸入電壓解決方案

環(huán)旭電子亮相第十七屆國(guó)際汽車動(dòng)力系統(tǒng)技術(shù)年會(huì)

環(huán)旭電子助力客戶發(fā)布高性能自行車計(jì)算機(jī)

ip6832原理圖文檔:無線充電技術(shù)的高效能革命

環(huán)旭電子如何解決高效能運(yùn)算系統(tǒng)挑戰(zhàn)

環(huán)旭電子如何解決高效能運(yùn)算系統(tǒng)挑戰(zhàn)

評(píng)論