I2C協議因其簡單性和靈活性而被廣泛應用于嵌入式系統設計中。它允許多個設備共享同一總線,從而減少了所需的引腳數量,簡化了系統設計。

1. I2C總線結構

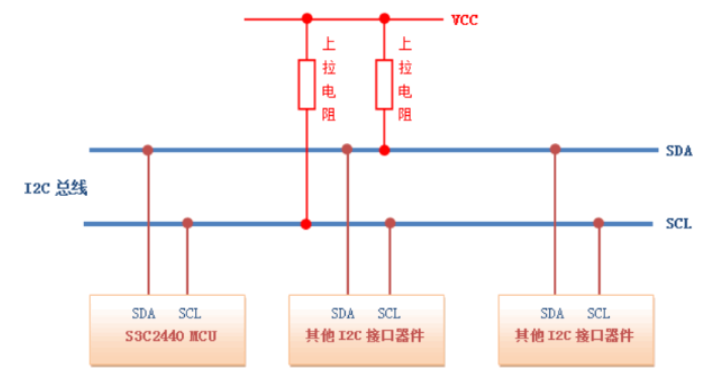

I2C總線由兩條線組成:數據線(SDA)和時鐘線(SCL)。SDA負責傳輸數據,而SCL用于同步數據傳輸。總線上的所有設備都通過這兩條線連接。

- SDA(數據線) :雙向數據線,用于傳輸數據。

- SCL(時鐘線) :雙向時鐘線,用于同步數據傳輸。

2. 引腳配置

在設計I2C硬件時,需要考慮以下引腳配置:

- 上拉電阻 :SDA和SCL線需要外部上拉電阻,以確保在空閑時保持高電平狀態。通常,上拉電阻的值在1kΩ到10kΩ之間。

- 總線電容 :為了減少噪聲和信號反射,總線上可以添加電容。一般推薦在SDA和SCL線上各添加一個0.1μF的電容。

- 總線長度 :I2C總線的最大長度取決于數據速率和設備數量。高速模式下,總線長度應盡量短,以減少信號衰減和時延。

3. 時序要求

I2C協議的時序要求非常嚴格,以下是一些關鍵的時序參數:

- 時鐘同步 :SCL線由主設備控制,用于同步數據傳輸。

- 數據穩定時間 :在SCL線上升沿之前,SDA線上的數據必須穩定。

- 數據保持時間 :在SCL線下降沿之后,SDA線上的數據必須保持穩定。

- 起始條件 :由SDA線從高電平變為低電平,同時SCL線保持高電平觸發。

- 停止條件 :由SDA線從低電平變為高電平,同時SCL線保持高電平觸發。

4. 設計注意事項

在設計I2C硬件時,需要注意以下幾點:

- 總線仲裁 :在多主機系統中,需要實現總線仲裁機制,以解決多個主機同時控制總線的問題。

- 地址沖突 :確保系統中沒有兩個設備使用相同的地址。

- 信號完整性 :使用適當的布線技術和屏蔽措施,以確保信號完整性。

- 電源管理 :合理設計電源電路,確保I2C總線在不同工作狀態下都能穩定工作。

5. 常見問題及解決方案

在I2C硬件設計中,可能會遇到以下常見問題及其解決方案:

- 信號干擾 :使用屏蔽電纜和適當的布線技術,減少信號干擾。

- 總線沖突 :實現總線仲裁機制,避免多個設備同時訪問總線。

- 設備不響應 :檢查設備的地址是否正確,以及是否正確配置了上拉電阻和電容。

- 數據傳輸錯誤 :檢查時序要求是否滿足,以及是否有硬件故障。

6. 結論

I2C協議的硬件設計需要考慮總線結構、引腳配置、時序要求等多個方面。通過遵循上述設計指南,可以確保I2C總線的穩定運行和數據傳輸的可靠性。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

嵌入式系統

+關注

關注

41文章

3747瀏覽量

133618 -

硬件

+關注

關注

11文章

3594瀏覽量

69005 -

數據線

+關注

關注

8文章

315瀏覽量

54186 -

IIC協議

+關注

關注

0文章

31瀏覽量

4242

發布評論請先 登錄

相關推薦

熱點推薦

AT32硬件除法器應用指南

AT32硬件除法器應用指南

AT32F011 提供了 32 位硬件除法器,并且可以執行無符號及有符號運算,本應用指南將介紹基礎概念及實際案例。

支持型號: AT32F011 系列

1

發表于 01-30 13:49

【瑞薩RA × Zephyr開發板評測】+模擬IIC實現OLED輸出(與硬件IIC輸出的失敗經驗)

無需額外工具即可編寫/調試程序。此外,通過Arduino Uno和Pmod?接口,包括對微控制器所有引腳的標準和通孔訪問等,它具有很高的可擴展性。

按照上圖進行Oled接線,首先使用IIC硬件接口

發表于 01-19 22:23

RA MCU眾測寶典 | IIC之【RA2E1】IIC通信的OLED顯示

“RAMCU眾測寶典”IIC專題上線啦!這次,瑞薩嵌入式小百科將和大家一起聚焦【瑞薩RA2E1】開發板,一步步玩轉IIC通信的OLED顯示。從IIC協議的核心原理、FSP中I2CMas

通信協議IIC與SPI最全對比分析

現今,在低端數字通信應用領域,我們隨處可見IIC(Inter-Integrated Circuit)和 SPI(Serial Peripheral Interface)的身影。原因是這兩種通信協議

發表于 12-10 06:04

基于hbirdv2-sdk的iic 0.96寸lcd調試

一.前言

簡介: 基于hbird-sdk的硬件IIC控制 0.96寸lcd.

二.工程結構

硬件: mcu200t fpga開發板

軟件結構: 主要由Makefile main.c

發表于 10-30 06:20

如何驗證硬件加速是否真正提升了通信協議的安全性?

驗證硬件加速是否真正提升通信協議的安全性,需從 安全功能正確性、抗攻擊能力增強、安全性能適配、合規一致性 等核心維度展開,結合實驗室測試與真實場景驗證,避免 “硬件參與即安全提升” 的表面判斷。以下

有哪些方法可以確保硬件加速與通信協議的兼容性?

? 確保硬件加速與通信協議的兼容性,核心是從 硬件選型、協議標準匹配、軟硬件接口適配、全場景測試驗證 四個維度建立閉環,避免因

【微五科技CF5010RBT60開發板試用體驗】硬件IIC點亮OLED小屏幕

傳輸效率高,整體功耗比軟件模擬方案更低。

長時間 (數小時) 滿負荷刷新測試,顯示穩定,無花屏、亂碼、死機現象,IIC 總線通信穩定可靠。

得益于硬件 IIC 內置的協議處理和錯誤檢測

發表于 08-08 11:01

STM32F407的兩個USB口能否分別實現讀卡器和讀U盤的功能以及硬件IIC讀寫AT24C02?

需求如下:

1.OTS_FS(PA 11,PA12)實現TF卡的讀卡器功能,

2.OTS_HS(PB14,PB15)實現讀寫U盤功能

3.硬件IIC(PB8,PB9)讀寫AT24C02,硬件I

發表于 03-11 06:23

iic協議的硬件設計指南

iic協議的硬件設計指南

評論