本文主要介紹FinFet Process Flow—啞柵極的形成。

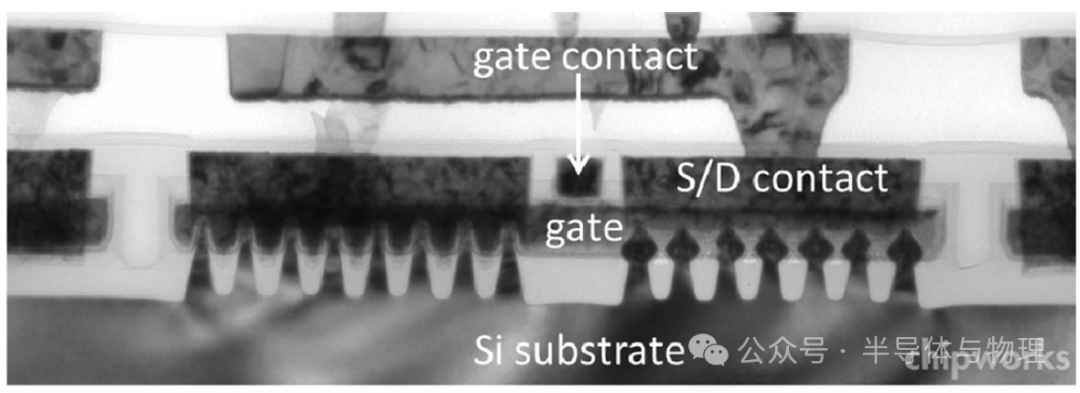

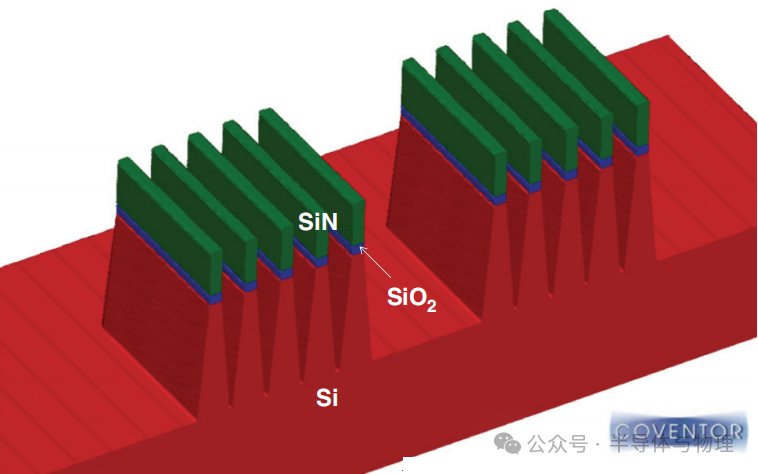

鰭片(Fin)的形成及其重要性

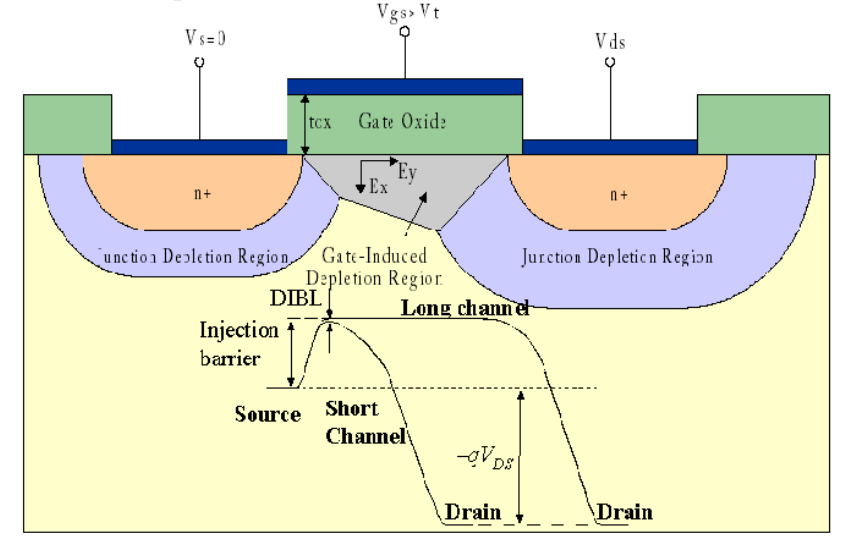

鰭片是FinFET器件三維結構的關鍵組成部分,它類似于魚鰭的形狀,因此得名。鰭片的高度直接決定了FinFET的柵極寬度,這對于控制電流流動至關重要。在22nm及以下技術節點中,由于鰭片尺寸非常小,通常通過SADP(Self-Aligned Double Patterning)或SAQP(Self-Aligned Quadruple Patterning)等圖案化技術來實現。

初步處理與ILD層沉積

ILD層沉積

隨后,在清潔后的晶圓上沉積一層ILD(Inter Layer Dielectric)一般使用SiO2 Coat。ILD的主要作用是在鰭片之間提供電氣隔離,并作為后續CMP(化學機械拋光)過程中的填充材料。選擇適當的ILD材料對于確保良好的電學性能和平坦度非常重要。

ILD CMP

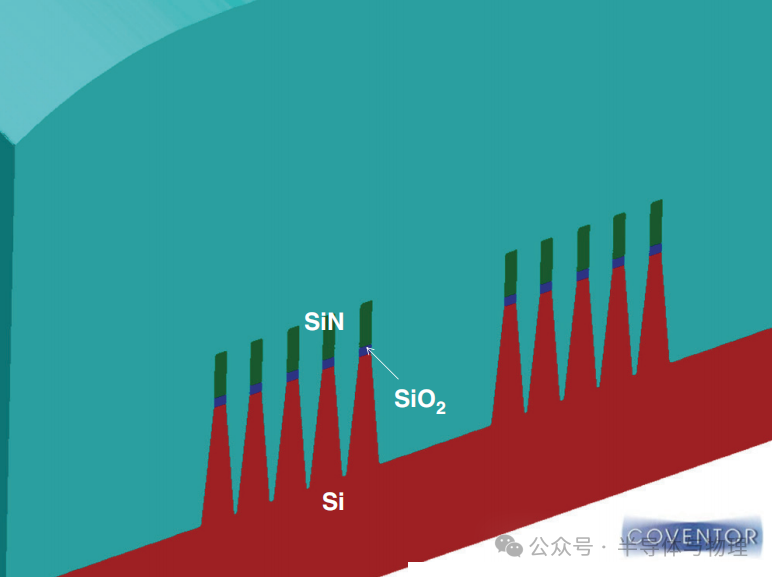

接下來進行的是ILD CMP,即使用氮化硅(SiN)作為終點檢測材料來進行化學機械拋光。CMP的目標是使ILD層表面變得非常平坦,以便于后續的圖案化和蝕刻操作。CMP過程中必須精確控制拋光量,以避免過度侵蝕下面的關鍵結構。

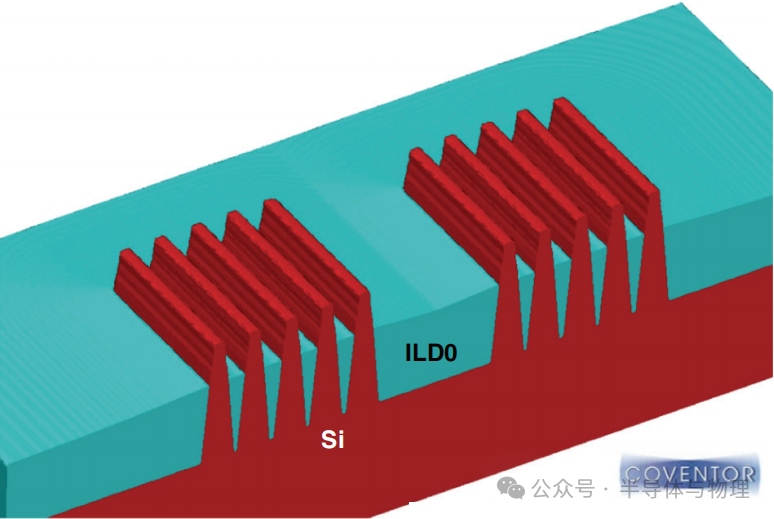

移除SiN和墊氧化層

CMP完成后,需要移除覆蓋在鰭片上的氮化硅硬掩膜以及墊氧化層。這個步驟通常通過濕法蝕刻完成,它不僅清除了這些臨時保護層,還暴露出鰭片頂部的硅表面,為后續的摻雜做準備。

犧牲氧化層生長與阱區摻雜

犧牲氧化層生長

緊接著,在鰭片表面生長一層薄的犧牲氧化層。該層用于后續的阱區摻雜過程中保護鰭片免受直接損傷。此外,犧牲氧化層還可以幫助定義摻雜區域的邊界,提高摻雜精度。

阱區摻雜

應用一個阱區植入掩模,并執行離子注入以形成通道和基板之間的隔離阱。這個步驟是為了創建p型或n型阱區,從而為PMOS和NMOS器件分別提供適當的背景摻雜。之后,移除犧牲氧化層并清洗晶圓,確保沒有殘留物影響后續工藝。

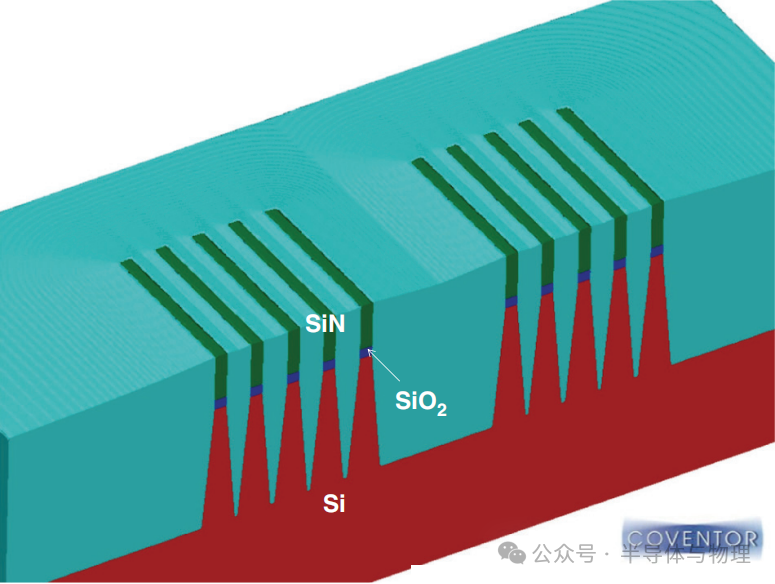

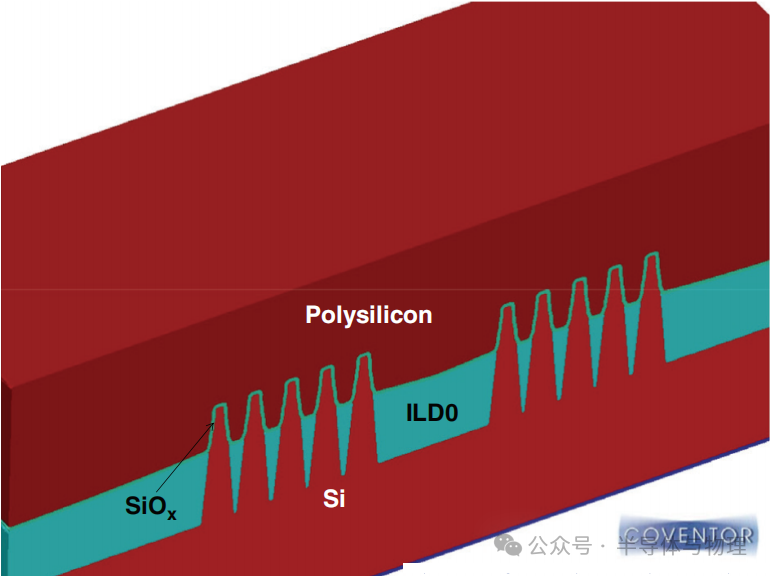

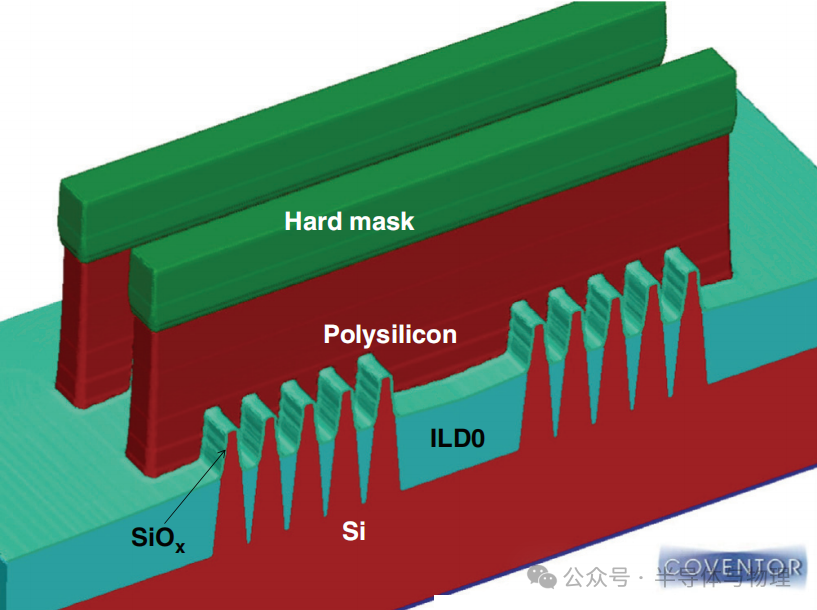

啞柵極結構形成

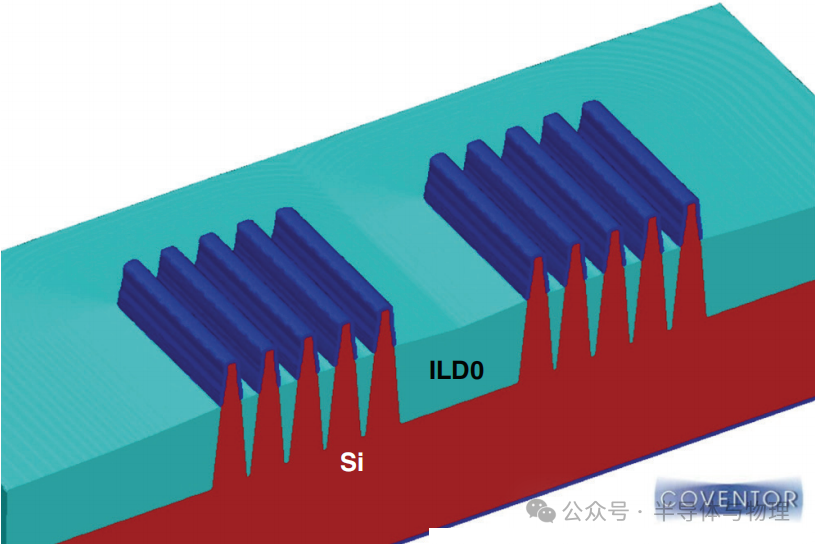

啞柵極氧化層沉積

為了構建臨時的柵極結構,先在晶圓上沉積一層啞柵極氧化層。這層氧化物將作為后續多晶硅沉積和平坦化的基礎。

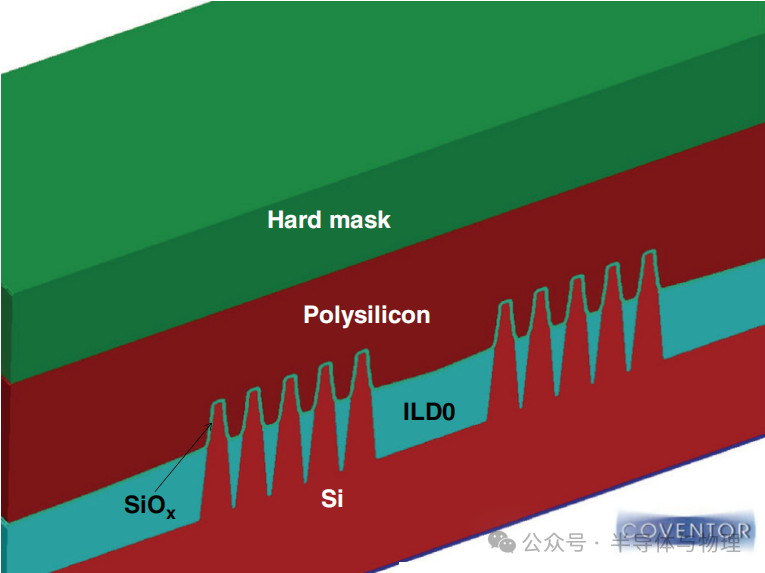

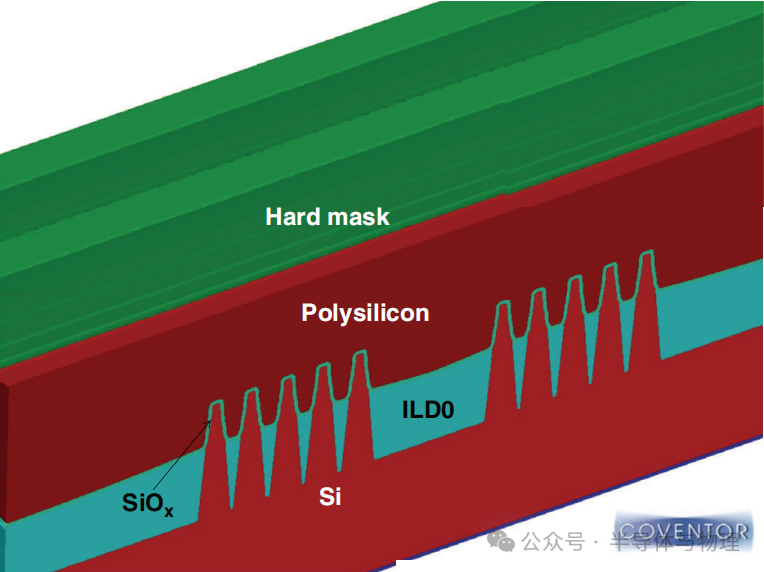

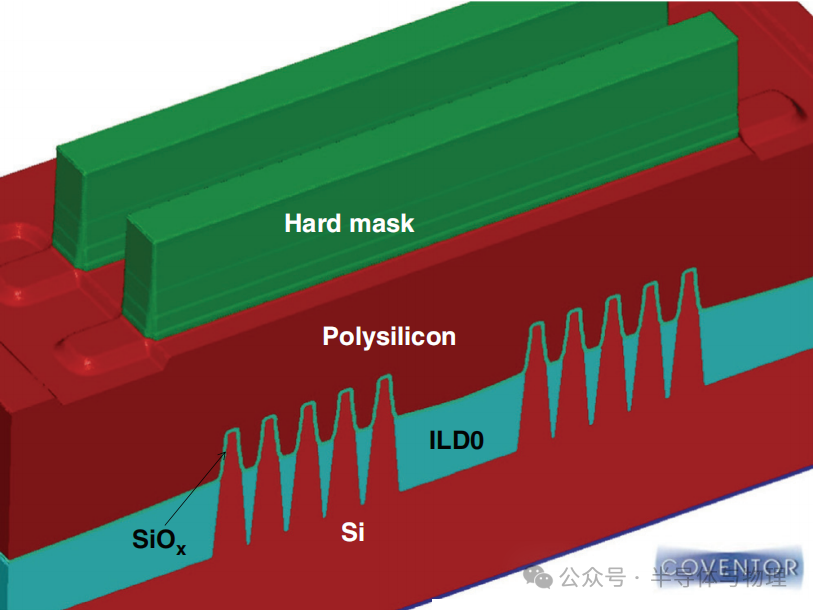

多晶硅沉積與CMP

然后,在整個晶圓表面沉積一層多晶硅,并通過CMP使其平坦化。多晶硅層將充當臨時柵極材料,直到最終的高k金屬柵極替換它為止。CMP過程中要保證多晶硅層厚度均勻,以支持后續的圖案化步驟。

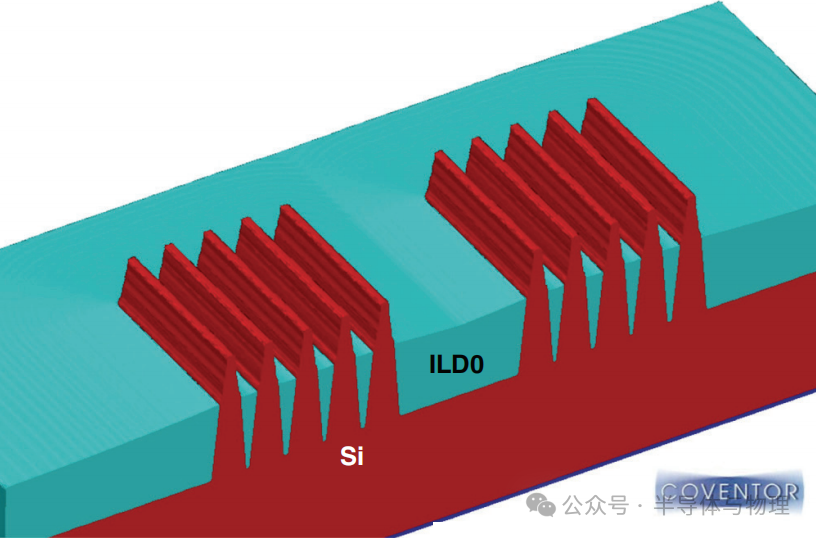

硬掩膜沉積

接著,在多晶硅層上沉積一層硬掩膜(HM),用于指導后續的柵極圖案化。根據技術節點的不同,如果柵極間距大于80nm,則可以使用單次193nm浸沒式光刻來形成線-空圖案;而對于更小的柵極間距,則需要采用如SADP或SAQP等倍增技術。硬掩膜的選擇和沉積條件對于后續圖案化的精度至關重要。

柵極圖案化

應用柵極掩模以在光刻膠中形成線-空圖案。經過硬掩膜蝕刻、光刻膠剝離和清潔后,再施加切割掩模并通過蝕刻切斷硬掩膜線條圖案。最后,利用形成的硬掩膜圖案蝕刻多晶硅,從而創建出設計好的啞柵極結構。

參考文獻

[1]Bellingham, Washington, USA : SPIE, [2016] | Includes bibliographical references and index.

[2]Maurya, Ravindra Kumar, and Brinda Bhowmick. "Review of FinFET devices and perspective on circuit design challenges."Silicon14.11 (2022): 5783-5791.

-

柵極

+關注

關注

1文章

188瀏覽量

21744 -

FinFET

+關注

關注

12文章

261瀏覽量

92338

原文標題:FinFet Process Flow-啞柵極的形成

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

重磅研究:7nm FinFET 性能優化的隱藏密碼 —— 柵極與鰭片間距調控

技術報告 | Gate 和 Fin Space Variation 對應力調制及 FinFET 性能的影響

MOSFET柵極閾值電壓Vth

為什么MOSFET柵極前面要加一個100Ω電阻

如何為EliteSiC匹配柵極驅動器

FLOW Digital Infrastructure宣布在東京市中心新建數據中心

體硅FinFET和SOI FinFET的差異

FinFet Process Flow—啞柵極的形成

FinFet Process Flow—啞柵極的形成

評論