隨著人工智能、數據中心、5G/6G、云計算、商用機器人和自動駕駛的快速發展,高速數據傳輸猶如連接城市的高速公路網絡一般,廣泛應用于消費電子、商用和軍用領域。國際標準組織IEEE和OIF光聯盟在不到十年內將以太網速率從10G提升至800G,推動了數字電路傳輸速度的飛躍。與此同時,PCB、連接器以及背板上信號的傳輸速率也越來越高,其中串行數據通信在傳輸過程中占據主導地位。在當今社會對于高速信號需求普遍存在的大背景下,按照最嚴格性能標準制造且設計精密的各種高速互連PCIE/ETH/VPX背板以及高速線纜,變得至關重要。背板作為嵌入式系統中的通信主干,必須依據嚴格的信號完整性標準開展設計,以確保系統內模塊之間能夠實現及時且精準的數據傳輸。

由于高速串行信號傳輸速率不斷攀升,在電路設計過程中,工程師常常遇到諸多棘手問題,諸如:系統不穩定、間歇性的死機、不同產品兼容性差以及經常出現誤碼等,而這些現象多半是信號完整性的問題。依照信號傳輸的完整流程,分別針對 TX 端(發送端)、傳輸鏈路以及 RX 端(接收端)展開相應測試,便能夠精準地定位問題根源,從而為后續的優化改進工作提供有力依據,確保高速傳輸系統的高效穩定運行。

什么是信號完整性?

sinolink technologies

信號完整性(Signal Integrity,簡稱SI)是指信號在線路傳輸過程中保持質量的能力,其核心要求在于確保信號的完整性、準確性和可靠性。在電子系統設計中,如果信號能夠按照既定的時序、持續時間和電壓幅度到達接收端,則表明該電路具有良好的信號完整性。良好的信號完整性意味著信號在傳輸和接收過程中能夠維持規定的電平和時序。反之,若信號完整性差,其影響因素諸多。其中主要是電源完整性問題。影響因素包括時序問題、反射、串擾、傳輸距離、信號衰減、溫度變化、信號傳輸介質、雜散、地彈、振鈴等,這些都會對信號完整性造成負擔,從而導致系統的穩定性下降、誤碼率增加、功耗增加和性能下降。因此,在高速電路設計中,確保良好的信號完整性至關重要。

在高速電路設計面臨三個嚴峻的問題:信號完整性SI ,電源完整性PI,電磁干擾EMI。SI的主要任務是保證數字電路各芯片之間信號的準確傳遞;PI的主要目的是確保各部分電路和芯片的可靠供電和噪聲抑制;EMI主要目的是確保PCB電路即不干擾其它設備,也不被其它設備干擾。值得注意的是SI的問題,一半以上是因為電源不好引發的信號質量問題,在EMI問題中,一個重要的影響因素是PDN上的高頻噪聲尤其是電源/地之間的高頻噪聲。

高速串行信號質量如何評估?

sinolink technologies

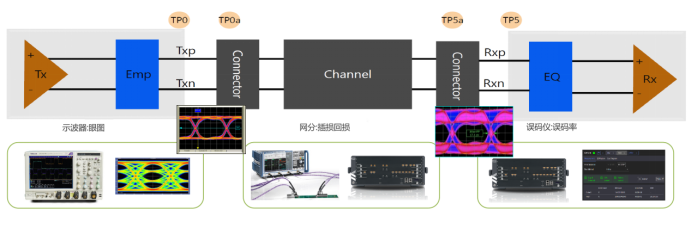

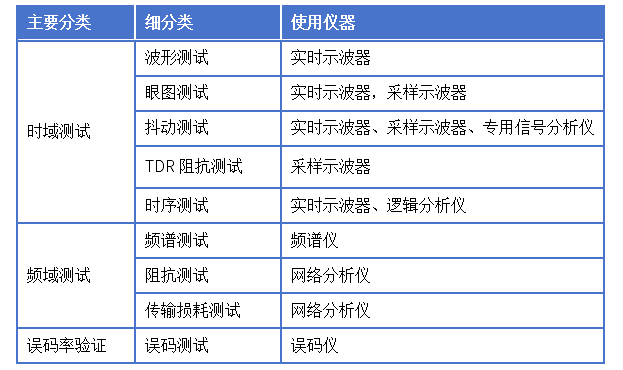

在高速信號傳輸鏈路中互連鏈路上任何一個環節的故障可能影響整個系統工作的效率以及穩定性,對于測試人員需要花費更多的成本去發現問題、定位問題、分析問題、解決問題。新標準逐漸從單一互連簡單要求的基礎上,額外增加協同整體要求。整個高速鏈路性能的評估,包括Tx發送端,傳輸鏈路,以及Rx接收端三大部分組成,發送、接收、電纜或者背板需要放在一個互連鏈路中評估。評估時按照時域、頻域和其他進行不同儀表的選取。

高速鏈路信號完整性測試工具

TX發送端信號質量的評估

其中TX發送端經常用示波器進行波形完整性、時序完整性、電源完整性、抖動/眼圖等測試。

波形完整性:

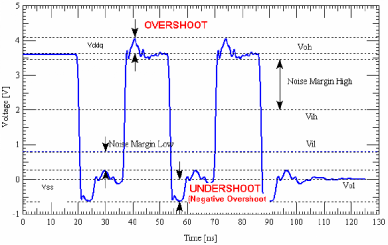

主要關注波形的單調性、過沖、振鈴、衰減。

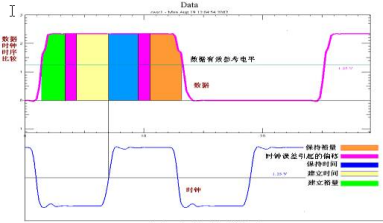

時序完整性:

主要關注建立保持時間、時序抖動、skew、毛刺等。

電源完整性:

簡稱PI,是單板電源設計的一項技術,通過合理的電源平面和濾波設計,為單板上的器件提供穩定/潔凈的電源供電,保證單板穩定工作,所以紋波測試為電源測試的必測項,PI和SI是相互影響的。PI包括電源系統設計、直流壓降分析、電壓瞬態分析、同步開關噪聲以及器件建模等。

抖動/眼圖:

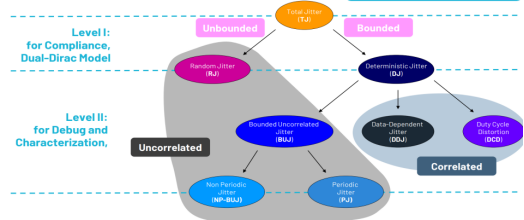

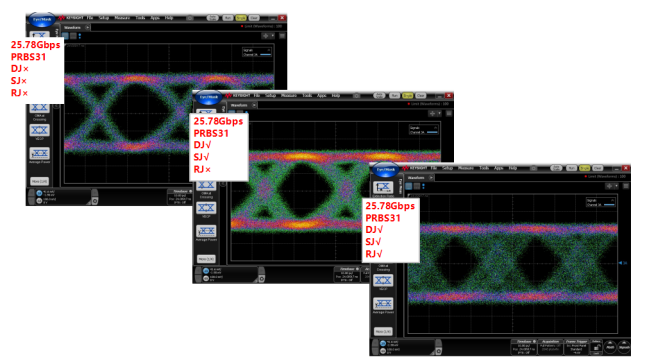

損耗、反射、串擾三大信號完整性的殺手給信號傳輸帶來巨大影響,會使信號的抖動變大,眼圖變差,干擾時鐘恢復,降低系統性能,進而在接收端帶來誤碼。抖動又可以按照成因分為:TJ、RJ、DJ。DJ中又可細分為PJ、DCD、ISI/DDJ。

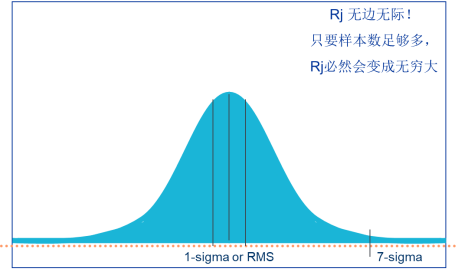

其中Random Jitter(隨機抖動)的統計分布是正態高斯分布,是無界抖動,隨著樣本量的增加RJ會一直增加。

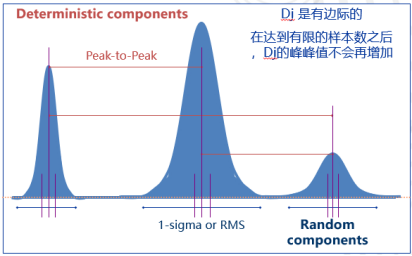

然而Deterministic Jitter (確定性抖動)是有界抖動,在達到有限樣本數之后,DJ的peak-peak值不會再增加。

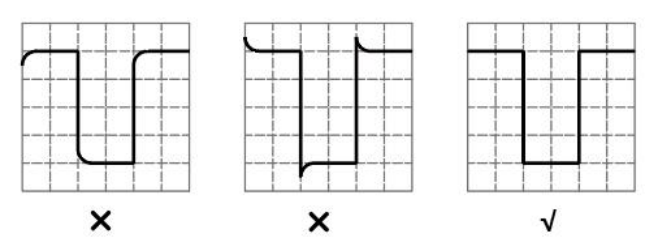

上述抖動在測試中經常用來定位問題信號完整性問題來源,除此之外,我們通常還需要進行眼圖模板的測試來直觀的表述信號質量的好壞。

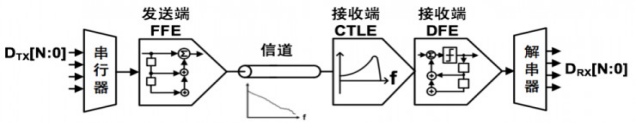

為了在抵抗傳輸損耗帶來的影響,改善信號質量,常用的均衡有TX端的FFE,RX端有FFE、CTLE、DFE。

其中TX端的預加重和去加重的目的都是盡量平衡高頻分量和低頻分量,減少傳輸鏈路對高頻分量衰減大于低頻分量衰減。預加重技術就是在傳輸線的始端增強信號的高頻分量,以補償高頻分量在傳輸鏈路中較大的衰減。去加重則是降低低頻分量的始端信號。

其中RX端最常用的均衡包括FFE、CTLE、DFE。

FFE實質是使用數字線性高通濾波器提高信號的高頻分量,實現信道的補償。

CTLE是直接通過線性模擬高通濾波器擬合信道的衰減,實現信道的補償。信道的頻率響應可以看做是一個低通濾波器,因此將信道和一個高通濾波器串聯就能得到一個全通的濾波器。

DFE為判決反饋均衡,就是將判決后的信號反饋到輸入信號上。與FFE類似,DFE也是通過數字高頻濾波器實現的,DFE可以只放大高頻信號,而不放大高頻噪聲。

高速傳輸鏈路評估

信號在傳輸鏈路路徑上傳輸時會有損耗,反射,串擾的問題,導致信號發生畸變。

損耗:傳輸線的損耗對不同頻率是不均勻的,頻率越高,損耗越大,上升沿越緩。速率越高,傳輸線越長,損耗所帶來的問題越嚴重,眼圖越容易閉合。

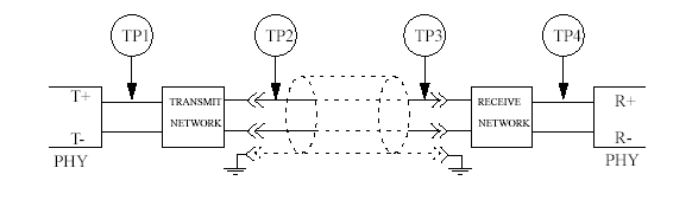

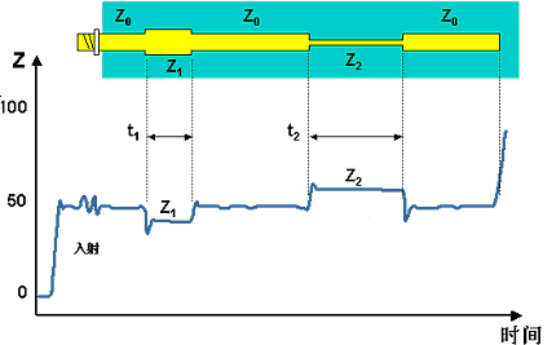

反射:傳輸線上分布電容、電感、和小電阻的存在,會導致傳輸線的分布式阻抗不均勻,信號流經傳輸線時部分能量會沿原路反射回去,通常使用TDR來測量傳輸路徑的阻抗變化,如下圖:

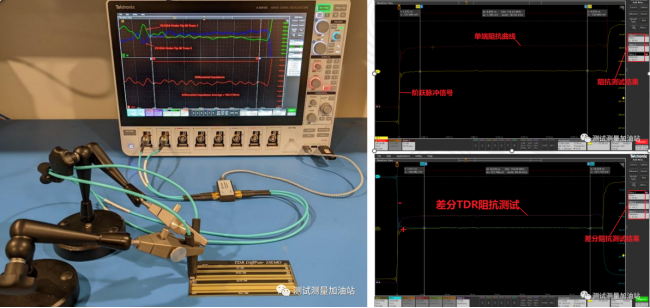

下面為實時示波器TDR阻抗測試:

信號在傳輸過程中,對不同速率其損耗不同,反射和串擾都可以導致信號的波形發生失真,導致眼圖閉合。通常使用矢量網絡分析儀VNA進行S參數測試和TDR或VNA進行阻抗測試。

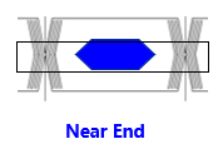

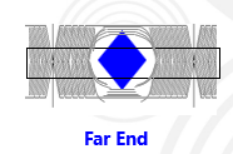

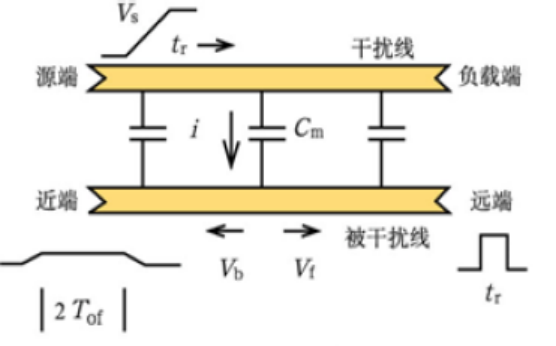

串擾:相鄰通道間通過地線或空間輻射產生的互相影響。頻率越高,串擾越大。串擾會帶來額外的噪聲,毛刺,抖動,并且使得信噪比變差。遠端串擾: 同向傳輸(同源)信號的干擾,幅度高,脈沖很窄。近端串擾: 反向傳輸(非同源)信號的干擾,幅度低,脈沖很寬。

RX接收端容限能力的評估

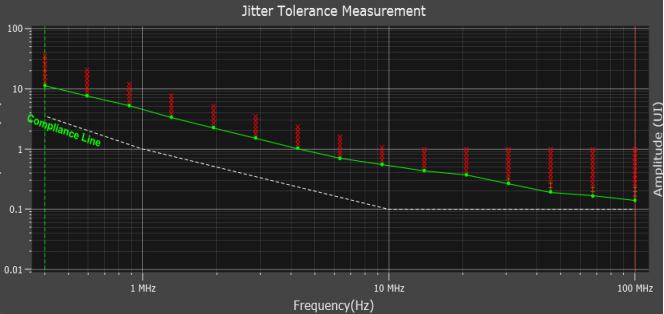

發送端一般利用實時示波器測抖動和眼圖,接收端需要利用誤碼儀進行抖動容限測試和噪聲容限測試。接收端中包括CDR時鐘恢復、復雜的均衡和信號調理等復雜結構。單純考察發送端是不足以保證沒有誤碼,接收端的測試也是非常重要,各種高速標準也明確提出了接收端容限測試的規范。誤碼儀是進行高速SerDes芯片接收端測試必備儀器。RX接收端會根據對應的協議規范或者自定義標準進行誤碼率、JTOL、ITOL的測試。下面我們以RX接收端測試為例為大家介紹高速傳輸鏈路信號完整測試。

測試原理:

使用測試儀表產生一個劣化(注入抖動)的眼圖信號,俗稱壓力眼信號。壓力眼信號的參數有明確規定,,在不同的規范中具體指標會有不同。通過校準后的壓力眼會輸入被測接收機進行抖動容限測試。中星聯華SL3000B系列高性能誤碼儀可提供PJ、RJ、BUJ等抖動注入,可以為RX JTOL測試提供強力支持。

測試流程:

產生規范要求的抖動分量,在不同的頻點上分別產生相應的抖動量

將stressed信號注入DUT Rx

統計DUT Tx端發出的信號的誤碼率是否達到要求

注入抖動眼圖:

測試結果圖:

目前,中星聯華的高性能誤碼儀是國內首個支持注入抖動和加噪聲創建壓力信號的高性能誤碼儀,也是目前國內首款能夠滿足接收端抖動容限JTOL和噪聲容限ITOL測試的誤碼儀。其中可支持的注入抖動類型有低頻正弦抖動、高頻周期抖動、BUJ串擾抖動、RJ隨機抖動以及SSC擴頻時鐘等;支持的噪聲類型有CMI和DMI和BBN寬帶白噪聲,有效地解決“卡脖子”的難題。

RX接收端測試利器——

中星聯華高性能誤碼儀

sinolink technologies

產品特色:

模塊化:多通道靈活配置,單機支持32發32收

高速率:1G-120Gbps,數據速率靈活可調

壓力眼:注抖加噪,讓信號擁有72般變化

UDP:最大可支持16Gbit超長用戶自定義碼型

中星聯華高性能誤碼分析儀具有模塊化設計、靈活的通道配置、高速率、注抖加噪創建壓力眼信號、超長用戶自定義碼型等業內領先的核心技術,可用于高速Serdes芯片和高速接口、光芯片、光器件、光模塊、光傳輸、高速互連等領域苛刻的測試。

-

測試

+關注

關注

9文章

6203瀏覽量

131361 -

信號完整性

+關注

關注

68文章

1486瀏覽量

98105 -

高速信號

+關注

關注

1文章

267瀏覽量

18505

發布評論請先 登錄

IDT信號完整性產品:解決高速信號傳輸難題

PK6350無源探頭在高速數字總線信號完整性測試中的應用案例

高速信號完整性分析測試

高速信號完整性分析測試

評論