ASIC(Application Specific Integrated Circuit)即專用集成電路,是指應特定用戶要求和特定電子系統的需要而設計、制造的集成電路。ASIC集成電路設計流程可以分為前端設計和后端設計兩大部分,以下是的流程介紹:

一、前端設計

- 準備需求規范

- 確定芯片的具體指標,包括物理實現(制作工藝、裸片面積、封裝)和性能指標(速度、功耗)以及功能指標(功能描述、接口定義)。

- 系統級設計

- 使用系統建模語言(如Matlab、C等)對各個模塊進行描述,驗證方案的可行性。

- RTL設計

- RTL驗證

- 消除Linting Error,確保可綜合。

- 執行基于周期的驗證(功能),驗證RTL的協議行為。

- 執行屬性檢查,驗證RTL實現和規范理解匹配。

- 執行IP功能驗證。

- 邏輯綜合

- 設計檢查

二、后端設計

- 布局布線準備

- 綜合網表文件(VHDL/Verilog格式)和SDC(約束文件)作為輸入文件傳遞給布局布線工具。

- Floor-plan

- 布局(Placement)

- 在布局工具中,切割行,在防止放置單元的位置創建阻塞。

- 單元的物理布局基于時序/面積需求執行。

- 布線(Routing)

- 最初的全局布線和細節布線,根據生產需要滿足DRC需求。

- 參數提取與驗證

- 執行布線后,將布線后Verilog網表、標準單元LEF/DEF文件給提取工具,以在SPEF(標準寄生交換格式)格式中提取芯片寄生(RLC阻感容)參數,并生成SPEF文件。

- 布局布線后檢查是否設計滿足需求(功能、時序、面積、功耗、可測性、DRC、LVS、ERC、ESD、SI、IR-Drop)。

- 執行布線后網表的功耗分析,確認設計是否滿足功耗目標。

- 使用布線后網表執行門級仿真,檢查設計是否滿足功能需求。

- 執行RTL和布線網表之間的形式驗證,確認PR工具未修改功能性。

- 使用SPEF文件和布線網表文件執行STA,檢查設計是否滿足時序需求。

- 在DFT工具中執行scan-tracing,檢查scan-chain是否是基于DFT需求建立的,使用DFT工具執行故障覆蓋,生成ATPG測試向量。

- 執行稱作物理驗證的DRC(設計規則檢查)驗證,確認設計滿足了制造需求。

- 執行LVS(layout vs Spice)檢查,將布線網表轉換為spice(SPICE-R),轉換綜合網表(SPICE-S),比較確認二者匹配。

- 執行ESD檢查,在芯片中同時具備模擬部分和數字部分的情況下,確認正確的背靠背二極管被放置并且具備正確的防護。對數字和模擬部分分別設置電源和地,以降低襯底噪聲。

- 執行特定的STA以確認芯片的信號完整性。將布線網表和SPEF文件(包含耦合電容值的寄生參數)輸入STA工具執行此步驟。

- 執行IR壓降分析,電源網格足夠健壯以經受設計的靜態和動態功耗下降,并且IR壓降在目標限制范圍內。

- 芯片完工修整

- 布線設計使用設計約束驗證完成后,進入芯片完工修整階段(金屬開槽、放置解耦帽等)。

- 設計與制造準備

- 芯片設計準備好進入制造單元,以制造廠可理解的GDS文件發布設計文件。

- GDS發布后,執行LAPO檢查,確認發布給fab的數據庫的正確性。

- 封裝與測試

- 執行封裝引線鍵合(wire-bounding),將芯片連接至封裝。

綜上,ASIC集成電路設計流程是一個復雜而精細的過程,需要多個階段的協同工作和嚴格的驗證與測試,以確保最終產品的性能和可靠性。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

集成電路

+關注

關注

5452文章

12571瀏覽量

374519 -

模塊

+關注

關注

7文章

2837瀏覽量

53283 -

asic

+關注

關注

34文章

1274瀏覽量

124567 -

電子系統

+關注

關注

0文章

508瀏覽量

32287

發布評論請先 登錄

相關推薦

熱點推薦

東莞理工學院“小眼睛科技杯”第四屆集成電路設計與創新應用競賽圓滿落幕

BASEDINNOVATION“小眼睛科技杯”集成電路設計與創新應用競賽2025年11月23日,東莞理工學院第四屆集成電路設計與創新應用競賽于學術會議中心圓滿落幕。本屆競賽由校團委、學生工作部

PDK在集成電路領域的定義、組成和作用

PDK(Process Design Kit,工藝設計套件)是集成電路設計流程中的重要工具包,它為設計團隊提供了與特定制造工藝節點相關的設計信息。PDK 是集成電路設計和制造之間的橋梁,設計團隊依賴 PDK 來確保設計能夠在晶圓

華大九天Empyrean Liberal工具助力數字集成電路設計

數字集成電路設計中,單元庫和IP庫宛如一塊塊精心打磨的“積木”,是數字IC設計的重要基礎。從標準單元庫(Standard Cell)、輸入輸出接口(I/O Interface)、存儲器單元(如

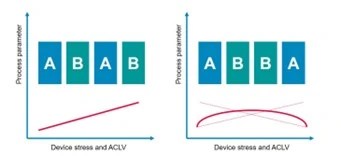

通過交互式對稱性校驗提升集成電路設計流程

在高性能集成電路 (IC) 設計領域,對稱性不僅僅是一種美學偏好,同時也是確保器件正常運行的關鍵因素。尤其是在模擬和射頻 (RF) 設計中,對稱性設計有助于電性保持一致。然而,在 IC 設計中確保

發表于 05-22 11:07

?1480次閱讀

實用電子電路設計(全6本)——數字邏輯電路的ASIC設計

由于資料內存過大,分開上傳,有需要的朋友可以去主頁搜索下載哦~

本文以實現高速高可靠性的數字系統設計為目標,以完全同步式電路為基礎,從技術實現的角度介紹ASIC邏輯電路設計技術。內容包括:邏輯

發表于 05-15 15:22

中國集成電路大全 接口集成電路

資料介紹本文系《中國集成電路大全》的接口集成電路分冊,是國內第一次比較系統地介紹國產接口集成電路的系列、品種、特性和應用方而知識的書籍。全書共有總表、正文和附錄三部分內容。總表部分列有國產接口

發表于 04-21 16:33

基于運算放大器和模擬集成電路的電路設計(第3版)

內容介紹:

本文全面闡述以運算放大器和模擬集成電路為主要器件構成的電路原理、設計方法和實際應用。電路設計以實際器件為背景,對實現中的許多實際問題尤為關注。全書共分13章,包含三大部分。第一部分(第

發表于 04-16 14:34

概倫電子集成電路工藝與設計驗證評估平臺ME-Pro介紹

ME-Pro是概倫電子自主研發的用于聯動集成電路工藝與設計的創新性驗證評估平臺,為集成電路設計、CAD、工藝開發、SPICE模型和PDK專業從業人員提供了一個共用平臺。

法動科技EMOptimizer解決模擬/射頻集成電路設計難題

一直困擾模擬/射頻集成電路工程師多年的痛點,被業界首款基于人工智能(AI)技術的模擬/射頻電路快速設計優化軟件EMOptimizer革命性地改變和突破!

集成電路版圖設計的基本概念和關鍵步驟

在集成電路設計中,版圖(Layout)是芯片設計的核心之一,通常是指芯片電路的物理實現圖。它描述了電路中所有元器件(如晶體管、電阻、電容等)及其連接方式在硅片上的具體布局。版圖是將電路設計

集成電路產業新地標 集成電路設計園二期推動產業創新能級提升

在2025海淀區經濟社會高質量發展大會上,海淀區對18個園區(樓宇)的優質產業空間及更新改造的城市高品質空間進行重點推介,誠邀企業來海淀“安家”。2024年8月30日正式揭牌的集成電路設計園二期就是

ASIC集成電路設計流程

ASIC集成電路設計流程

評論