- ALINX NVMeIP -

在當下數據驅動的時代,企業對高性能存儲解決方案的需求不斷增加。NVMe AXI IP 憑借其支持大數據量、高速傳輸、低延遲等存儲性能優勢,成為眾多開發者和企業的理想選擇。

NVMe專為 SSD 而生,通過直接利用 PCIe 通道,避免 SATA 協議和外置控制器(PCH)的額外延遲,使性能大幅提升,尤其在隨機 I/O 操作中表現突出。

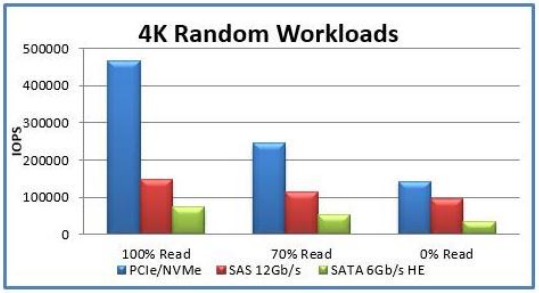

NVMe PCIe SSD的 IOPs 性能可達高端企業級 SATA SSD 的十倍(具體場景為高隊列深度的隨機讀寫),同時支持自動功耗狀態切換和動態能耗管理功能,顯著降低功耗。

( NVMe/SAS/SATA 存儲設備單讀性能對比)

NVMe 協議憑借其高速傳輸、低延遲、高效能存儲和高可靠性的特點,在數據中心、邊緣計算、企業存儲、AI 服務器和云計算等領域有著廣泛應用。

ALINX NVMe IP 詳情

ALINX NVMe IP 針對當前數據密集型應用進行了深度優化,顯著縮短了延遲時間,提升數據吞吐量,滿足云計算、大數據分析、人工智能、虛擬現實/增強現實( VR/AR )等前沿領域的迫切需求。

兼容性方面,NVMe IP 不依賴 CPU,全部由 FPGA 完成處理,需要 FPGA 具有足夠的資源和適當的硬件支持。ALINX NVMe IP 目前支持AMD Virtex 7/ AMD UltraScale/AMD UltraScale+系列器件。

技術支持方面,ALINX 提供完善的技術支持和高效的定制化服務,由經驗豐富的 IP 研發團隊專人對接,全程協助客戶完成 IP 集成和性能優化,確保客戶需求快速實現。

考慮到每個應用場景都有其獨特需求,ALINX NVMe AXI IP 為開發者提供了豐富的定制選項,允許根據特定的應用需求對其性能進行精準調整,包括不限于優化特定工作負載下的數據傳輸速率,根據不同的存儲容量需求進行配置等。

以下是 ALINX NVMe IP 的詳細介紹:

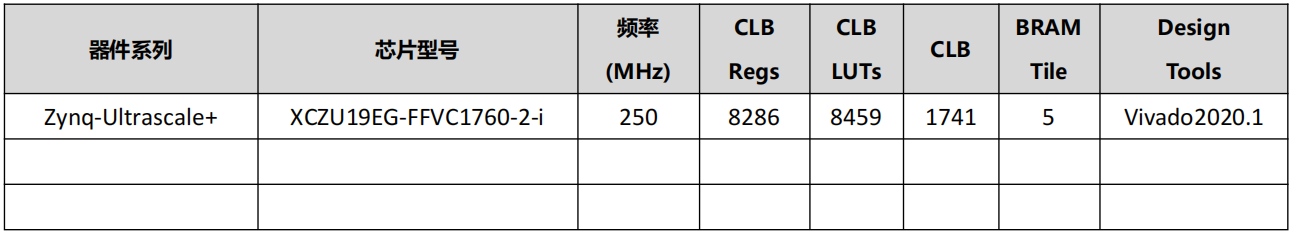

IP 資源消耗表

注:IP 實際邏輯資源消耗受實例化中其他邏輯資源消耗影響

產品特性

功能支持:命令支持(Identify、Write、Read、Flush),兼容 NVMe 1.4 協議,支持 PCIe Gen 1.0-4.0;

性能參數:

(1)最大隊列深度:每個隊列支持 65535 個 I/O 命令;

(2)傳輸速率:基于 PCIe 3.0 X4,讀寫速率均可達 3000MB/s;

靈活性:支持多種存儲單元(512 字節 / 4096 字節);

支持定制化服務:包括數據傳輸速率優化和存儲容量配置;

版本支持:支持兩個版本(AXI FULL 版本 / AXI Stream 版本);

參考設計:XCZU19EG + FMC子板(FH1402)+SAMSUNG 980 M.2 SSD。

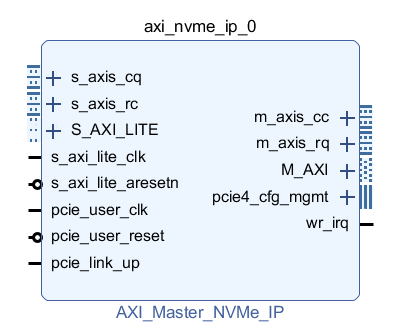

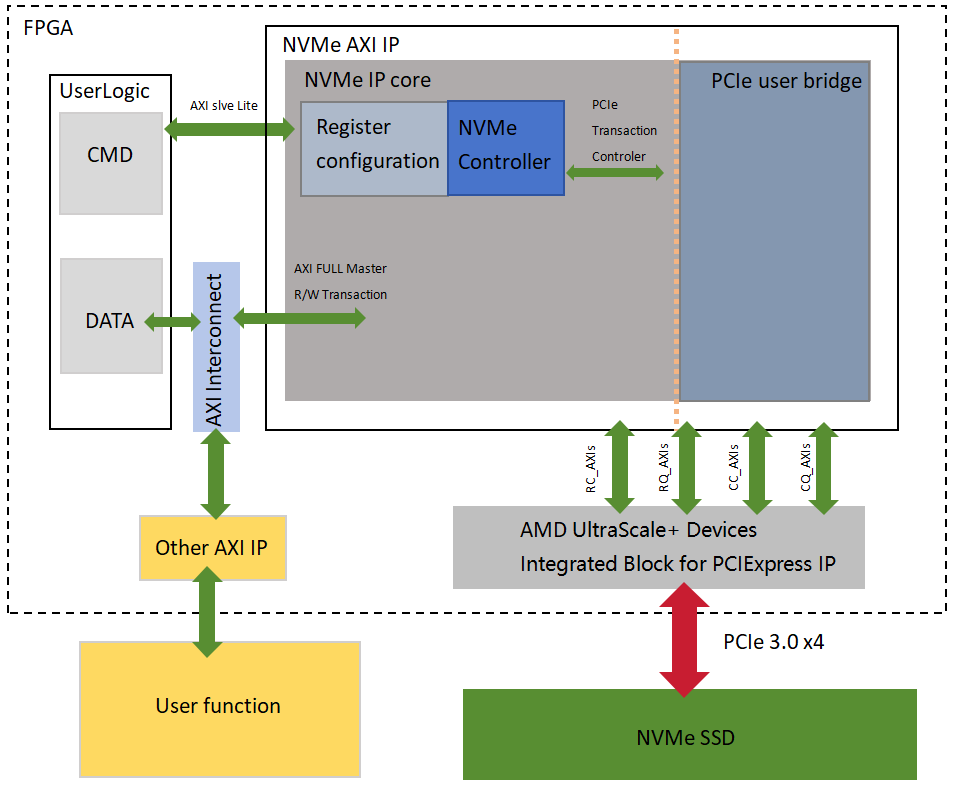

AXI-Master-FULL 版本

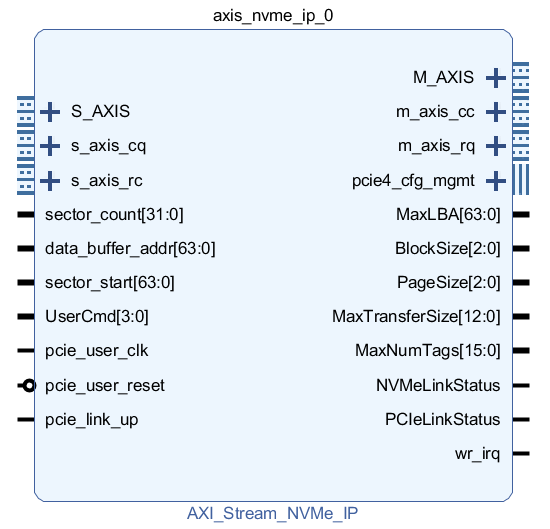

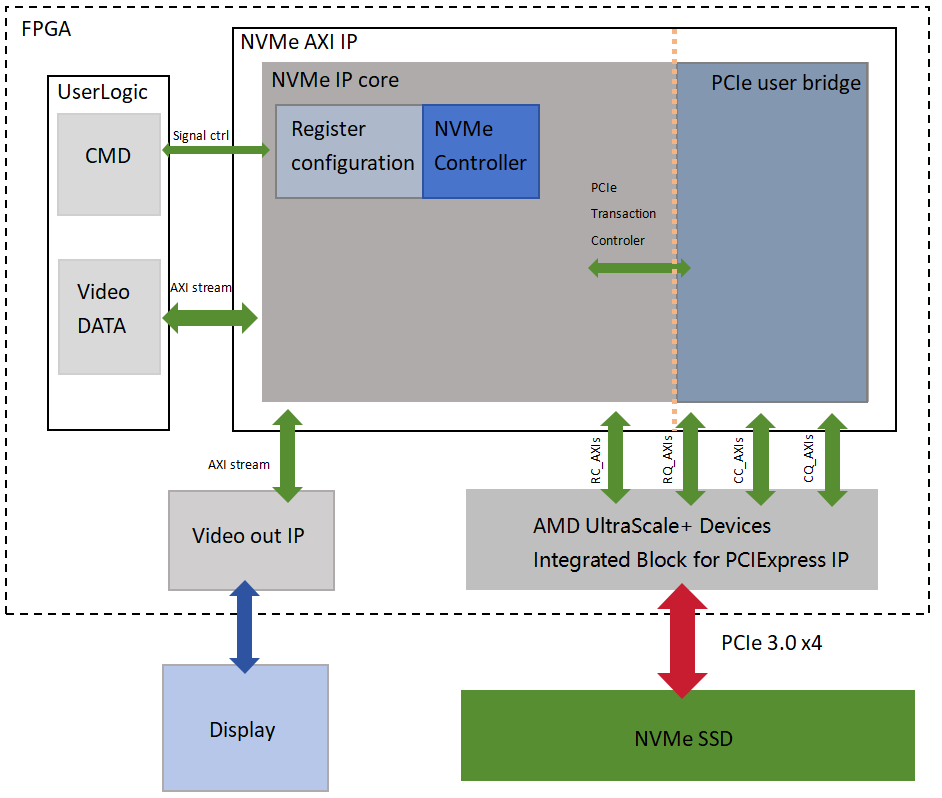

AXI-Stream 版本

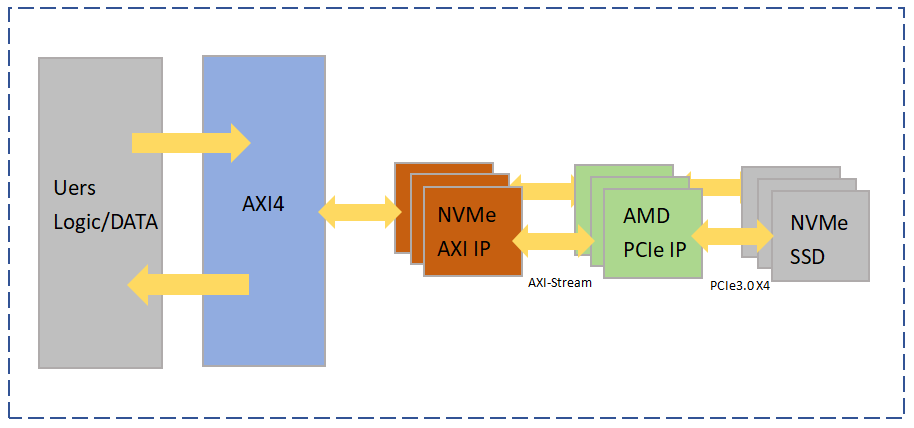

NVMe AXI IP 應用交互

NVMe AXI IP 通過 PCIe Bridge 實現 PCIe 協議交互,支持 AXI FULL 和 AXI Stream 兩種接口模式。用戶數據通過 AXI Interconnect 接入后,經過 NVMe AXI IP 的協議邏輯處理,被打包為 PCIe TLP 包并寫入 NVMe SSD 存儲;同樣,數據從 NVMe SSD 提取后,通過協議解析和 AXI 接口傳遞到上層邏輯。

Example 舉例

AXI-Master-FULL 版本

AXI 讀寫:在系統正常啟動后,NVMe AXI IP 自動初始化并建立 PCIe 鏈路連接。初始化完成后,用戶的數據流通過 AXI Interconnect IP 傳送到 NVMe AXI IP 的 AXI Master FULL 接口,進行 NVMe 協議的處理。數據被打包為 TLP 層 PCIe 包,并通過 RC/RQ/CC/CQ AXI Stream 接口與 AMD UltraScale+ 設備的 PCIe 集成模塊(Integrated Block for PCIExpress)連接,最終寫入 NVMe SSD 存儲。當需要讀取數據時,NVMe AXI IP 從 NVMe SSD 通過 RC/RQ/CC/CQ AXI Stream 接口提取數據,再通過 AXI Master FULL 接口與 AXI Interconnect IP 連接,將數據傳輸到其他 AXI 總線接口供用戶邏輯使用。

AXI-Stream 版本

AXI Stream 讀寫:在系統正常啟動后,NVMe AXI IP 自動進行初始化并建立連接。初始化完成后,用戶的數據流通過 AXI Stream 接口輸入到 NVMe AXI IP,執行 NVMe 協議的交互處理。數據被打包為 TLP 層 PCIe 包,通過 RC/RQ/CC/CQ AXI Stream 接口與 AMD UltraScale+ 設備的 PCIe 集成模塊連接,最終存儲到 NVMe SSD。當從 NVMe SSD 讀取數據時,NVMe AXI IP 使用 RC/RQ/CC/CQ AXI Stream 接口提取數據,并通過 AXI Stream 接口傳輸給連接的視頻輸出 IP,進而通過視頻接口進行數據展示。

審核編輯 黃宇

-

FPGA

+關注

關注

1660文章

22408瀏覽量

636222 -

存儲

+關注

關注

13文章

4787瀏覽量

90057 -

IP

+關注

關注

5文章

1862瀏覽量

155820 -

SSD

+關注

關注

21文章

3109瀏覽量

122221 -

nvme

+關注

關注

0文章

298瀏覽量

23837

發布評論請先 登錄

高性能網絡存儲設計:NVMe-oF IP的實現探討

NVMe over Fabrics 國產 IP:高性能網絡存儲解決方案

NVMe高速傳輸之擺脫XDMA設計52:主要功能測試結果與分析4(NVMe 指令提交與完成機制測試)

NVMe高速傳輸之擺脫XDMA設計50:主要功能測試結果與分析2 nvmePCIe高速存儲

Xilinx高性能NVMe Host控制器IP+PCIe 3.0軟核控制器IP,純邏輯實現,AXI4和AXI4-Stream DMA接口,支持PCIe 3.0和4.0

NVMe高速傳輸之擺脫XDMA設計43:如何上板驗證?

NVMe高速傳輸之擺脫XDMA設計40:隊列管理功能驗證與分析4

NVMe高速傳輸之擺脫XDMA設計23:UVM驗證平臺

NVMe高速傳輸之擺脫XDMA設計18:UVM驗證平臺

NVMe IP高速傳輸卻不依賴XDMA設計之三:系統架構

一文詳解 ALINX NVMe IP 特性

一文詳解 ALINX NVMe IP 特性

評論