本次技術分享介紹VeriStand的執行機制以及該機制下信號傳輸的延遲,當仿真測試對信號延遲有一定要求時,考慮VeriStand執行機制的影響是必要的,現在請跟隨小編的步伐一起學習吧!

本文教程:

VeriStand執行機制

一、硬件單點采樣

VeriStand添加通道時默認使用的是硬件單點采樣模式,該模式下采集數據不會在緩存中停留等待,這是由于硬件單點采樣模式不帶緩沖機制,無需等待采集到特定個點數后再讀取。

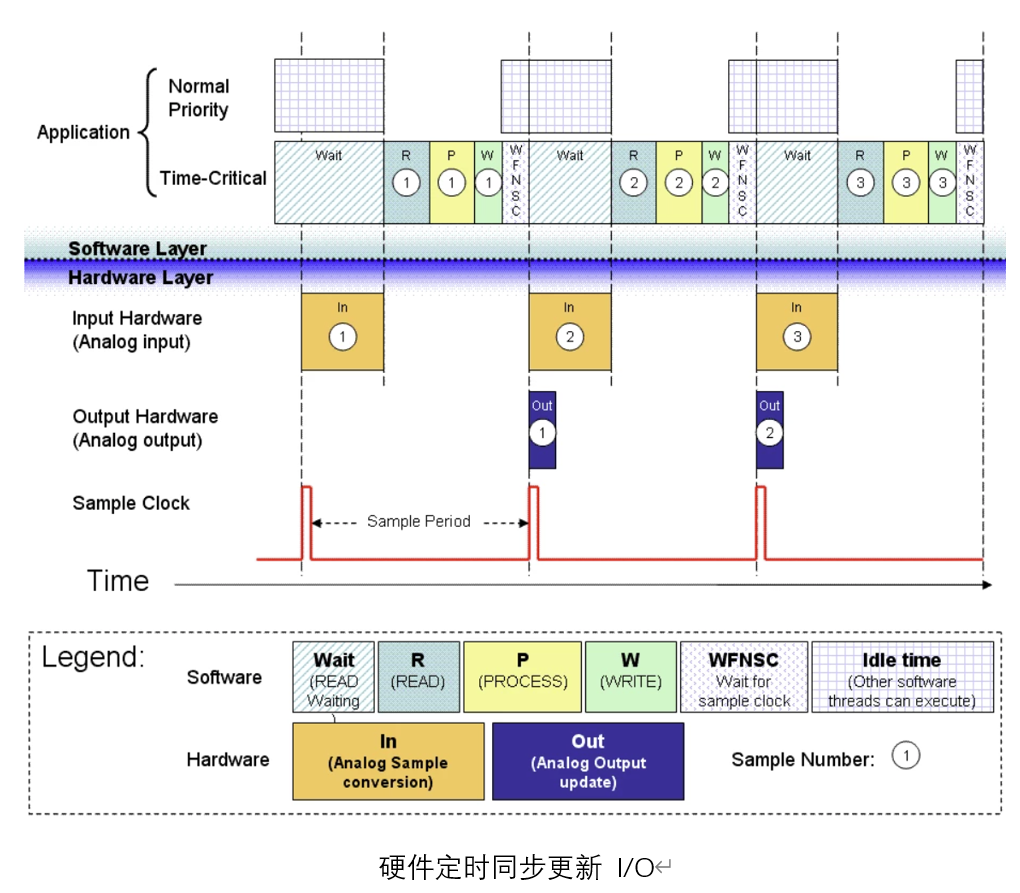

在VeriStand中設置硬件單點定時采集時,將使用機箱背板提供的時鐘來同步AI和AO 。如下圖,硬件定時同步更新 I/O模式下AI采集的值經過了R、P、W步驟后,需要等待下一次時鐘的上升沿才能由AO輸出,即AI、AO操作需要與時鐘信號對齊。

二、VeriStand的工作機制和延遲

1、并行執行模式

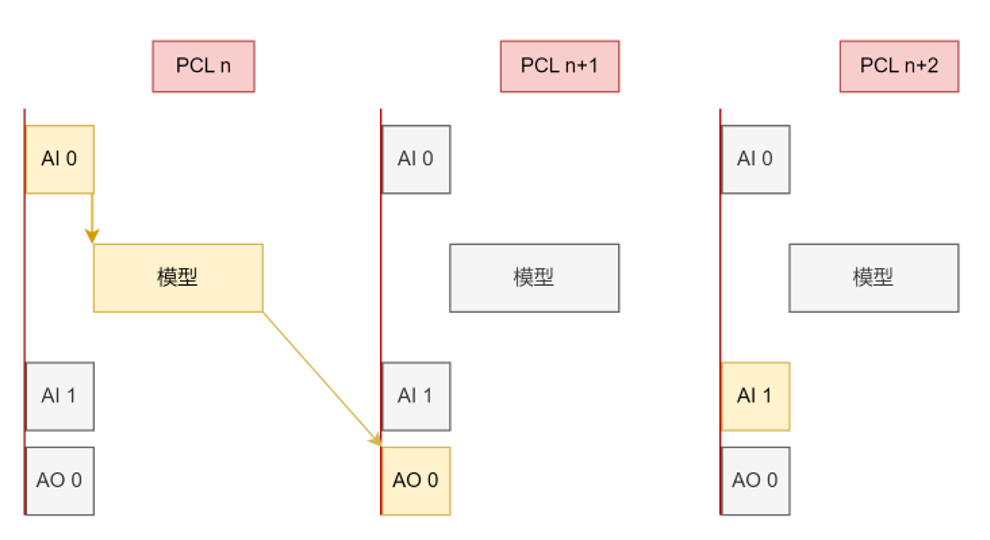

在并行執行模式下,使用硬件定時同步更新 I/O,AI和AO需要與時鐘對齊,AO輸出的是上一次PCL主循環(Primary Control Loop)中AI讀取并經模型處理的值,所以存在一個PCL執行時間的延遲,對于10k模擬頻率的情況,延遲為100μs。

具體原理如上圖,模型的執行結果直接傳輸到下一PCL主循環,AI、AO都對齊來自機箱背板的時鐘信號實現同時執行,但AO輸出的是上一個PCL的執行結果,過程中有一個PCL執行周期的延遲。

2、低延遲執行模式

低延遲執行模式下,AI采集到值并經過模型運算后立刻傳到AO輸出,無需等待到下一次PCL再進行AO輸出;AI在采樣時鐘的上升沿進行采集,AO等待接受到模型執行結果后輸出,AI到AO的延遲約等于模型執行時間(數據的硬件傳輸時間不超過1us)。

此時AI仍然嚴格對齊時鐘,但是AO的更新時間由得到模型處理結果后對AO賦值的時間節點決定,因為模型的執行速度不是精確恒定,AO的輸出節拍會有抖動,是否產生不良影響由具體情況而定。

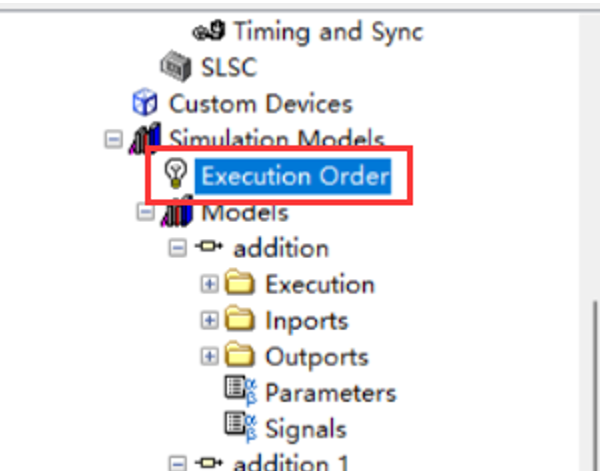

3、模型執行順序Execution Order

當需要執行多個模型且模型之間有數據傳遞,模型的執行順序設置會對延遲產生較大影響。

還記得之前教程出現過的Execution Order嗎,在這里可以設置模型的執行順序,執行前后順序按Group分組,默認會把所有模型放到同一分組并行執行。下面通過示意圖展示模型執行的機制,結論基于驗證實驗推導而來。

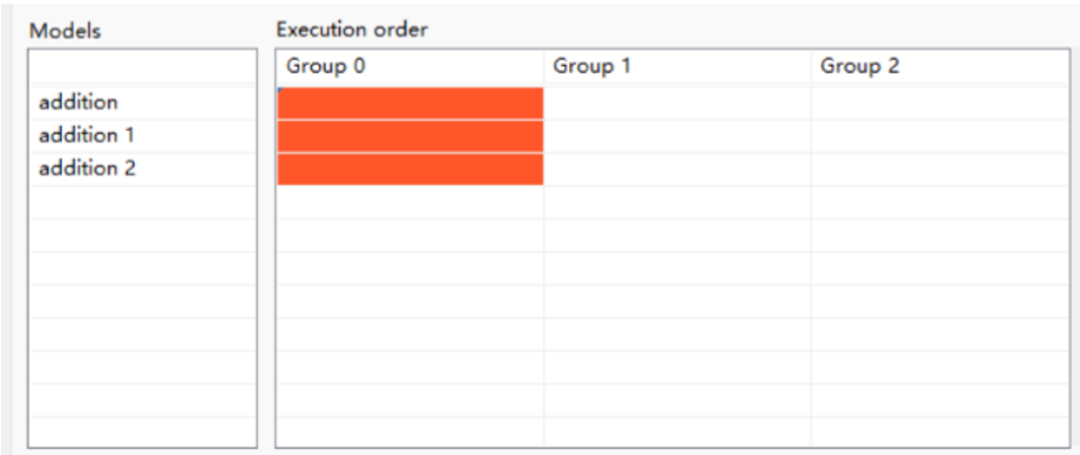

3.1 模型的并行執行

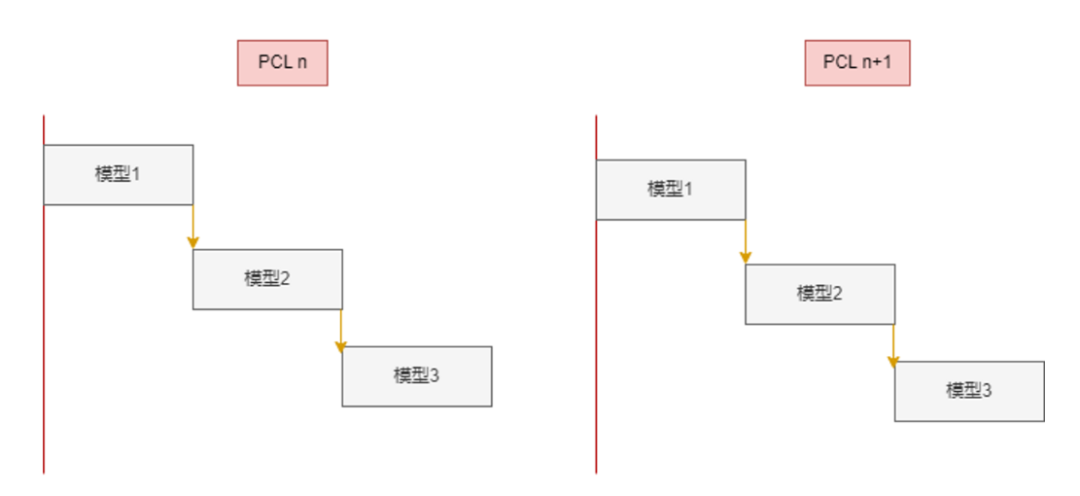

首先看默認的模型并行執行的情況,假設三個模型從上到下依次傳遞數據。

三個模型同組的執行機制如上圖所示,類似于前文描述的 輸入、模型、輸出 并行執行模式,只不過這里變成了模型1、模型2、模型3并行執行,即三個模型依舊是同時執行,但每次傳遞數據到下一個模型都必須等待下一次PCL主循環。

所以,若VeriStand設置為并行執行,三個模型均在同一Group,則上圖中PCL n進行了AI采集并立刻傳輸給模型1運算,經過傳遞,最終在PCL n+2中由模型3輸出最終計算結構,并在下一次的PCL n+3中由AO輸出,AI到AO有三個PCL周期的延遲。

同理,如果VeriStand設置為低延遲模式,三個模型依然是在同一Group,那么AI到AO的延遲=兩個PCL執行周期+模型3的執行耗時。

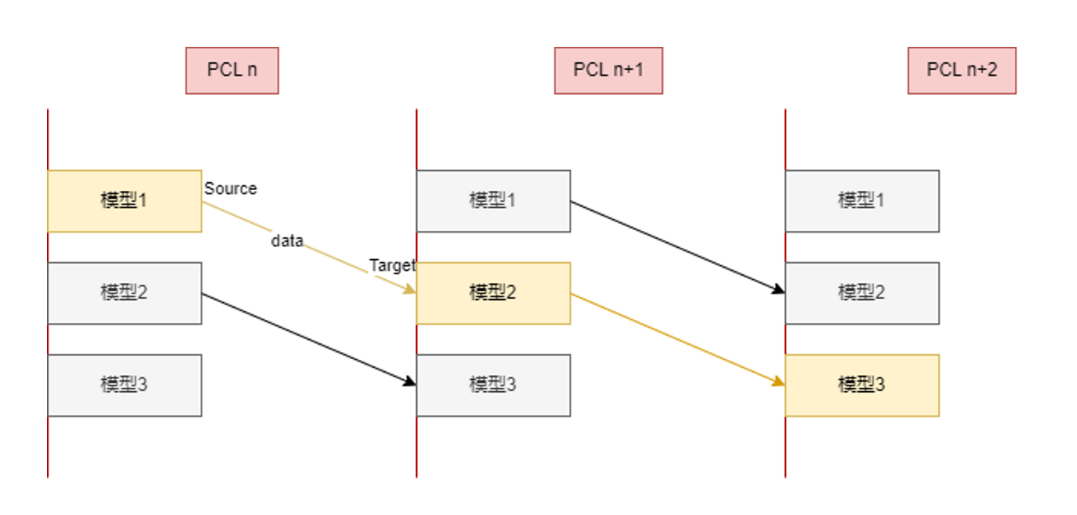

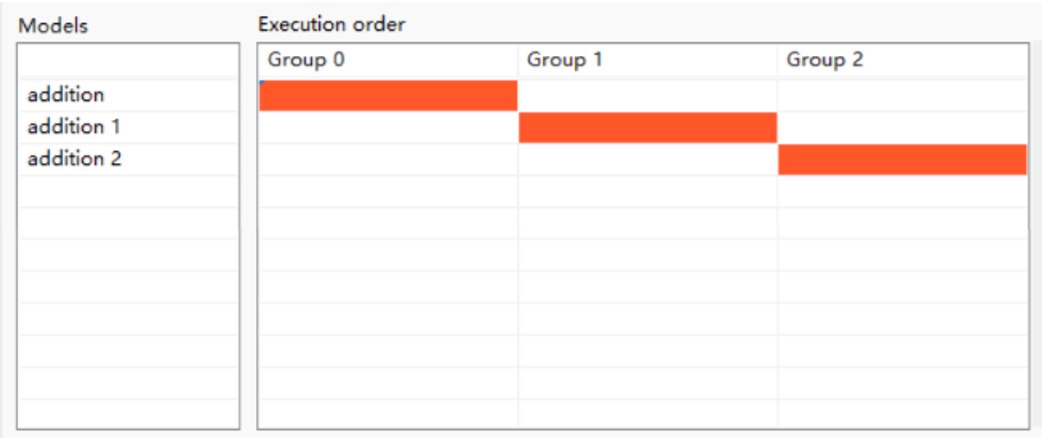

3.2 模型的分步執行

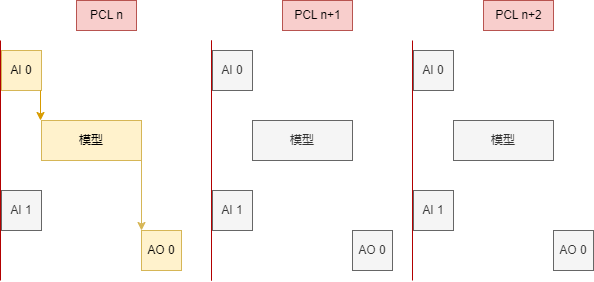

當模型被安排到前后按順序執行的一個個Group時,模型的執行機制就類似于上文中描述的VeriStand低延遲執行模式。

如上圖所示,三個模型不是并行執行,其按照設置的Group順序前后進行。

若VeriStand設置為并行執行,模型執行順序按照分組前后執行:AI在PCL n開始時采集,經過三個模型計算,運算結果在PCL n+1開始時由AO輸出,AI到AO的延遲為一個PCL周期。

若VeriStand設置為低延遲模式,模型執行順序按照分組前后執行:AI在PCL n開始時采集,經過三個模型計算,運算結果在第三個模型執行結束后立刻由AO輸出,無需等待到下一次PCL主循環,AI到AO的延遲約等于三個模型的計算耗時。

4、實驗驗證

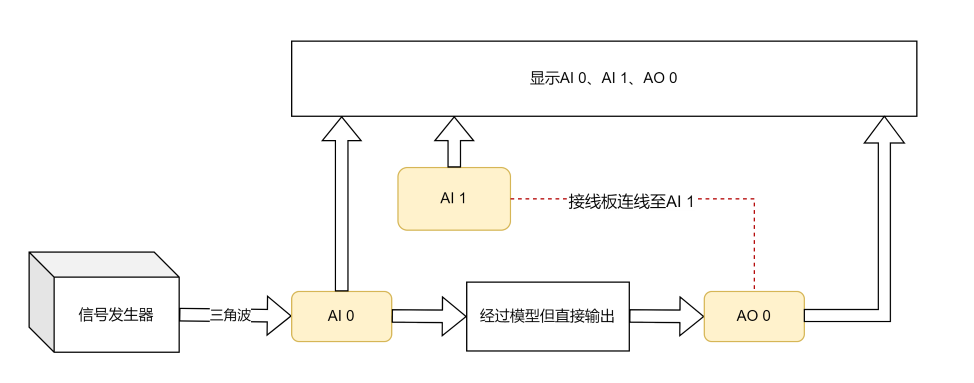

感興趣的小伙伴可以參考上圖的原理設計一個實驗來驗證本文所提到的兩種執行模式的原理和延遲。其中,信號發生器產生三角波輸入到AI 0,VeriStand采集到AI 0的數據后映射到模型,模型不改變值并直接輸出到AO 0,AO 0輸出電壓到AI 1,將AI 0、 AI 1、AO 0顯示在波形顯示面板。

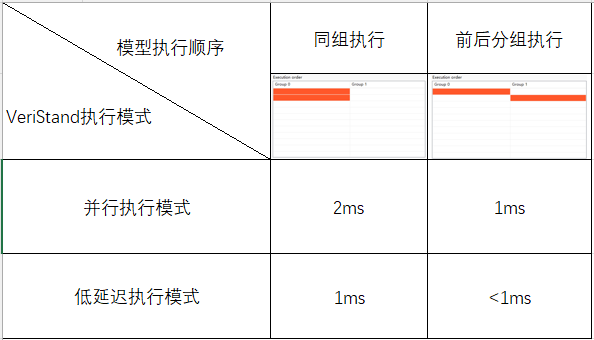

上圖統計了各設置下執行時AI 0到AO 0的實驗真實延遲,本次實驗的VeriStand目標頻率是1k,1ms等價于1個PCL周期,大家可以自己推導一下理論延遲做對比;兩設置排列組合下所有情況的延遲都符合理論預設的預期。

以上就是本次分享的所有內容啦,歡迎大家留言討論,交流分享!

-

硬件

+關注

關注

12文章

3606瀏覽量

69098 -

仿真測試

+關注

關注

0文章

115瀏覽量

11801 -

VeriStand

+關注

關注

8文章

13瀏覽量

22971

原文標題:VeriStand 執行機制

文章出處:【微信號:華穗科技,微信公眾號:華穗科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

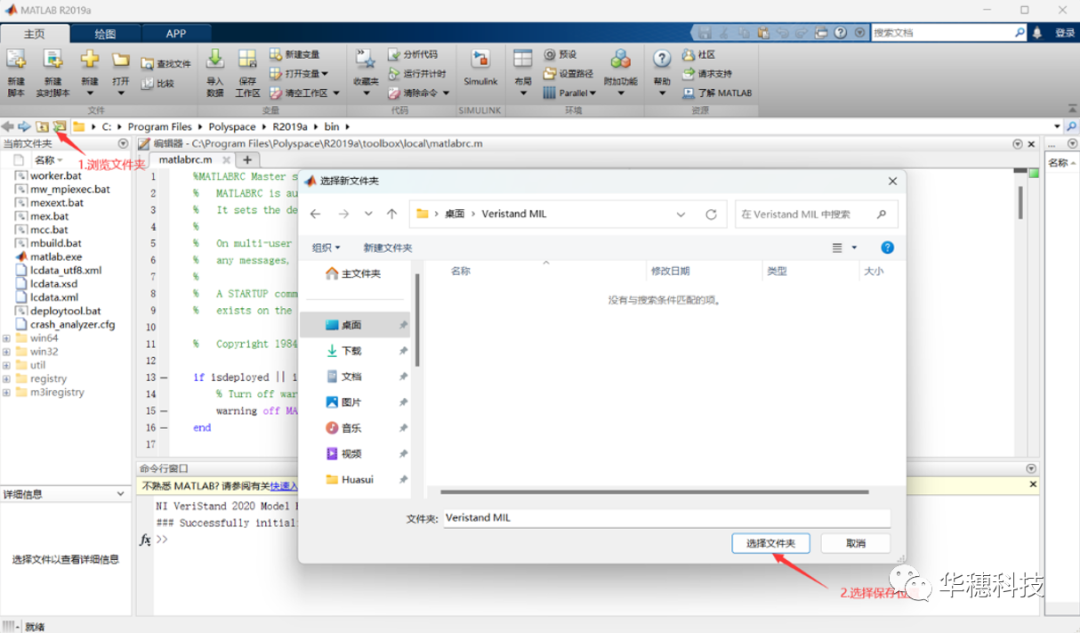

使用VeriStand搭建MIL測試環境

Simulink中的NI VeriStand Blocks在安裝完VeriStand后沒有自動出現,該怎么找到?

VeriStand 2014中Stimulus Profiles Editor的用法

NI VeriStand 2016 與matlab 2016 搭配的問題

matlab 2016a 與 NI VeriStand 2016 代碼生成問題

labview建立veristand模型

Veristand,創建導入labview模型

veristand訪問C模塊

利用NI VeriStand 2010特性創建分布式系統

labview與veristand無法建立連接

veristand入XML文件

最新NI VeriStand 2010適用于從高性能多機箱系

在NI VeriStand環境中進行FPGA相關配置

如何使用VeriStand的User Channels、Alarms、Procedures功能?

VeriStand的執行機制

VeriStand的執行機制

評論