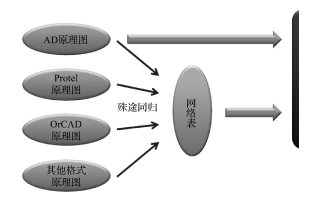

生成PCB網(wǎng)表是電路設計過程中的一個重要步驟,它將電路原理圖轉換為PCB布局所需的連接信息。AD(Altium Designer)軟件是一款流行的電子設計自動化(EDA)工具,它提供了從原理圖設計到PCB布局和制造的完整解決方案。以下是使用AD軟件生成PCB網(wǎng)表的步驟:

1. 準備工作

在開始之前,確保你已經(jīng)安裝了最新版本的Altium Designer,并熟悉基本的操作界面和功能。

2. 創(chuàng)建原理圖

- 啟動AD軟件 :打開Altium Designer。

- 新建原理圖 :在“File”菜單中選擇“New” -> “Schematic File”。

- 繪制原理圖 :使用原理圖編輯器工具欄中的組件和連線工具繪制電路原理圖。

3. 組件庫管理

- 添加組件庫 :在原理圖中,使用“Place”菜單下的“Component”功能添加所需的組件。

- 組件屬性設置 :雙擊組件,打開屬性窗口,設置組件的封裝類型等信息。

4. 原理圖檢查

5. 創(chuàng)建PCB項目

- 新建PCB項目 :在“File”菜單中選擇“New” -> “PCB Project”。

- 添加原理圖文件 :在PCB項目中添加之前創(chuàng)建的原理圖文件。

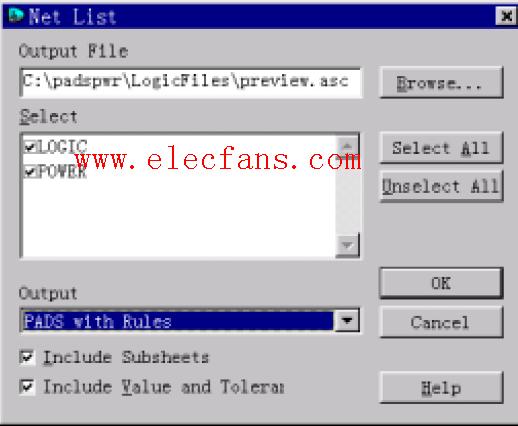

6. 生成網(wǎng)表

- 設置原理圖和PCB的鏈接 :在PCB項目中,確保原理圖文件與PCB文件正確鏈接。

- 生成網(wǎng)表 :在“Project”菜單中選擇“Schematic” -> “Update PCB Document”,AD軟件將自動生成網(wǎng)表。

7. 網(wǎng)表檢查

- 查看網(wǎng)表 :在“Project”菜單中選擇“Schematic” -> “View” -> “Netlist”。

- 檢查網(wǎng)表 :檢查生成的網(wǎng)表是否包含了所有必要的連接信息,確保沒有遺漏或錯誤。

8. 導入網(wǎng)表到PCB

- 打開PCB文件 :在PCB項目中打開PCB文件。

- 導入網(wǎng)表 :在PCB編輯器中,使用“Design”菜單下的“Import Changes from Schematic”功能導入網(wǎng)表。

9. PCB布局

- 布局組件 :根據(jù)網(wǎng)表和設計要求,手動或自動布局PCB板上的組件。

- 布線 :使用自動布線工具或手動布線,確保所有連接都正確無誤。

10. 設計驗證

- DRC檢查 :進行設計規(guī)則檢查,確保PCB設計符合制造要求。

- 3D視圖檢查 :使用3D視圖功能檢查組件的放置和布線是否合理。

11. 輸出制造文件

- 生成Gerber文件 :在“File”菜單中選擇“Fabrication Output” -> “Gerber Files”。

- 生成鉆孔文件 :生成鉆孔文件,用于PCB制造過程中的鉆孔操作。

12. 文檔和版本控制

- 保存項目 :定期保存項目文件,確保設計數(shù)據(jù)不會丟失。

- 版本控制 :使用版本控制系統(tǒng)管理設計文件,便于團隊協(xié)作和歷史記錄追蹤。

13. 總結

生成PCB網(wǎng)表是一個復雜的過程,涉及到多個步驟和細節(jié)。使用Altium Designer軟件,可以通過一系列工具和功能來自動化這個過程,提高設計效率和準確性。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

pcb

+關注

關注

4404文章

23877瀏覽量

424211 -

自動化

+關注

關注

31文章

5930瀏覽量

90215 -

電子設計

+關注

關注

42文章

1681瀏覽量

49848 -

AD軟件

+關注

關注

7文章

15瀏覽量

14777

發(fā)布評論請先 登錄

相關推薦

熱點推薦

PCB設計經(jīng)驗之Altium網(wǎng)表及Protel網(wǎng)表的生成

通過導入網(wǎng)絡連接關系進行PCB的導入。當今幾大主流PCB設計軟件都支持Altium Designer格式網(wǎng)表導出,這也極大地提高了Altiu

發(fā)表于 04-22 10:26

?2w次閱讀

急!!!orcad生成網(wǎng)表時無法正常退出

各位大俠,我在用orcad生成網(wǎng)表時,軟件無法正常退出,但其實網(wǎng)表文件已經(jīng)

發(fā)表于 12-18 11:14

用PADS生成網(wǎng)表時出現(xiàn)的問題

用PADS生成網(wǎng)表時出現(xiàn)的問題,求高手解答,謝謝。PCB Net List Errors Report - FIRST.sch - Sat Feb 11 19:51:39

發(fā)表于 02-11 20:08

生成網(wǎng)表時出錯,請高人指點

在生成網(wǎng)表時報Error,【ALG0030】Unable to read design "d:\PCB\test\test.dsn"為什么呢,請高手說明,謝謝

發(fā)表于 03-26 16:04

allegro第三方生成網(wǎng)表如何實現(xiàn)與allegro pcb交互設計

allegro第三方生成網(wǎng)表如何實現(xiàn)與allegro pcb交互設計

發(fā)表于 10-28 10:37

cadence allegro 16.5軟件生成網(wǎng)表時出現(xiàn)這些,求大神給予解答

cadence allegro 16.5軟件生成網(wǎng)表時出現(xiàn)這些,求大神給予解答

發(fā)表于 12-16 13:32

不能生成網(wǎng)表

oracd capture cis 生成網(wǎng)表時,我確定所有路徑都是沒問題的,而且也沒有非法字符,但是按了creat netlist的確定時,一直不出現(xiàn)這個窗口,也沒有生成任何bat文件

發(fā)表于 06-25 13:02

PCB設計軟件藍牙音箱實操│網(wǎng)表導出導入和封裝路徑設置

`PCB設計軟件allegro藍牙音箱案例實操講解,以藍牙音箱為案例將PCB設計基礎知識融進實際案例中,通過操作過程講解PCB設計軟件功能及

發(fā)表于 07-31 14:15

PCB設計│網(wǎng)表導入的雷區(qū),你還在踩?

PCB設計軟件allegro藍牙音箱案例實操講解,以藍牙音箱為案例將PCB設計基礎知識融進實際案例中,通過操作過程講解PCB設計軟件功能及實

發(fā)表于 08-06 11:05

orcad軟件怎么生成allegro網(wǎng)表、ad網(wǎng)表、pads網(wǎng)表?

以下界面,選擇PCB Editor,然后點擊確定,即可生成Allegro第一方網(wǎng)表,網(wǎng)表的形式會

發(fā)表于 11-05 15:04

Orcad軟件怎么生成導出allegro網(wǎng)表、ad網(wǎng)表、pads網(wǎng)表

1、 orcad軟件怎么生成allegro網(wǎng)表、ad網(wǎng)表、pads

發(fā)表于 08-26 17:46

為什么PCB板上沒有顯示Allegro軟件導入的網(wǎng)表?

很多剛開始接觸這個Allegro軟件的同學,就有這樣的疑問,我的原理圖的網(wǎng)表都已經(jīng)導入到PCB中了,為什么PCB板上什么都沒有呢?元器件

發(fā)表于 09-07 17:23

cadence16.6生成網(wǎng)表后原理圖與PCB不能正常交互,為何?

cadence16.6生成網(wǎng)表后原理圖與PCB不能交互,交互功能勾選了,原理圖改網(wǎng)絡重新生成網(wǎng)

發(fā)表于 09-09 17:10

powerlogic如何生成網(wǎng)表netlist

powerlogic如何生成網(wǎng)表netlist

為了建立網(wǎng)表(Netlist):1. 選擇工具/網(wǎng)

發(fā)表于 03-12 12:38

?2549次閱讀

AD軟件如何生成PCB網(wǎng)表

AD軟件如何生成PCB網(wǎng)表

評論